- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

CST TDR仿真不对,Allegro PCB,100欧差分线

但CST2013仿真结果明显不对,与理论值和实际测试结果都相差很大,分析了很久都没解决。

我感觉是仿真设置和Mesh 出了问题,但又不知道具体怎么设。请各位大牛指导。万分感谢!

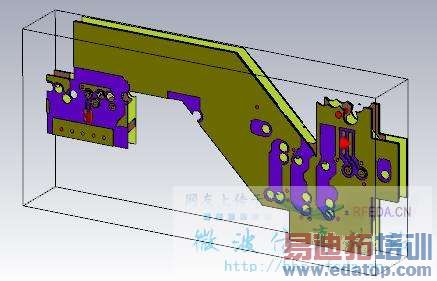

模型截图:

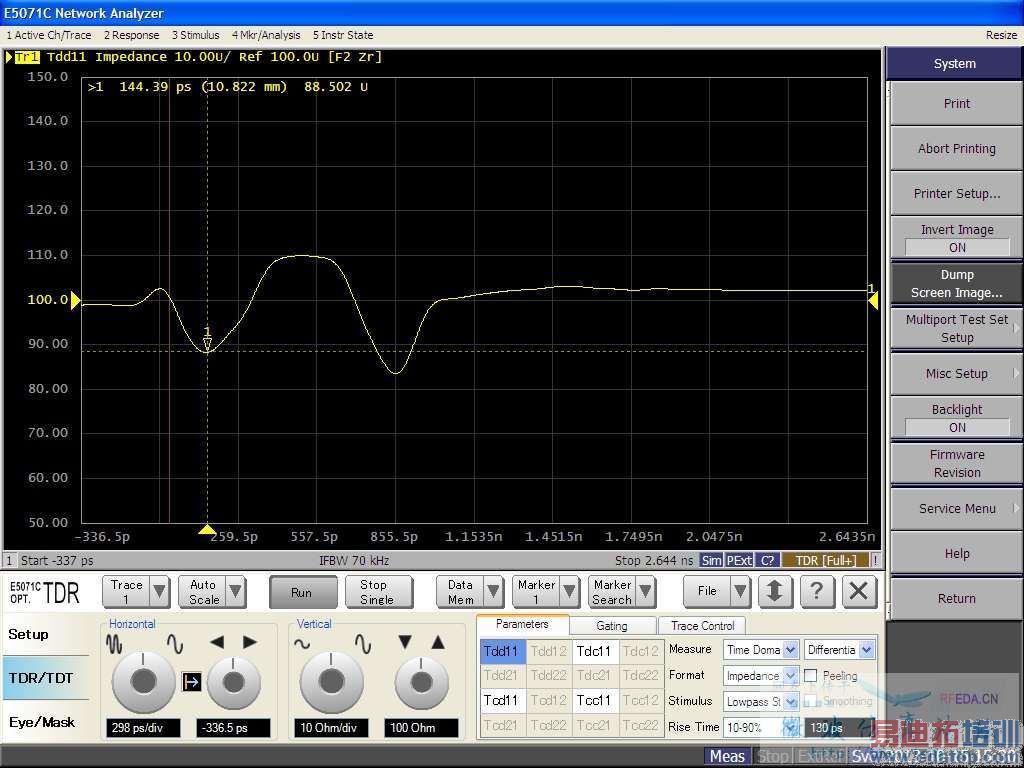

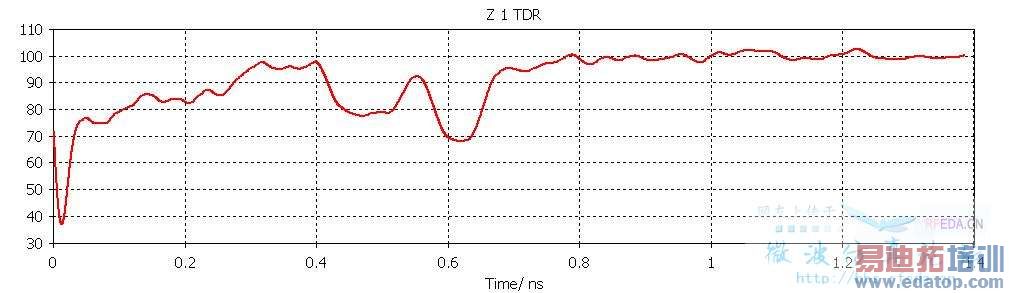

下面图片是用 Agilent TDR的实测波形, 压缩档是CST仿真文件

仿真文件 Archived from CST2013 19

网友回复:

第一个PART 怎么都下不了呢

网友回复:

我试了可以, 你再试一下,不行我就重新上传

网友回复:

無法讀取請問是用哪種模組??MWS嗎??

网友回复:

看了下你的CST文件,主要问题是频率范围,也可以说是脉冲长度的设置

我简单测量了一下两个端口之间的距离,大概957mil,也就是25mm左右,光速需要0.08ns从1端口传到2端口,而你的激励信号长度为0.09ns,明显不能分辨印制线上的不连续,建议将频率范围设置为0-100GHz试试

网友回复:

线长1625mil. 对应在FR4介质里的传播时间是 230ps 左右。

040G带宽也应该够,对应激励脉冲上升沿是21.9ps,已经很陡了。我试过20G带宽和50G带宽,只是影响结果的精度。

这对差分线跑的最高信号频率是2.5GHz。

我重新上传了仿真文件,大家再看看能否打开,谢谢!

网友回复:

问题还是没解决,改变MESH数量会生成完全不同的结果。所以现在我不清楚要怎么设置MESH才合适。有没有人可以帮忙设置一下正确参数,谢谢!

网友回复:

你的感觉是对的,mesh出了问题。

但这个完全没必要“分析很久”,CST作为一款成熟的商业软件,怎可能仿真结果如此离谱?

相信你仿真的过程中肯定看到此警告:mesh cells are represented in staircase mode and have been filled with PEC……

如果此时你看一眼你的网格,你会发现差分信号线都和GND短路了。

信号能传的过去才怪。

所以CST TDR仿真是没问题的,你还需要加密网格,特别是z向的

网友回复:

因為2013我開不了所以看不到 不過我有些建議 如果你先看TDR的話

CST 的excitstion signals 那使用smooth step 我從你的儀器上看到 使用的上升時間

應該是 10-90% 130PS 所以你可以設定 Arise 80% 130PS 這樣就跟你設定的頻率無關了

也會跟你的 儀器的上升時間一樣 基本上波形的大略圖會差不多 再來就是你mesh設定的差異

网友回复:

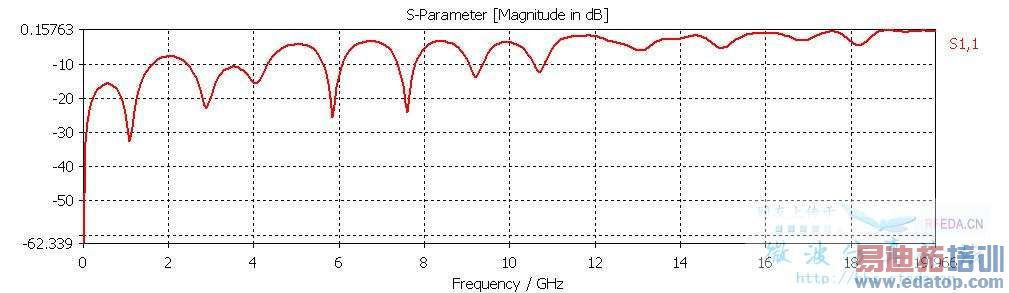

在各位大佬的建议下,我优化了mesh, 仿真结果如下:

结果看起来有点象样了。但有两点还不明白,

仿真图中TDR传播时间是0.65ns, 我用ads 自带的linecalc 输入PCB参数( Er=4.0, TanD=0.02, 层厚H=3.5mil, 线宽W=4mil, 线距S=10mil ) ,

得出 Ko=2.689, Zodd=59Ω,那么Zdiff = 118Ω;

问题1:为什么TDR 仿真出来的阻抗会小于118Ω?

问题2:根据Ko=2.689, 推算出差分线长是2340mil,与实际长度1625mil相差比较大,这个误差是怎么来的呢?

请大佬们继续建议,谢谢!

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习易迪拓培训专家讲授的CST视频培训教程。

上一篇:CST端口模式的问题

下一篇:用CST对平行电极板之间的电场进行仿真