# ECE 744 - Homework # 1 Spring 2001

# Due: Thursday February 8, 2001 11:20 AM. (On-Campus Only!)

You may turn in paper copy or e-mail your homework. It may be hand-written or in electronic format.

I highly encourage you to work in groups, but each person must turn in their own homework, expressed in their own words, own calculations, etc. There will be no blatant copying allowed. State All Assumptions! Show All Work for Partial Credit!!!

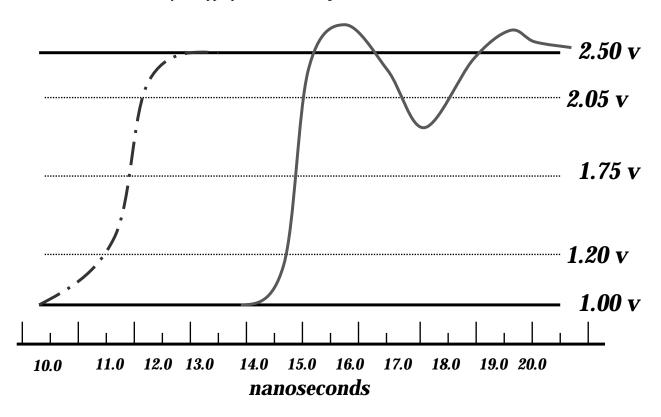

(1) For the following 2 Plots of a Signal, Identify the Various SI parameters... fill in the tables for each. Assume the thresholds are marked by the appropriate lines.... [5 pnts. Each]

$V_{il^-max} = 1.20V$ ,  $V_{ih^-min} = 2.05V$ ,  $V_{ref^-Driver} = 1.75 V$ ,  $V_{steady^-state-high} = 2.50 V$ ,  $V_{steady^-state-low} = 1.0V$

| Parameter  | Measurement | Parameter    | Measurement | Parameter     | Measurement |

|------------|-------------|--------------|-------------|---------------|-------------|

| Period T   |             | Noise Margin |             | Ringback      |             |

|            |             | High         |             | (Rising)      |             |

| Duty Cycle |             | Noise Margin |             | Ringback      |             |

|            |             | Low          |             | (Falling)     |             |

| High Time  |             | Overshoot    |             | Output Buffer |             |

|            |             | (Rising)     |             | Delay         |             |

| Low Time   |             | Overshoot    |             |               |             |

|            |             | (Falling)    |             |               |             |

| Frequency  |             | Monotonic    |             |               |             |

|            |             | Y/N ??       |             |               |             |

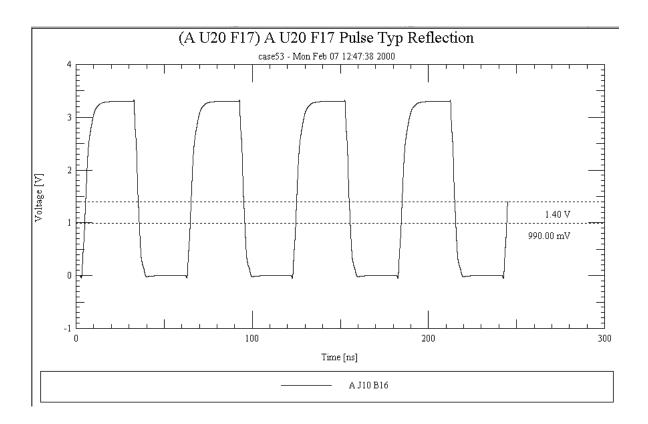

$V_{il^-max} = 0.7V, \quad V_{ih^-min} = 2.55V, \quad V_{ref^-Driver} = 1.75~V, \quad V_{steady^-state-high} = 3.30~V, \quad V_{steady^-state-low} = 0.0V$

| Parameter  | Measurement | Parameter              | Measurement | Parameter             | Measurement |

|------------|-------------|------------------------|-------------|-----------------------|-------------|

| Period T   |             | Noise Margin<br>High   |             | Ringback (Rising)     |             |

| Duty Cycle |             | Noise Margin<br>Low    |             | Ringback<br>(Falling) |             |

| High Time  |             | Overshoot<br>(Rising)  |             |                       |             |

| Low Time   |             | Overshoot<br>(Falling) |             |                       |             |

| Frequency  |             | Monotonic<br>Y/N ??    |             |                       |             |

- (2) For the following Rise / Fall Times, what are the highest frequencies of interest for our analyses? Assume the 3X Rule applies. What is the wavelength  $\lambda$  at this frequency? Assume  $\varepsilon r = 4.3$ . [6 pnts.]

- 900 psecs Rise Time

- 2.0 nsecs Rise Time

- 250 psecs Rise Time

- (3) For the following set of DC and AC Noise items, calculate the total noise based on each of the three formulas discussed in the lectures. Rank the calculated totals in order of magnitude. [4 pnts.] The values listed are in millivolts.

#### DC Noises

| Ohmic Drop               | 5  |

|--------------------------|----|

| Voltage Differential     | 11 |

| Temperature Differential | 7  |

#### **AC** Noises

| Ohmic Drop          | 20  |

|---------------------|-----|

| Reflection          | 200 |

| Crosstalk           | 139 |

| SSN                 | 277 |

| Power Supply Ripple | 15  |

| EMI (Incoming)      | 5   |

| Gate I/O Level      | 50  |

(4) (a) Given the following set of timings and interconnect lengths, determine the minimum cycle time.

Assume  $\mathcal{E}_r = 4.0$  Assume Actual Line Load = Standard Load Specification. Assume Common Clock Architecture. [4 pnts.]

Setup Time = 1000 psecs

Hold Time = 1 nsec

TCO - = 1 nsec

Interconnect Length = 35 inches

Settling Time = 1.4 nsecs

Clock Skew = 475 psecs

Clock Jitter = 75 psecs

ECE744 Spring 2001

(4b) Given the following set of timings and operational frequency, determine the minimum and maximum interconnect lengths for the system. Assume Common Clock Architecture. Assume Actual load = Standard

Load Specification. Assume  $\mathcal{E}_r = 4.5$  [4 pnts.] Do we satisfy hold time requirements?

Operation Frequency = 70MHz

Setup Time = 1.1nsecs

Hold Time = 1.1nsecs

Tco = 1.2 nsecs

Settling Time = 0 nsecs

Clock Skew = 500 psecs

Clock Jitter = 500 psecs

- (5) (a) On a PCB design, a CPU requires that a 1.5 volt trace is routed across the board from the regulator. This CPU draws 40 Amps from the regulator. This trace length is 4 inches, and the device can tolerate a maximum DC drop of 1.5% for the regulated voltage. For a 2 oz. Copper trace, how wide must the trace be to meet these specifications? How much energy is dissipated in the trace? [3 pnts.]

- (6) Calculate the size of a round wire, 100 feet long, which will connect to an ideal 8 ohm pure resistive load. This wire must carry a 40 volt signal and the voltage at the end must be within 5% of the source. How much energy is dissipated in this wire? [4 pnts.]

- (7) (a) A PCB is 10 inches by 11 inches square. The Vcc and GND planes are 2.5 mils apart, with FR-4 material as the dielectric. Calculate the total capacitance provided by these two planes. State your assumptions. [4 pnts.]

- (7b) How close would the same planes need to be to produce a capacitance of 1 uF?? What dielectric would be needed to produce this type of board? State your assumptions and reasoning. [4 pnts.]

ECE744 Spring 2001

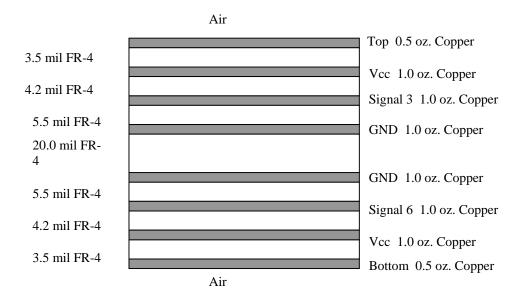

(8) Fill in the blanks for the following parameters. Show all work. Use the equations from the class notes, show which equation you chose to use for each application. [ 16 pnts.]

Assume straight, lossless lines w/o distributed loadings, Assume  $\gg_r = 4.3$

This PCB is a 4s4p (4 Signal, 4 Power) stackup, as shown.

| Item | Layer  | Width   | Length | Co      | R <sub>o</sub> | $L_{o}$ | Z <sub>o</sub> ohms | C <sub>total</sub> | R <sub>total</sub> |

|------|--------|---------|--------|---------|----------------|---------|---------------------|--------------------|--------------------|

|      |        |         |        | pf/inch | mohms/inch     | nH/inch |                     | pF                 | ohms               |

| Wire | Top    | 4 mils  | 12 "   |         |                | N/A     |                     |                    |                    |

| Wire | Top    | 12 mils | N/A    |         |                | N/A     |                     |                    |                    |

| Wire | S3     | 5 mils  | N/A    |         |                |         |                     |                    |                    |

| Wire | S3     | 14 mils | N/A    |         |                |         |                     |                    |                    |

| Wire | S6     | 10 mils | 6"     |         |                |         |                     |                    |                    |

| Wire | Bottom | 5 mils  | 16"    |         |                | N/A     |                     |                    |                    |

What is the total board thickness  $\underline{?}$

- (9) Repeat Example 5.3.2 from the textbook (Poon), but make the wave a **FALLING EDGE**. Use your choice of SPICE simulator, producing a plot similar to that of Figure 5.7. Discuss **briefly** why the number of segments used in the simulation effect the shape and accuracy of the waveform. Please submit your circuit and stimulus files as well as the plots of the results. **[ 17 pnts.]**

- (10) What is the skin effect depth and  $R_{skin}$  of the following wires at the specified rise times (frequency of interest): [8 pnts.]

| Wire # | Material | $T_{r}$  | Skin Depth | Trace                   | $\mathbf{R}_{\mathrm{skin}}$ |

|--------|----------|----------|------------|-------------------------|------------------------------|

|        |          |          | cm         | Width                   | Ohms/cm                      |

|        |          |          |            | cm                      |                              |

| 1      | Copper   | 2 usec   |            | 1.28 x 10 <sup>-2</sup> |                              |

| 2      | Copper   | 300 psec |            | $2.00 \times 10^{-2}$   |                              |

| 3      | Tungsten | 3 usec   |            | $0.75 \times 10^{-2}$   |                              |

| 4      | Tungsten | 300 nsec |            | 1.00 x 10 <sup>-2</sup> |                              |

| 5      | Aluminum | 3 nsec   |            | $0.75 \times 10^{-2}$   |                              |

| 6      | Aluminum | 600 psec |            | $0.75 \times 10^{-2}$   |                              |

| 7      | Gold     | 1 nsec   |            | 1.28 x 10 <sup>-2</sup> |                              |

| 8      | Gold     | 500 psec |            | 1.28 x 10 <sup>-2</sup> |                              |

(11)(a) For the 4s2p stackup shown in problem number (8), determine the wire size and spacing required to produce a differential pair with an individual impedance of 70 ohms, and a differential impedance of 120 ohms. Assume that the wires are routed only on the TOP layer. [6 pnts.] State all other assumptions.

(12) The specifications for the USB (Universal Serial Bus) differential pair wiring require an individual impedance of 50 ohms, with a differential impedance of 100 ohms. How can this be? Is this possible? What are they really trying to tell us here? What is the wire size and spacing required to meet this specification on the same PCB as in problem (8)? Assume the routing is on the BOTTOM layer only. State all assumptions required to solve this problem. [4 pnts.]

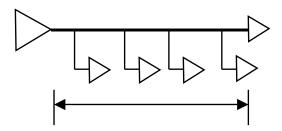

(13) For the following Driver / Receiver circuit, calculate the effects of adding 7 additional (total of 8) loads, equally spaced, with a capacitive load of 6 pF each. Assume that the chip inputs are on the transmission line (no stubs). Calculate BOTH the new  $Z_o$  and  $T_o$  values for this circuit. Length = 10 inches! [6 pnts.]

$C_o = 1.0 \ pf/inch$ ,  $Z_o = 65 \ ohms$ ,  $T_o = 175 \ ps/inch$ .

ECE744 Spring 2001

## 射频和天线设计培训课程推荐

易迪拓培训(www.edatop.com)由数名来自于研发第一线的资深工程师发起成立,致力并专注于微波、射频、天线设计研发人才的培养;我们于2006年整合合并微波EDA网(www.mweda.com),现已发展成为国内最大的微波射频和天线设计人才培养基地,成功推出多套微波射频以及天线设计经典培训课程和ADS、HFSS等专业软件使用培训课程,广受客户好评;并先后与人民邮电出版社、电子工业出版社合作出版了多本专业图书,帮助数万名工程师提升了专业技术能力。客户遍布中兴通讯、研通高频、埃威航电、国人通信等多家国内知名公司,以及台湾工业技术研究院、永业科技、全一电子等多家台湾地区企业。

易迪拓培训课程列表: http://www.edatop.com/peixun/rfe/129.html

#### 射频工程师养成培训课程套装

该套装精选了射频专业基础培训课程、射频仿真设计培训课程和射频电路测量培训课程三个类别共 30 门视频培训课程和 3 本图书教材;旨在引领学员全面学习一个射频工程师需要熟悉、理解和掌握的专业知识和研发设计能力。通过套装的学习,能够让学员完全达到和胜任一个合格的射频工程师的要求…

课程网址: http://www.edatop.com/peixun/rfe/110.html

#### ADS 学习培训课程套装

该套装是迄今国内最全面、最权威的 ADS 培训教程, 共包含 10 门 ADS 学习培训课程。课程是由具有多年 ADS 使用经验的微波射频与通信系统设计领域资深专家讲解,并多结合设计实例,由浅入深、详细而又全面地讲解了 ADS 在微波射频电路设计、通信系统设计和电磁仿真设计方面的内容。能让您在最短的时间内学会使用 ADS, 迅速提升个人技术能力,把 ADS 真正应用到实际研发工作中去,成为 ADS 设计专家...

课程网址: http://www.edatop.com/peixun/ads/13.html

#### HFSS 学习培训课程套装

该套课程套装包含了本站全部 HFSS 培训课程,是迄今国内最全面、最专业的 HFSS培训教程套装,可以帮助您从零开始,全面深入学习 HFSS的各项功能和在多个方面的工程应用。购买套装,更可超值赠送 3 个月免费学习答疑,随时解答您学习过程中遇到的棘手问题,让您的 HFSS学习更加轻松顺畅···

课程网址: http://www.edatop.com/peixun/hfss/11.html

#### CST 学习培训课程套装

该培训套装由易迪拓培训联合微波 EDA 网共同推出,是最全面、系统、 专业的 CST 微波工作室培训课程套装, 所有课程都由经验丰富的专家授 课,视频教学,可以帮助您从零开始,全面系统地学习 CST 微波工作的 各项功能及其在微波射频、天线设计等领域的设计应用。且购买该套装, 还可超值赠送3个月免费学习答疑…

#### HFSS 天线设计培训课程套装

套装包含6门视频课程和1本图书,课程从基础讲起,内容由浅入深, 理论介绍和实际操作讲解相结合,全面系统的讲解了 HFSS 天线设计的 全过程。是国内最全面、最专业的 HFSS 天线设计课程,可以帮助您快 速学习掌握如何使用 HFSS 设计天线, 让天线设计不再难…

课程网址: http://www.edatop.com/peixun/hfss/122.html

### 13.56MHz NFC/RFID 线圈天线设计培训课程套装

套装包含 4 门视频培训课程,培训将 13.56MHz 线圈天线设计原理和仿 真设计实践相结合,全面系统地讲解了13.56MHz线圈天线的工作原理、 设计方法、设计考量以及使用 HFSS 和 CST 仿真分析线圈天线的具体 操作,同时还介绍了 13.56MHz 线圈天线匹配电路的设计和调试。通过 该套课程的学习,可以帮助您快速学习掌握 13.56MHz 线圈天线及其匹 配电路的原理、设计和调试…

详情浏览: http://www.edatop.com/peixun/antenna/116.html

#### 我们的课程优势:

- ※ 成立于 2004年, 10 多年丰富的行业经验,

- ※ 一直致力并专注于微波射频和天线设计工程师的培养,更了解该行业对人才的要求

- ※ 经验丰富的一线资深工程师讲授,结合实际工程案例,直观、实用、易学

#### 联系我们:

- ※ 易迪拓培训官网: http://www.edatop.com

- ※ 微波 EDA 网: http://www.mweda.com

- ※ 官方淘宝店: http://shop36920890.taobao.com

易迪拓信训 官方网址: http://www.edatop.com