# PCB 制造工艺综述

## 目 录

|                            |    |

|----------------------------|----|

| 一、 PCB 制造行业术语 .....        | 2  |

| 二、 PCB 制造工艺综述 .....        | 4  |

| 1. 印制板制造技术发展 50 年的历程 ..... | 4  |

| 2. 初步认识 PCB .....          | 5  |

| 3. 表面贴装技术(SMT)的介绍 .....    | 7  |

| 4. PCB 电镀金工艺介绍 .....       | 8  |

| 5. PCB 电镀铜工艺介绍 .....       | 8  |

| 6. 多层板孔金属化工艺 .....         | 9  |

| 7. PCB 表面处理技术 .....        | 9  |

| 三、 印制板产品的 DFM .....        | 12 |

| 1、 DFM 的开始 .....           | 12 |

| 2、 工具和技术 .....             | 13 |

## 一、PCB 制造行业术语

### 1. Test Coupon: 试样

test coupon 是用来以 TDR (Time Domain Reflectometer) 测量所生产的 PCB 板的特性阻抗是否满足设计需求。一般要控制的阻抗有单根线和差分对两种情况。所以, test coupon 上的走线线宽和线距(有差分对时)要与所要控制的线一样。最重要的是测量时接地点的位置。为了减少接地引线(ground lead)的电感值, TDR 探棒(probe)接地的地方通常非常接近量信号的地方(probe tip)。所以, test coupon 上量测信号的点跟接地点的距离和方式要符合所用的探棒。

### 2. 金手指

在线路板板边节点镀金 (Edge-Connction) , 也就是我们经常说的金手指(Gold Finger), 是用来与连接器(Connector)弹片之间的连接, 进行压迫接触而导电互连。这是由于黄金永远不会生锈, 且电镀加工有非常的容易, 外观也好看, 故电子工业的接点表面几乎都要选择黄金。

线路板金手指上的金的硬度在 140 Knoop 以上, 以便卡插拔时确保耐磨得效果, 故一向采用镀硬金的工艺。其镀金的厚度平均为在 30u in。

但在封装载板上(Substrate)上设有若干镀金的承垫, 用来 COB (chip on board) 晶片间, 以"打金线" (wire bond 是一种热压式熔接) 的办法互连, 故另需使用较软的金层与金线融合, 一般金的硬度在 100 Knoop 以下, 称为软金, 其品质要求较硬金更为严格。此外, 镀金层具有焊锡性与导热性, 故也常用于焊点与散热表面的用途。

### 3. 硬金, 软金

硬金:Hard Gold;软金 soft Gold。电镀软金是以电镀的方式析出镍金在电路板上, 它的厚度控制较具弹性, 一般适合用于 IC 封装板打线用, 金手指或其它适配卡。内存所用的电镀金多数为硬金, 因为必须耐磨, 在化学金方面, 基本上有所谓的浸金和化学金两种, 浸金指的是以置换的方式将金析出于镍表面, 因为是置换方式其厚度相当薄且无法继续成长, 但是化学金是采用氧化还原剂的方式将金还原在镍面上, 并非置换, 因此它的厚度可以成长较厚, 一般这类的做法是用于无法拉出导线的电路板, 因为化学金在整体的稳定度上控制较难, 因此较容易产生品质问题, 一般此类应用多集中在焊接方面, 打线方面的应用很少。

### 4. SMT 基本名词术语解释

- Additive Process(加成工艺): 一种制造 PCB 导电布线的方法, 通过选择性的在板层上沉淀导电材料(铜、锡等)。

- Angle of attack(迎角): 丝印刮板面与丝印平面之间的夹角。

- Anisotropic adhesive(各异性胶): 一种导电性物质, 其粒子只在 Z 轴方向通过电流。

- Application specific integrated circuit (ASIC 特殊应用集成电路): 客户定做的用于专门用途的电路。

- Artwork(布线图): PCB 的导电布线图, 用来产生照片原版, 可以任何比例制作, 但一般为 3:1 或 4:1。

- Automated test equipment (ATE 自动测试设备): 为了评估性能等级, 设计用于自动分析功能或静态参数的设备, 也用于故障离析。

- Blind via(盲通路孔): PCB 的外层与内层之间的导电连接, 不继续通到板的另一面。

- Buried via(埋入的通路孔): PCB 的两个或多个内层之间的导电连接(即, 从外层看不见的)。

- Bonding agent(粘合剂): 将单层粘合形成多层板的胶剂。

- **Bridge(锡桥):** 把两个应该导电连接的导体连接起来的焊锡, 引起短路。

- **Circuit tester(电路测试机):** 一种在批量生产时测试 PCB 的方法。包括: 针床、元件引脚脚印、导向探针、内部连线、装载板、空板、和元件测试。

- **Cladding(覆盖层):** 一个金属箔的薄层粘合在板层上形成 PCB 导电布线。

- **CTE---Coefficient of the thermal expansion(温度膨胀系数):** 当材料的表面温度增加时, 测量到的每度温度材料膨胀百万分率(ppm)。

- **Cold cleaning(冷清洗):** 一种有机溶解过程, 液体接触完成焊接后的残渣清除。

- **Component density(元件密度):** PCB 上的元件数量除以板的面积。

- **Conductive epoxy(导电性环氧树脂):** 一种聚合材料, 通过加入金属粒子, 通常是银, 使其通过电流。

- **Copper foil(铜箔):** 一种阴性质电解材料, 沉淀于电路板基底层上的一层薄的、连续的金属箔, 它作为 PCB 的导电体。它容易粘合于绝缘层, 接受印刷保护层, 腐蚀后形成电路图样。

- **Copper mirror test(铜镜测试):** 一种助焊剂腐蚀性测试, 在玻璃板上使用一种真空沉淀薄膜。

- **Defect(缺陷):** 元件或电路单元偏离了正常接受的特征。

- **Delamination(分层):** 板层的分离和板层与导电覆盖层之间的分离。

- **Desoldering(卸焊):** 把焊接元件拆卸来修理或更换, 方法包括: 用吸锡带吸锡、真空(焊锡吸管)和热拔。

- **DFM(为制造着想的设计):** 以最有效的方式生产产品的方法, 将时间、成本和可用资源考虑在内。

- **Environmental test(环境测试):** 一个或一系列的测试, 用于决定外部对于给定的元件包装或装配的结构、机械和功能完整性的总影响。

- **Functional test(功能测试):** 模拟其预期的操作环境, 对整个装配的电器测试。

- **Fiducial(基准点):** 和电路布线图合成一体的专用标记, 用于机器视觉, 以找出布线图的方向和位置。

- **Fine-pitch technology (FPT 密脚距技术):** 表面贴片元件包装的引脚中心间隔距离为 0.025" (0.635mm) 或更少。

- **Fixture (夹具):** 连接 PCB 到处理机器中心的装置。

- **Lead configuration(引脚外形):** 从元件延伸出的导体, 起机械与电气两种连接点的作用。

- **Machine vision(机器视觉):** 一个或多个相机, 用来帮助找元件中心或提高系统的元件贴装精度。

- **Mean time between failure (MTBF 平均故障间隔时间):** 预料可能的运转单元失效的平均统计时间间隔, 通常以每小时计算, 结果应该表明实际的、预计的或计算的。

- **Photo-plotter(相片绘图仪):** 基本的布线图处理设备, 用于在照相底片上生产原版 PCB 布线图(通常为实际尺寸)。

- **Pick-and-place(拾取-贴装设备):** 一种可编程机器, 有一个机械手臂, 从自动供料器拾取元件, 移动到 PCB 上的一个定点, 以正确的方向贴放于正确的位置。

- **Placement equipment(贴装设备):** 结合高速和准确定位地将元件贴放于 PCB 的机器, 分为三种类型: SMD 的大量转移、X/Y 定位和在线转移系统, 可以组合以便元件适应电路板设计。

- **Reflow soldering(回流焊接):** 通过各个阶段, 包括: 预热、稳定/干燥、回流峰值和冷却, 把表面贴装元件放入锡膏中以达到永久连接的工艺过程。

- **Schematic(原理图):** 使用符号代表电路布置的图, 包括电气连接、元件和功能。

- **Solder bump(焊锡球):** 球状的焊锡材料粘合在无源或有源元件的接触区, 起到与电路焊盘连接的作用。

- **Soldermask(阻焊):** 印刷电路板的处理技术, 除了要焊接的连接点之外的所有表面由塑料涂层覆盖住。

- Type I, II, III assembly(第一、二、三类装配): 板的一面或两面有表面贴装元件的 PCB(I); 有引脚元件安装在正面、有 SMD 元件贴装在一面或两面的混合技术(II); 以无源 SMD 元件安装在第二面、引脚(通孔)元件安装在正面为特征的混合技术(III)。

- Ultra-fine-pitch(超密脚距): 引脚的中心对中心距离和导体间距为 0.010" (0.25mm) 或更小。

- Void(空隙): 锡点内部的空穴, 在回流时气体释放或固化前夹住的助焊剂残留所形成。

- Yield(产出率): 制造过程结束时使用的元件和提交生产的元件数量比率。

5. Keying Slot : 在线路板金手指区, 为了防止插错而开的槽。

6. Mounting Hole : 安装孔, 此词有两种意思, 一是指分布在板脚的较大的孔, 是将组装后的线路板固定在终端设备上使用的螺丝孔, 其二是指插孔焊接零件的脚孔。后者也称 Insertion Hole, Lead Hole。

7. Laminate : 基材, 指用来制造线路板用的基材板, 也叫覆铜板 CCL ( Copper per Clad Laminates)。

8. Prepreg : 树脂片, 也称为半固化片。

9. Silk Screen : 网板印刷, 用聚酯网布或不锈钢网布当载体, 将正负片的图案以直接乳胶或间接版膜方式转移到网框的网布上形成的网版, 作为对线路板印刷的工具。

10. Screen Printing : 网版印刷, 是指在已有图案的网布上, 用刮刀刮挤压出油墨, 将要转移地图案转移到板面上, 也叫“丝网印刷”。

11. Screen ability : 网印能力, 指网版印刷加工时, 其油墨在刮压之作用下具有透过网布之露空部分, 而顺利漏到板上的能力。

12. Solder Bump : 铜锡凸块, 为了与线路板的连接, 在晶片的连接点处须做上各种形状的微“铜锡凸块”。

13. Subtractive Process : 减成法, 是指将基材上部分无用的铜箔减除掉, 而达成线路板的做法称为“减成法”。

14. Surface-Mount Device(SMD) : 表面装配零件, 不管是具有引脚, 或封装是否完整的各式零件, 凡能够利用锡膏做为焊料, 而能在板面焊垫上完成焊接组装者皆称为 SMD。

15. Surface Mount Technology : 表面装配技术, 是利用板面焊垫进行焊接或结合的组装技术, 有别于采用通孔插焊的传统的组装方式, 称为 SMT。

16. Thin Core : 薄基材, 多层板的内层是由薄基材制作。

17. Through Hole Mounting : 通孔插装, 是指早期线路板上各零件之组装, 皆采用引脚插孔及填锡方式进行, 以完成线路板上的互连。

18. Twist: 板翘, 指板面从对角线两侧的角落发生变形翘起, 称为板翘。其测量的方法是将板的三个角落紧合面, 再测量翘起的角的高度。

## 二、PCB 制造工艺综述

### 1. 印制板制造技术发展 50 年的历程

PCB 制造技术发展的 50 年历程可划分为 6 个时期:

- 1) PWB 诞生期: 1936 年~ (制造方法: 加成法)

绝缘板表面添加导电性材料形成导体图形，称为“加成法工艺”。使用这类生产专利的印制板曾在 1936 年底时应用于无线电接收机中。

2) PWB 试产期: 1950 年~ (制造方法: 减成法)

制造方法是使用覆铜箔纸基酚醛树脂层压板 (PP 基材)，用化学药品溶解除去不需要的铜箔，留下的铜箔成为电路，称为“减成法工艺”。在一些标牌制造工厂内用此工艺试做 PWB，以手工操作为主，腐蚀液是三氯化铁，溅上衣服就会变黄。当时应用 PWB 的代表性产品是索尼制造的手提式晶体管收音机，应和 PP 基材的单面 PWB。

3) PWB 实用期: 1960 年~ (新材料: GE 基材登场)

PWB 应用覆铜箔玻璃布环氧树脂层压板 (GE 基材)。由于 PWB 的国产 GE 基板在初期有加热翘曲变形、铜箔剥离等问题，材料制造商逐渐改进而提高，1965 年起日本有好几家材料制造商开始批量生产 GE 基板，工业用电子设备用 GE 基板，民用电子设备用 PP 基板，已成为常识。

4) PWB 跌进期: 1970~ (MLB 登场，新安装方式登场)

这个时期的 PWB 从 4 层向 6、8、10、20、40、50 层…，更多层发展，同时实行高密度化 (细线、小孔、薄板化)，线路宽度与间距从 0.5mm 向 0.35、0.2、0.1mm 发展，PWB 单位面积上布线密度大幅提高。

PWB 上元件安装方式开始了革命性变化，原来的插入式安装技术 (TMT) 改变为表面安装技术 (SMT)。引线插入式安装方法在 PWB 上应用有 20 年以上了，并都依靠手工操作的，这时也开发出自动元件插入机，实现自动装配线。SMT 更是采用自动装配线，并实现 PWB 两面贴装元件。

5) MLB 跃进期: 1980 年~ (超高密度安装的设备登场)

在 1982 年~1991 年的 10 年间，日本 PWB 产值约增长 3 倍 (1982 年产值 3615 亿日元，1991 年 10940 亿日元)。MLB 的产值 1986 年时 1468 亿日元，追上单面板产值；到 1989 年时 2784 亿日元，接近双面板产值，以后就 MLB 占主要地位了。

1980 年后 PCB 高密度化明显提高，有生产 62 层玻璃陶瓷基 MLB，MLB 高密度化推动移动电话和计算机开发竞争。

6) 迈向 21 世纪的助跑期: 1990 年~ (积层法 MLB 登场)

1991 年后日本泡沫经济破灭，电子设备和 PWB 受影响下降，到 1994 年后才开始恢复，MLB 和挠性板有大增长，而单面板与双面板产量却开始一直下跌。1998 年起积层法 MLB 进入实用期，产量急速增加，IC 元件封装形式进入面阵列端接型的 BGA 和 CSP，走向小型化、超高密度化安装。

今后的展望: 50 多年来 PWB 发展变化巨大。自 1947 的发明半导体晶体管以来，电子设备的形态发生大变样，半导体由 IC、ISI、VLSI、…向高集成度发展，开发出了 MCM、BGA、CSP 等更高集成化的 IC。21 世纪初期的技术趋向就是为设备的高密度化、小型化和轻量化努力，主导 21 世纪的创新技术将是“纳米技术”，会带动电子元件的研究开发。

## 2. 初步认识 PCB

PCB 是英文 (Printed Circuit Board) 印制线路板的简称。通常把在绝缘材上，按预定设计，制成印制线路、印制元件或两者组合而成的导电图形称为印制电路。而在绝缘基材上提供元器件之间电气连接的导电图形，称为印制线路。这样就把印制电路或印制线路的成品板称为印制线路板，亦称为印制板或印制电路板。

PCB 几乎我们能见到的电子设备都离不开它，小到电子手表、计算器、通用电脑，大到计算机、通迅电子设备、军用武器系统，只要有集成电路等电子元器件，它们之间电气互连都要用到 PCB。它提供集成电路等各种电子元器件固定装配的机械支撑、实现集成电路等各种电子元器件之间的布线和电气连接或电

绝缘、提供所要求的电气特性，如特性阻抗等。同时为自动锡焊提供阻焊图形；为元器件插装、检查、维修提供识别字符和图形。

PCB 是如何制造出来的呢？我们打开通用电脑的键盘就能看到一张软性薄膜（挠性的绝缘基材），印上有银白色（银浆）的导电图形与健位图形。因为通用丝网漏印方法得到这种图形，所以我们称这种印制线路板为挠性银浆印制线路板。而我们去电脑城看到的各种电脑主机板、显卡、网卡、调制解调器、声卡及家用电器上的印制电路板就不同了。它所用的基材是由纸基（常用于单面）或玻璃布基（常用于双面及多层），预浸酚醛或环氧树脂，表层一面或两面粘上覆铜簿再层压固化而成。这种线路板覆铜簿板材，我们就称它为刚性板。再制成印制线路板，我们就称它为刚性印制线路板。单面有印制线路图形我们称单面印制线路板，双面有印制线路图形，再通过孔的金属化进行双面互连形成的印制线路板，我们就称其为双面板。如果用一块双面作内层、二块单面作外层或二块双面作内层、二块单面作外层的印制线路板，通过定位系统及绝缘粘结材料交替在一起且导电图形按设计要求进行互连的印制线路板就成为四层、六层印制电路板了，也称为多层印制线路板。现在已有超过 100 层的实用印制线路板了。

为进一步认识 PCB 我们有必要了解一下单面、双面印制线路板及普通多层板的制作工艺，加深对它的了解。

单面刚性印制板：→单面覆铜板→下料→刷洗、干燥→网印线路抗蚀刻图形→固化检查修板→蚀刻铜→去抗蚀印料、干燥→钻网印及冲压定位孔→刷洗、干燥→网印阻焊图形（常用绿油）、UV 固化→网印字符标记图形、UV 固化→预热、冲孔及外形→电气开、短路测试→刷洗、干燥→预涂助焊防氧化剂（干燥）→检验包装→成品出厂。

双面刚性印制板：→双面覆铜板→下料→钻基准孔→数控钻导通孔→检验、去毛刺刷洗→化学镀（导通孔金属化）→（全板电镀薄铜）→检验刷洗→网印负性电路图形、固化（干膜或湿膜、曝光、显影）→检验、修板→线路图形电镀→电镀锡（抗蚀镍/金）→去印料（感光膜）→蚀刻铜→（退锡）→清洁刷洗→网印阻焊图形常用热固化绿油（贴感光干膜或湿膜、曝光、显影、热固化，常用感光热固化绿油）→清洗、干燥→网印标记字符图形、固化→外形加工→清洗、干燥→电气通断检测→（喷锡或有机保焊膜）→检验包装→成品出厂。

贯通孔金属化法制造多层板工艺流程：→内层覆铜板双面开料→刷洗→钻定位孔→贴光致抗蚀干膜或涂覆光致抗蚀剂→曝光→显影→蚀刻与去膜→内层粗化、去氧化→内层检查→（外层单面覆铜板线路制作、B—阶粘结片、板材粘结片检查、钻定位孔）→层压→数控制钻孔→孔检查→孔前处理与化学镀铜→全板镀薄铜→镀层检查→贴光致耐电镀干膜或涂覆光致耐电镀剂→面层底板曝光→显影、修板→线路图形电镀→电镀锡铅合金或镍/金镀→去膜与蚀刻→检查→网印阻焊图形或光致阻焊图形→印制字符图形→（热风平整或有机保焊膜）→数控洗外形→成品检查→包装出厂。

从工艺流程图可以看出多层板工艺是从双面孔金属化工艺基础上发展起来的。它除了继了双面工艺外，还有几个独特内容：金属化孔内层互连、钻孔与去环氧钻污、定位系统、层压、专用材料。

我们常见的电脑板卡基本上是环氧树脂玻璃布基双面印制线路板，其中有一面是插装元件另一面为元件脚焊接面，能看出焊点很有规则，这些焊点的元件脚分立焊接面我们就叫它为焊盘。为什么其它铜导线图形不上锡呢。因为除了需要锡焊的焊盘等部分外，其余部分的表面有一层耐波峰焊的阻焊膜。其表面阻焊膜多数为绿色，有少数采用黄色、黑色、蓝色等，所以在 PCB 行业常把阻焊油叫成绿油。其作用是，防

止波焊时产生桥接现象，提高焊接质量和节约焊料等作用。它也是印制板的永久性保护层，能起到防潮、防腐蚀、防霉和机械擦伤等作用。从外观看，表面光滑明亮的绿色阻焊膜，为菲林对板感光热固化绿油。不但外观比较好看，便重要的是其焊盘精确度较高，从而提高了焊点的可靠性。相反网印阻焊油就比较差。

我们从电脑板卡可以看出，元件的安装有三种方式。一种为传动的插入式安装工艺，将电子元件插入印制线路板的导通孔里。这样就容易看出双面印制线路板的导通孔有如下几种：一是单纯的元件插装孔；二是元件插装与双面互连导通孔；三是单纯的双面导通孔；四是基板安装与定位孔。另二种安装方式就是表面安装与芯片直接安装。其实芯片直接安装技术可以认为是表面安装技术的分支，它是将芯片直接粘在印制板上，再用线焊法或载带法、倒装法、梁式引线法等封装技术互联到印制板上。其焊接面就在元件面上。

表面安装技术有如下优点：

- 1) 由于印制板大量消除了大导通孔或埋孔互联技术，提高了印制板上的布线密度，减少了印制板面积（一般为插入式安装的三分阶之一），同时还可降低印制板的设计层数与成本。

- 2) 减轻了重量，提高了抗震性能，采用了胶状焊料及新的焊接技术，提高了产品质量和可靠性。

- 3) 由于布线密度提高和引线长度缩短，减少了寄生电容和寄生电感，更有利于提高印制板的电参数。

- 4) 比插装式安装更容易实现自动化，提高安装速度与劳动生产率，相应降低了组装成本。

从以上的表面安技术就可以看出，线路板技术的提高是隋芯片的封装技术与表面安装技术的提高而提高。现在我们看的电脑板卡其表面粘装率都不断地在上升。实际上这种的线路板再用传动的网印线路图形是无法满足技术要求的了。所以普通高精确度线路板，其线路图形及阻焊图形基本上采用感光线路与感光绿油制作工艺。也许过不多久人们该把印制线路板叫作感光线路板了。

现在我们再来看成组芯片直接安装技术，多芯片模块（MCM）技术，它是“将多块未封装的集成电路芯片高密度安装在同一基板上构成一个完整的部件”的新思路，即现在人们普遍称之为多芯片模块，简称MCM是（Multi Chip Module的缩写）。随着MCM的兴起，使封装的概念发生了本质的变化，在80年代以前，所有的封装都是面向器件的，而MCM可以说是面向部件的或者说是面向系统或整机的。MCM技术集先进印刷线路板技术、先进混合集成电路技术、先进表面安装技术、半导体集成电路技术于一体，是典型的垂直集成技术，对半导体器件来说，它是典型的柔性封装技术，是一种电路的集成。MCM的出现使电子系统实现小型化、模块化、低功耗、高可靠性提供了更有效的技术保障。

其中MCM-D型（Mulit Chip Module—Deposited Thin Film）是采用薄膜技术将金属材料淀积到陶瓷或硅、铝基板上，光刻出信号线、电源线地线，并依次做成多层基板，多达几十层。主要用在500Mhz以上的高性能产品中，线宽和间距可做到10-25mm  $\mu$ m，孔径在1050  $\mu$ m，因而，具有组装密度高，信号通道短，寄生效应小，噪声低等优点，可明显地改善系统的高频性能。

现在我们可以看到如今的高新技术PCB已经不是我们所认为的印制线路板了，也许又该提升一步叫光刻线路板了。

### 3. 表面贴装技术(SMT)的介绍

#### 1) SMT的特点

- 组装密度高、电子产品体积小、重量轻，贴片元件的体积和重量只有传统插装元件的1/10左右，一般采用SMT之后，电子产品体积缩小40%~60%，重量减轻60%~80%。

- 可靠性高、抗振能力强。焊点缺陷率低。

- 高频特性好。减少了电磁和射频干扰。

- 易于实现自动化，提高生产效率。降低成本达 30%~50%。节省材料、能源、设备、人力、时间等。

## 2) 为什么要用表面贴装技术(SMT)?

- 电子产品追求小型化，以前使用的穿孔插件元件已无法缩小

- 电子产品功能更完整，所采用的集成电路(IC)已无穿孔元件，特别是大规模、高集成 IC，不得不采用表面贴片元件

- 产品批量化，生产自动化，厂方要以低成本高产量，出产优质产品以迎合顾客需求及加强市场竞争力

- 电子元件的发展，集成电路(IC)的开发，半导体材料的多元应用

- 电子科技革命势在必行，追逐国际潮流

## 3) SMT 技术的发展趋势

随着电子产品向便携式/小型化、网络化和多媒体方向迅速发展，表面贴装技术 (Surface Mount Technology, 简称 SMT) 在电子工业中正得到越来越广泛的应用，并且在许多领域部分或全部取代了传统电子装联技术。SMT 的出现使电子装联技术发生了根本的、革命性的变革。在应用过程中，SMT 正在不断地发展与完善，主要表现在以下几方面：

- SMT 生产线的发展

- SMT 生产线是生产的基础，目前其有如下几个发展趋势：计算机集成制造系统 (CIMS) 的应用、SMT 生产线正向高效率方向发展、SMT 生产线向“绿色”环保方向发展。

- SMT 设备的发展：包括丝印设备、贴装设备的发展。

- (FMS)、多功能等方向发展

- 表面贴装元器件的发展

- SMT 工艺材料的发展

## 4. PCB 电镀金工艺介绍

### 作用与特性：

印制板上的金镀层有几种作用。金作为金属抗蚀层，它能耐受所有一般的蚀刻液。它的导电率很高，其电阻率为 2.44 微欧—厘米。由于它的负的氧化电位，使得它是一种抗锈蚀的理想金属和接触电阻低的理想接触表面金属。金作为可焊性的基底，是多年来争论的问题之一。只要说明金在控制条件下，已经成功地用来作为一种焊接的辅助手段就够了。

近年来已经发展了一些新的镀金工艺，它们大多数是专利性的。这表明为避开以典的碱性氰化物镀金及其对电镀抗蚀剂的破坏作用所作的努力。金价格成本高，促使发展金的合金槽浴，作为降低成本的手段。

## 5. PCB 电镀铜工艺介绍

铜作为印制电路制造中的基本的导线金属，已经得到了广泛的承认。它具有极为优越的导电性(仅次于银)、容易电镀、成本低、并给出高度可靠的结果。铜是很容易活化的，因此在铜和其它电镀的金属之间，可以获得良好的金属—金属键合。“电子设备用的印制电路，MIL—STD—275”指出：“金属化应该镀铜，孔中铜镀层的厚度应不小于 0.001 英寸。”有三种最常用的镀铜溶液：焦磷酸盐、硫酸盐以及氟硼酸盐溶液。

## 6. 多层板孔金属化工艺

众所周知, 孔金属化是多层板生产过程中最关键的环节, 她关系到多层板内在质量的好坏。孔金属化过程又分为去钻污和化学沉铜两个过程。化学沉铜是对内外层电路互连的过程; 去钻污的作用是去除高速钻孔过程中因高温而产生的环氧树脂钻污(特别在铜环上的钻污), 保证化学沉铜后电路连接的高度可靠性。多层板工艺分凹蚀工艺和非凹蚀工艺。凹蚀工艺同时要去除环氧树脂和玻璃纤维, 形成可靠的三维结合; 非凹蚀工艺仅仅去除钻孔过程中脱落和汽化的环氧钻污, 得到干净的孔壁, 形成二维结合, 单从理论上讲, 三维结合要比二维结合可靠性高, 但通过提高化学沉铜层的致密性和延展性, 完全可以达到相应技术要求。非凹蚀工艺简单、可靠, 并已十分成熟, 因此在大多数厂家得到广泛应用。高锰酸钾去钻污是典型的非凹蚀工艺。

## 7. PCB 表面处理技术

虽然以产品生命周期短和迅猛的技术改变闻名, 电子工业还不得不采用一种工业应用广泛的热空气焊锡均涂(HASL, hot air solder leveling)的替代技术。

长期影响。环境的关注通常集中在潜在的铅泄漏到环境中去。尽管在北美的立法禁止铅的使用还是几年后的事情, 但是原设备制造商(OEM, original equipment manufacturer)必须满足欧洲和日本的环境法令, 以使其产品作全球销售。这个考虑已经孕育出许多课题, 评估在每一个主要的 OEM 那里消除铅的可选方法。

HASL 的替代方法允许无铅印刷电路板(PWB, printed wiring board), 也提供平坦的共面性表面, 满足增加的技术要求。更密的间距和区域阵列元件已允许增加电子功能性。通常, 越高的技术对立着降低成本。可是, 大多数替代方法改进高技术装配和长期的可靠性, 而还会降低成本。

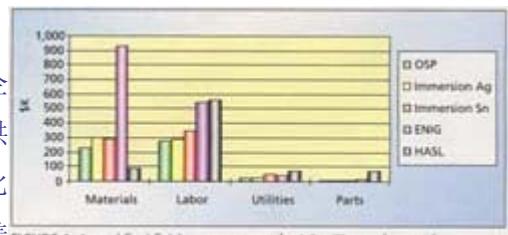

成本节约是整个过程成本的函数, 包括过程化学、劳力和企业一般管理费用(图一)。象 OSP、浸银和浸锡等替代技术可提供最终表面处理成本的 20 ~ 30% 的减少。虽然每块板的节约百分比在高层数多层电路板产品上可能低, 日用电子的成本节约, 随着更大的功能性和铅的消除, 将驱使替代方法使用的急剧增加。

替代方法的使用将不仅会增加, 而且将取代 HASL 作为最终表面处理的选择。今天替代的问题是选择的数量和已经发表的数据的纯卷积。诸如 ENIG、OSP、浸锡和浸银等替代方法都提供无铅、高可焊性、平整、共面的表面, 在生产中对第一次通过装配合格率提供重大改进。为了揭开最终表面处理的神秘面纱, 这些 HASL 的替代方法可通过比较每个涂层对装配要求和 PWB 设计的优点来区分。

### 装配要求

HASL 替代方法对装配过程的作用反映表面的可焊性和它如何与使用的焊接材料相互作用。每一类替代的表面涂层 — OSP、有机金属的 organometallic(浸锡和银)或金属的(ENIG) — 具有不同的焊接机制。焊接机制的这种差异影响装配过程的设定和焊接点的可靠性。

OSP 是焊接过程中必须去掉的保护性涂层。助焊剂必须直接接触到 OSP 表面, 以渗透和焊接到 PWB 表面的铜箔上。<sup>1</sup>

浸洗工艺, 如浸银或锡, 有机共同沉淀消除最终表面的氧化物。不象 OSP, 锡和银溶解在焊锡里面,

将成为焊接点的一部分，将帮助熔湿速度。锡和银两者都在 PWB 的铜表面直接形成焊接点。

如果适当地沉淀，在 ENIG 表面的金是纯净的，由于其可熔于焊锡，所以将提供焊接的最快的熔湿速度。可是，当使用 ENIG 时，焊接点是在镍障碍层上面形成的，不是直接在 PWB 的铜表面。

所有三类替代涂层都提供最佳的印刷表面，对所有类型的锡膏都一样。锡膏直接印在表面涂层上面，提供助焊剂直接接触、渗透 OSP 和熔湿 PWB 表面。印刷模板对沉积完美的锡膏印刷，形成有效的密封，消除了 HASL 的印糊和锡桥问题。结果是三种替代涂层都有很高的第一次通过装配合格率，焊锡熔湿方面相差很小。区别在于焊接点的强度和可靠性。几个研究已经证实，使用 OSP，直接焊接到铜的表面，提供最好强度的焊接点。<sup>2,3</sup>当使用区域阵列片状包装的较小焊盘时，焊接点的强度变得重要。

虽然使用上减少，波峰焊接还是今天装配过程的构成整体的一部分。每一种最终表面涂层的焊接机制将影响助焊剂化学成分的选择和波峰焊接工艺的设定。金属的和有机金属的涂层有助于通孔的焊锡熔湿，通常要求很少的助焊剂、较低活性的助焊剂和波峰的较少动荡。免洗材料在生产条件下与 OSP 相处很好，但要求一些优化来增加助焊剂和/或焊锡渗透到通孔内。通常，这个优化增加助焊剂的使用量，代替特定类型的助焊剂化学成分，或通过更高的动荡或温度来增加焊锡渗透。

全球范围内正在实施取代传统波峰焊接工艺的方法。插入式回流(intrusive reflow)、选择性焊锡喷泉(selective solder fountain)和顺应针(compliant pin)正实际上使用在所有最终表面涂层上。至今为止所完成的工作表明，选择性焊锡喷泉的动荡改善了通孔(through-hole)的可熔湿性。孔中锡膏(paste-in-hole)或侵入式回流将助焊剂和助焊剂载体直接接触 PWB 的表面，使得通孔的可熔湿性对所有最终表面涂层都是类似的。最后，由于可预见的孔的误差，HASL 的替代方法比使用顺应针(compliant pin)的 HASL 要强。在替代方法中，较厚的浸锡为插件提供最光滑的表面，为顺应针提供最宽的操作窗口。<sup>4</sup>

装配工业现在正评估无铅焊接替代品。虽然某些合金似乎是特别的 OEM 的选择，但是，还要选择整个工业所接受的合金。尽管如此，正在测试的所有合金都要求较高的回流温度，并产生较慢的熔湿速度。锡膏供应商已经工程研究了专门的助焊剂化学成分，来改善这些新合金的熔湿。初始的研究表明较高的回流温度不会影响 OSP、浸银或浸锡的可焊性或绑接强度。较高的熔化温度明显地帮助 OSP 的渗透和锡与银表面熔湿，甚至是双面回流。另外的测试正在进行中，以评估熔湿速度的影响和优化对最终表面涂层的特定回流参数。

## PWB 设计

正如所讨论的，装配过程可以优化，以适合所有的最终表面涂层。PWB 的设计将最终决定适于各个应用的最佳的 HASL 替代方法，但更专门的包装和互连的类型：

象按键接触(key contact)、元件屏蔽(component shielding)和插件连接器(edge connector)这样的应用要求在整个设备寿命内的接触电阻低。

柔性的电路板通常要求铝的或不锈钢的加强构件或散热器。

元件包装和某些 PWB 要求引线接合(wire bonding)或与直接芯片附着用的导电性胶的兼容性。

PWB 上的高密度互连(HDI, high-density interconnect)几何形状戏剧性地影响使用传统无电镀涂层的合格率。

已经看到由于装配在 ENIG 上的区域阵列包装的绑接强度不够而出现的现场失效(field failure)。

为了满足所有这些要求，电子工业正将注意力集中在三种主要的替代方法上：OSP、浸银和浸锡。这三种涂层的每一种都提供适合特定 PWB 设计要求的优势。

OSP 是成本最低的替代方法，与多金属表面兼容，提供最高的绑接强度。现在有新的配方，提供较薄的沉淀层，和原先的、消除了多金属表面生锈的一样牢固(图二)。由于耐磨性或电解金沉淀的可焊性，要求多金属涂层，如用于插件连接器或金引线接合(gold wire bonding)的电解镍/金。高成本和焊接点中金的易脆性要求 OSP 对已焊接的连接作第二次涂层。

虽然生产已证实按键接触，但使用，如果焊接点的强度对 PWB 设使得 OSP 成为移动电子和区域阵列择。OSP 也显示与使用在倒装芯片性(图三)。最后，散热器或刚性构容易地应用在板列形式。不象 OSP，铝上面，引起变色。

和 OSP 与 ENIG 比较, 浸银还是一个相对较新的技术。可是, 在过去六年里, 广泛的测试和大量的生产已经证实了这个工艺的可靠性<sup>5,6</sup>。焊锡的熔湿特性使得这种涂层更适合于一种现存的无铅波峰焊接工艺。这种表面处理方法是大多数应用的潜在替代方法, 包括屏蔽、铝引线接合、按键接触和焊接。

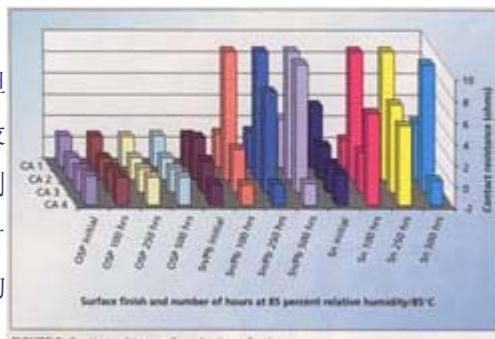

如表一所示，这个涂层的接触电阻在经过老化或回流工序之后保持很低。初始的研究显示，接触电阻在与导电聚合物接触 300,000 次后保持很低，虽然更多工作需要完成。作为一种金属涂层，浸银也可以在低放大或不放大的情况下检查，使得应用者和装配者两个都容易决定其存在。

**FIGURE 2:** New OSP process on mixed metal PWB

ENIG 也可以和新的 OSP 工艺一起

计是关键的话。这个高接合强度

包装 (area array package) 的选

应用中的导电性胶的更大的兼容

件大都可以在最终表面处理之前

浸或无电镀工艺将镀在不锈钢或

表一、浸银涂层的接触电阻

系列二，探针半径 0.020", 接触力 10oz。模拟压缩连接器的 100% 接合。电阻以欧姆测量。

| 涂层  | 处理     | 系列号      | 读数#1  | 读数#2  | 读数#3  |

|-----|--------|----------|-------|-------|-------|

|     |        |          | 电阻    | 电阻    | 电阻    |

| OSP | BTH 处理 | 10370KG2 | 0.500 | 1.25  | 0.500 |

| OSP | 无环境处理  | 10370KKY | 0.500 | 0.500 | 0.500 |

| 锡   | BTH 处理 | 10370KGM | 0.025 | 0.025 | 0.025 |

| 锡   | 无环境处理  | 10370KHW | 0.025 | 0.025 | 0.025 |

| 银   | BTH 处理 | 10370K9Z | 0.025 | 0.025 | 0.025 |

| 银   | 无环境处理  | 10370K8Y | 0.025 | 0.025 | 0.025 |

| 镍/金 | 无环境处理  | 无        | 0.025 | 0.025 | 0.025 |

|           |       |   |       |       |       |

|-----------|-------|---|-------|-------|-------|

| Sn63/Pb37 | 无环境处理 | 无 | 0.025 | 0.025 | 0.025 |

|-----------|-------|---|-------|-------|-------|

浸锡已经在 PWB 和金属表面处理工业使用几十年了。可是，已经开发出新的化学成分，使有机物与锡一起沉淀在铜的表面。这种共同沉淀的有机物消除纤维状结晶(whisker)的增长，这是一个可靠性问题，阻碍铜锡金属间的增长，影响可焊接性能。

这些新的浸锡工艺的结果是，较厚的最终表面涂层(30 ~ 50 millionths 百万分之一)，提供光滑表面给顺应针插件和在线测试(CT, in-circuit test)渗透。正在进行中的研究，评估相对 CT 探针磨损和几种最终表面涂层的性能。新的浸锡工艺很容易适应无铅装配，并与浸银一样，它们的存在容易检查。

## 结论

OSP、浸银和浸锡用于混合技术和水溶性与免洗装配技术，都将提供高的第一次通过装配合格率。每个产品的适当应用是通过 PWB 的设计要求来明确的：

OSP 是成本最低的涂层，为芯片规模(chip-scale)和倒装芯片(flip chip)包装提供最好的焊接强度。新的配方能够处理多金属表面，如镍/金带自动连接(TAB, tape automated bonding)或铝散热器和刚性构件。

浸银提供一种可引线接合的(wire bondable)单一的表面涂层，具有对按键接触的和金属对金属屏蔽的低接触电阻。

浸锡提供较厚的、均匀金属涂层，改善 CT 探针寿命和压入装配针的光滑性。

OSP 已经是 HASL 替代品的市场主流，为应用者提供最宽的处理窗口。作为较新的产品，浸银和锡还必须达到相同的市场渗透，现在，要求应用过程中更多的关注。全球都在作经验积累，以解决工艺问题，使得可以从 HASL 容易地转换到其它替代方法。

## 三、印制板产品的 DFM

DFM(Design For Manufacture)指“为制造着想的设计”。这些年，虽然 DFM 已被各种各样的定义，但一个基本的理念是相同的：为了在制造阶段，以最短的周期、最低的成本达到最高可能的产量，DFM 必须在新产品开发的概念阶段有具体表现。

### 1、DFM 的开始

首先，必须认识到 DFM 的必要性。这个对一个高级管理成员来说可以最有效率地完成，但时常对具体实施 DFM 的初级雇员来说是另外一回事。他们通过参与 DFM 会议或研讨会来自我教育，与他人共享知识。内部推广 DFM 的其它方法包括，把有关 DFM 的研究提交给关键人物或邀请顾问与公司领导讨论 DFM。成功至少需要工程和制造两方面的领导确信 DFM 的必要，之后，组织的其余部分尽可能地予以支持。

开始 DFM 的下一个步骤就是，找一个可以监督这个过程的雇员。这意味着他必须具有工程和制造两个方面的技术背景。雇员必须了解公司的工程方面，从而理解涉及到研究、开发和设计产品的各种要求，这样他或她可以在新产品开发周期内的修正阶段影响产品。类似地，该人必须了解制造工序的能力，以加强资本和补偿任何薄弱环节。一个人在足够的细节上广泛地了解工程和制造两大功能块，是不寻常的，因此对有潜力的关键人物的循环计划应该用来开发这些技能。外部招聘，作为这个长远培训步骤的替代，是另一个保证 DFM 资源的方法。可是，这个人的关键是了解你公司的工程和制造过程。把工程要求和制造能力合理的匹配是 DFM 成功的关键。

一旦指定一个人为 DFM 职位，重要的是他或她了解现在可利用的技术和将来有前景的技术。找到和把这

些知识带入公司是重要的,这样,工程部门可以将它体现在产品设计中,制造部门可以生产出来。转换技术的有用方法是阅读关键的技术杂志或期刊、参加技术研讨会、会见供应商、访问和调查公司、参加工程协会的本地分会、和浏览因特网。收集新技术的样品,带到会议中或简单地展示陈列出来,这样做可以引起人们的兴趣和产生应用的想法。技术转换研讨和会议(经常举行),有工程和制造两方参加,对开始教育步骤是必须的。类似的会议也会把想法汇集成讨论议题。

得到技术知识后,下一步必须决定这个新人物应该“安顿”在哪里,组织上向哪里汇报。我们推荐该人和设计部门“共处”在一起,这样,所有的交互作用都在实时发生。另外,由于成为部门的信息资产,DFM人员有机会和人们建立和睦与尊重。虽然DFM人员可以向工程或制造部门汇报,推荐的方法是使其向制造部门汇报,而驻扎在工程部。这样,他或她对制造部有必要的效忠,同时对工程部提供有价值的服务。

开始DFM时,考虑的另外的步骤是:统一从制造到工程的信息流(即,用同一种声音说同一种语言);告诉设计和生产人员彼此的能力,让设计人员参观生产,反过来也是;拆除工程与制造部门之间的墙,通过每天设计部门解答DFM问题,成功地把新产品推向生产,量化DFM的影响,然后推出市场。

## 2、工具和技术

有许多商业够买的DFM工具,以及那些世界级公司内部创建的工具。DFM工具是为了提供一个框架,以目标的方式来使一个设计的可制造性的测量和影响特征化。

**DFM指南:**是为一个公司制定预期结果基线所必须的。工程部设计达到一套规格或要求,制造部具备某种的生产能力。要求和能力的同步为两个功能部门设定期望。DFM指南形成工程与制造部门之间的桥梁,成为通信工具。它可以开始是一页简单的合理的行动列表。例如,PCB DFM指南应该包括首选元件与包装、优化的板/组合板尺寸、元件之间的间距要求和生产设备的边缘空留。后来,可能进化成一本更复杂和更全面的手册,定义每一个有用的部分和过程。当然,最好开始简单,使得指南清楚交流、容易理解和马上可用作参考(即,摆在每一个设计者的桌面上)。信息越复杂,越可能被放在某个人的书架上,而不是新产品设计时实际的查阅。和其它任何文件一样,指南必须得到维护,以使其准确地描述制造者的能力。当生产自动设备被替换或更新或新技术引入时,这一点特别重要。

**DFM反馈步骤:**为了有效地传播制造车间和工程实验室所得到的知识经验,这一点是必要的。一个有效的方法是,由生产人员使用制造工艺来建立所有的工程模型。这是一个被证实的方法,用来传递成功建立产品的建设性的反馈信息。因此不会出现奇怪的问题,当一个产品发放给生产,因为那些相同的生产工艺已经在整个设计周期内已经用到。反馈必须传递迅速准确,使得设计小组可以马上更正由生产人员在模型上所观察到的任何问题。如人们所预料,在生产设备上运行模型制造会消耗额外的生产能力,因此,必须适当的考虑到预测的负荷要求。

**假设分析模型:**用这种方法来完成一个设计相对另一个设计的量化的可制造性测量。虽然相当简单,但它实现了极大的DFM影响力。模型表现了制造中每个装配工艺的特色:百万缺陷率(dpm, defects per million)、设定时间和运行时间。使用者输入每个工艺步骤加入的元件数量。模型输出三个关键变量的计算结果:预计周期时间、预计成本和预计产量。工具的作用是可以把非DFM PCB设计和实现优化步骤的DFM PCB设计进行比较(即,进行假设模型分析)。假设模型分析的一个例子可以从表一中看到。表中列出了PCB X的DFM

前后的周期时间、成本和产量的计算。这允许两个装配之间这些变量差别的比较，以看出 DFM 的影响。将价格差乘以预计年生产的 PCB 数量，得到预计的年度成本节约，这个然后可以和预计的改造实施成本比较。表一描述的例子显示了 66% 的成本和周期时间的减少，DFM 应用板比非 DFM 应用板高出 10% 的产量改进。这个模型可以用来作出商业决定，在目标、量化数据的基础上实施 DFM。

| PCB 装配的假设分析模型 *   |           |     |       |          |                  |       |          |                 |       |          |  |

|-------------------|-----------|-----|-------|----------|------------------|-------|----------|-----------------|-------|----------|--|

|                   | Standards |     |       |          | PCB X before DFM |       |          | PCB X after DFM |       |          |  |

| Process           | dpm       | S/U | Run   | Variable | S/U              | Run   | Quantity | S/U             | Run   | Quantity |  |

| Stencil Print(T)  | 20        | 5   | 0.5   | (PCB)    | 5                | 0.5   | 1        | 5               | 0.5   | 1        |  |

| Chip Place        | 100       | 10  | 0.012 | (SMT)    | 10               | 0.048 | 4        | 10              | 0.312 | 26       |  |

| IC Place          | 200       | 15  | 0.025 | (SMT)    | 0                | 0     | 0        | 0               | 0     | 0        |  |

| Reflow            | 25        | 5   | -     | Internal | 5                | 0.3   | 1        | 5               | 0.3   | 1        |  |

| Stencil Print(B)  | 20        | 5   | 0.5   | (PCB)    | 0                | 0     | 0        | 0               | 0     | 0        |  |

| Chip Place        | 100       | 10  | 0.012 | (SMT)    | 0                | 0     | 0        | 0               | 0     | 0        |  |

| IC Place          | 200       | 15  | 0.025 | (SMT)    | 0                | 0     | 0        | 0               | 0     | 0        |  |

| Reflow            | 25        | 5   | -     | Internal | 0                | 0     | 0        | 0               | 0     | 0        |  |

| Clean             | 10        | 5   | 0.3   | (PCB)    | 0                | 0     | 0        | 0               | 0     | 0        |  |

| DIP               | 5000      | 15  | 0.1   | (Comp)   | 0                | 0     | 0        | 0               | 0     | 0        |  |

| Sequence          | 1500      | 20  | 0.02  | (Comp)   | 20               | 0.26  | 13       | 0               | 0     | 0        |  |

| VCD               | 1500      | 15  | 0.03  | (Comp)   | 15               | 0.39  | 13       | 0               | 0     | 0        |  |

| Radial            | 5000      | 30  | 0.04  | (Comp)   | 0                | 0     | 0        | 0               | 0     | 0        |  |

| Stake             | 6000      | 10  | 0.14  | (Comp)   | 0                | 0     | 0        | 0               | 0     | 0        |  |

| Mask              | 2500      | 10  | 0.05  | (Point)  | 10               | 0.15  | 3        | 0               | 0     | 0        |  |

| Adhesive Dispense | 50        | 5   | -     | Internal | 5                | 0     | 50       | 5               | 0     | 50       |  |

| Chip Place        | 100       | 10  | 0.12  | (SMT)    | 10               | 0.6   | 50       | 10              | 0.6   | 50       |  |

| IC Place          | 200       | 15  | 0.025 | (SMT)    | 0                | 0     | 0        | 0               | 0     | 0        |  |

| Cure              | 25        | 5   | -     | Internal | 5                | 0     | 1        | 5               | 0     | 1        |  |

| Clean             | 10        | 5   | 0.3   | (PCB)    | 0                | 0     | 0        | 0               | 0     | 0        |  |

| Prep              | 5000      | 15  | 0.1   | (Comp)   | 15               | 0.7   | 7        | 0               | 0     | 0        |  |

|                                                                                |       |    |         |                |    |      |         |        |      |     |  |  |  |  |  |  |

|--------------------------------------------------------------------------------|-------|----|---------|----------------|----|------|---------|--------|------|-----|--|--|--|--|--|--|

| Prewave                                                                        | 7500  | 10 | 0.2     | (Comp)         | 10 | 2    | 10      | 10     | 0.8  | 4   |  |  |  |  |  |  |

| Wave Solder/Clean                                                              | 2000  | 5  | 0.7     | (PCB)          | 5  | 0.7  | 1       | 5      | 0.7  | 1   |  |  |  |  |  |  |

| Postwave Difficult                                                             | 15000 | 10 | 3       | (Comp)         | 10 | 9    | 3       | 0      | 0    | 0   |  |  |  |  |  |  |

| Postwave Easy                                                                  | 10000 | 10 | 1       | (Comp)         | 0  | 0    | 0       | 0      | 0    | 0   |  |  |  |  |  |  |

| Clean                                                                          | 500   | 5  | 0.3     | (PCB)          | 5  | 0.3  | 1       | 0      | 0    | 0   |  |  |  |  |  |  |

| Depanel                                                                        | 5000  | 5  | 1.5     | (PCB)          | 5  | 6    | 4       | 5      | 1.5  | 1   |  |  |  |  |  |  |

| Conformal Coat                                                                 | 10000 | 20 | 10      | (PCB)          | 20 | 10   | 1       | 20     | 10   | 1   |  |  |  |  |  |  |

| Inspection                                                                     | 500   | 5  | 0.007   | (Solder Joint) | 5  | 1.12 | 160     | 5      | 1.12 | 160 |  |  |  |  |  |  |

|                                                                                |       |    |         |                |    |      |         |        |      |     |  |  |  |  |  |  |

| Enter Lot Size                                                                 | 50    |    |         |                | 50 |      |         |        |      |     |  |  |  |  |  |  |

| Enter Realization                                                              | 0.55  |    |         |                |    |      |         |        |      |     |  |  |  |  |  |  |

| 0.8                                                                            |       |    |         |                |    |      |         |        |      |     |  |  |  |  |  |  |

| I.E. Minutes                                                                   | 165   |    | 32.068  |                |    |      | 90      | 15.832 |      |     |  |  |  |  |  |  |

| Prorated Setup                                                                 | 3.3   |    |         |                |    |      | 1.8     |        |      |     |  |  |  |  |  |  |

| Total I.E. Min.                                                                |       |    | 35.368  |                |    |      | 17.632  |        |      |     |  |  |  |  |  |  |

| Total I.E. Hours                                                               |       |    | 0.589   |                |    |      | 0.294   |        |      |     |  |  |  |  |  |  |

| Expected Cycle Time                                                            |       |    | 1.072   |                |    |      | 0.367   |        |      |     |  |  |  |  |  |  |

| Expected Cost                                                                  |       |    | \$32.15 |                |    |      | \$11.02 |        |      |     |  |  |  |  |  |  |

| Expected Yield                                                                 |       |    | 89.40%  |                |    |      | 98.70%  |        |      |     |  |  |  |  |  |  |

| * All numbers are fictitious and are intended for instructional purposes only. |       |    |         |                |    |      |         |        |      |     |  |  |  |  |  |  |

表一.

**DFM 计分:**这个工具描述了对一个特定产品设计的每个重要的可制造性特征。表二是 PCB 可制造性的计分表。它显示了 18 个对生产重要的可制造性特征，分成三个部分：元件、设计和制造工艺。规格在设计开始时由 DFM 人员和设计小组决定，给出或者是 1 或者是 0 的等级(1 = 希望的特征，0 = 不希望的特征)。然后，在设计周期的每个连续的硬件(即，原型 1，原型 2，制造模型和生产)重复操作期间，每个特征用 1 和 0 计分(1 = 达到，0 = 没达到)。计分累计和被除(除以 18)，然后与工具底部给定的等级比较。几个重要的结果从这种工具的使用中得到。这些结果中：通常得到所希望的分数(在世界级的级别中)，因为它们是按标准的，高分的竞争在设计者中升起，人们得到高分的回报。突然，工程部门努力获取 DFM 的高分。

| Design for Manufacturability Scoring |             |         |         |                     |            |

|--------------------------------------|-------------|---------|---------|---------------------|------------|

| Project: X                           |             |         |         |                     |            |

| Board #: Y                           |             |         |         |                     |            |

| Components                           | Specs       | Proto 1 | Proto 2 | Manufacturing Model | Production |

| <1% sole-sourced components          | 1           | 0       | 0       | 1                   | 1          |

| >95% PPSL compliance                 | 1           | 1       | 1       | 1                   | 1          |

| Process compatible packaging         | 1           | 0       | 1       | 1                   | 1          |

| Component count - single pass        | 1           | 1       | 1       | 1                   | 0          |

| <2% hardware                         | 1           | 0       | 0       | 0                   | 1          |

| Correct Strategy selected            | 1           | 0       | 0       | 0                   | 1          |

|                                      |             |         |         |                     |            |

| Design                               |             |         |         |                     |            |

| Optimal PCB panel                    | 1           | 0       | 1       | 1                   | 1          |

| Fabrication DRC resolved             | 1           | 0       | 0       | 0                   | 0          |

| Zero defect documentation            | 1           | 0       | 0       | 1                   | 1          |

| CAM ready data                       | 1           | 1       | 1       | 1                   | 1          |

| Within PCB design guidelines         | 1           | 1       | 1       | 1                   | 1          |

| Process compatible orientation       | 1           | 0       | 1       | 1                   | 1          |

|                                      |             |         |         |                     |            |

| Manufacturing Process                |             |         |         |                     |            |

| Correct material packaging           | 1           | 0       | 0       | 1                   | 1          |

| Automation content >90%              | 1           | 1       | 1       | 1                   | 1          |

| <1% post wave process                | 1           | 0       | 0       | 0                   | 1          |

| Process steps <10                    | 1           | 0       | 0       | 0                   | 1          |

| No fixtures/tools required           | 1           | 1       | 1       | 1                   | 1          |

| 6 sigma yield possible               | 1           | 0       | 0       | 1                   | 1          |

| DFM Score                            | 18%         | 33%     | 50%     | 72%                 | 89%        |

| 93-100%                              | World Class |         |         |                     |            |

|        |                       |

|--------|-----------------------|

| 85-92% | Highly Manufacturable |

| 77-84% | Acceptable            |

| 69-76% | Poor                  |

| 0-68%  | Unacceptable          |

表二

**生产就绪检查:**当一个工程产品设计完成, 何时才准备就绪接受设计呢? 这些经常是公司要问的关键问题。虽然答案各异, 但一个证明成功的方法是生产就绪检查。这是一个重要的 DFM 工具, 因为市场是竞争性的, 顾客要求高品质、具竞争性价格、达到市场快的产品, 要求在新产品引入的开始为可制造性设计的产品。这个工具检查来自整个新产品设计周期内每个功能部门的每个可传递任务的完成情况。工程可传递任务的一个例子是, 所有发放给制造部门的图纸, 用于订货到交货时间内的材料采购。因此, 工程部有 X 可传递, 制造部有 Y 可传递。每一个这些可传递任务在整个设计周期的某个关口(即, 检查点)检测。跨功能的新产品小组决定何时这些可传递任务必须完成, 然后检查就绪完成情况。现在这个变成一项很目标性的检查, 何时工程完成, 是否制造准备就绪。例如, 在 10 个月的开发周期内有 10 个不同的关口, 工程部报告 75 个可传递任务中有 50 个完成, 而制造部在第 10 个关口报告, 100 个可传递任务中有 100 个已完成, 那么很清楚, 工程没有完成, 制造准备就绪, 需要等待。

所有这些工具 – DFM 指南、DFM 反馈、假设分析模型、DFM 计分和生产就绪检查 – 都是内部开发的。应该做成本对效益的平衡, 以便合理的决定是否购买许多商业 DFM 工具之一, 或者创建更适合公司需要的用户化 DFM 工具。关键是使用必要的工具达到所希望的 DFMM 影响。

## 结论

DFM 在过去 20 年里, 已变成改善成本、品质和周期时间的通用方法。结果, DFM 的概念、工具和技术在这段时间变得越来越组织化。随着这种成熟, 该知识, 过去只能在教科书、手册和个人数据库中找到, 已在计算机软件工具中找到去路。该趋势将继续, 直到 CAE 工作站 “知道” 了一个制造工艺的全部特性, 并能够开发其过程能力。

可是, 没有必要等待到未来去发生。这里所提到的 DFM 概念和工具, 只是电子装配工业中, DFM 过程成功实施的已被证实的技术例证。当然, 不同的产品和工艺过程将要求细节上的变化, 但是概念和工具是可移植的。

## 有关的工业标准文件

有许多工业文件可用于帮助 DFM 的实施。下面是一览子设计有关的文件, 有关这些或其它文件的情况, 或要购买文件, 请联系:

IPC – Association Connecting Electronics Industries, (846) 509-9700.

Surface Mount Equipment Manufacturers Association (SMEMA), (847) 831-1002.

Electronic Industries Alliance (EIA), (703) 907-7500.

|            |                                                                                  |

|------------|----------------------------------------------------------------------------------|

| IPC-T-50   | Terms and Definitions for Interconnecting and Packaging Electronic Circuits      |

| IPC-D-275  | Design Standard for Rigid Printed Boards and Rigid Printed Board Assemblies      |

| IPC-D-279  | Design Guidelines for Reliable Surface Mount Technology Printed Board Assemblies |

| IPC-D-322  | Guidelines for Selecting Printed Wiring Board Sizes Using Standard Panel Sizes   |

| IPC-D-325  | Documentation Requirements for Printed Boards, Assemblies, and Support Drawings  |

| IPC-D-330  | Design Guide Manual                                                              |

| IPC-D-390  | Automated Design Guidelines                                                      |

| IPC-C-406  | Design and Application Guidelines for Surface Mount Connectors                   |

| IPC-SM-782 | Surface Mount Design and Land Pattern Standard                                   |

| IPC-EM-782 | Surface Mount Design and Land Pattern Standard Spreadsheet                       |

| EIA-JEP-95 | JEDEC Registered and Standard Outlines for Semiconductor Devices                 |

| SMEMA 3.1  | Fiducial Design Standard                                                         |

设计丝印层的有关内容时，只注意文字符号放置得整齐美观，忽略了实际制出的 PCB 效果。他们设计的印板上，字符不是被元件挡住就是侵入了助焊区域被抹除，还有的把元件标号打在相邻元件上，如此种种的设计都将会给装配和维修带来很大不便。正确的丝印层字符布置原则是：“不出歧义，见缝插针，美观大方”。

资料收集: 收藏天地 2001

本站国际域名: [www.maihui.net](http://www.maihui.net)

<http://maihui.top263.net/>

<http://pcb2002new.a2.cn4e.com/>

联系方式:

联系邮址: [killmai@163.net](mailto:killmai@163.net)

OICQ 号码: 13985548

联系电话: 13189611215

---

## 射 频 和 天 线 设 计 培 训 课 程 推 荐

易迪拓培训([www.edatop.com](http://www.edatop.com))由数名来自于研发第一线的资深工程师发起成立，致力并专注于微波、射频、天线设计研发人才的培养；我们于 2006 年整合合并微波 EDA 网([www.mweda.com](http://www.mweda.com))，现已发展成为国内最大的微波射频和天线设计人才培养基地，成功推出多套微波射频以及天线设计经典培训课程和 ADS、HFSS 等专业软件使用培训课程，广受客户好评；并先后与人民邮电出版社、电子工业出版社合作出版了多本专业图书，帮助数万名工程师提升了专业技术能力。客户遍布中兴通讯、研通高频、埃威航电、国人通信等多家国内知名公司，以及台湾工业技术研究院、永业科技、全一电子等多家台湾地区企业。

易迪拓培训课程列表：<http://www.edatop.com/peixun/rfe/129.html>

### 射频工程师养成培训课程套装

该套装精选了射频专业基础培训课程、射频仿真设计培训课程和射频电路测量培训课程三个类别共 30 门视频培训课程和 3 本图书教材；旨在引领学员全面学习一个射频工程师需要熟悉、理解和掌握的专业知识和研发设计能力。通过套装的学习，能够让学员完全达到和胜任一个合格的射频工程师的要求…

课程网址：<http://www.edatop.com/peixun/rfe/110.html>

### ADS 学习培训课程套装

该套装是迄今国内最全面、最权威的 ADS 培训教程，共包含 10 门 ADS 学习培训课程。课程是由具有多年 ADS 使用经验的微波射频与通信系统设计领域资深专家讲解，并多结合设计实例，由浅入深、详细而又全面地讲解了 ADS 在微波射频电路设计、通信系统设计和电磁仿真设计方面的内容。能让您在最短的时间内学会使用 ADS，迅速提升个人技术能力，把 ADS 真正应用到实际研发工作中去，成为 ADS 设计专家…

课程网址：<http://www.edatop.com/peixun/ads/13.html>

### HFSS 学习培训课程套装

该套课程套装包含了本站全部 HFSS 培训课程，是迄今国内最全面、最专业的 HFSS 培训教程套装，可以帮助您从零开始，全面深入学习 HFSS 的各项功能和在多个方面的工程应用。购买套装，更可超值赠送 3 个月免费学习答疑，随时解答您学习过程中遇到的棘手问题，让您的 HFSS 学习更加轻松顺畅…

课程网址：<http://www.edatop.com/peixun/hfss/11.html>

## CST 学习培训课程套装

该培训套装由易迪拓培训联合微波 EDA 网共同推出, 是最全面、系统、专业的 CST 微波工作室培训课程套装, 所有课程都由经验丰富的专家授课, 视频教学, 可以帮助您从零开始, 全面系统地学习 CST 微波工作的各项功能及其在微波射频、天线设计等领域的设计应用。且购买该套装, 还可超值赠送 3 个月免费学习答疑…

课程网址: <http://www.edatop.com/peixun/cst/24.html>

## HFSS 天线设计培训课程套装

套装包含 6 门视频课程和 1 本图书, 课程从基础讲起, 内容由浅入深, 理论介绍和实际操作讲解相结合, 全面系统的讲解了 HFSS 天线设计的全过程。是国内最全面、最专业的 HFSS 天线设计课程, 可以帮助您快速学习掌握如何使用 HFSS 设计天线, 让天线设计不再难…

课程网址: <http://www.edatop.com/peixun/hfss/122.html>

## 13.56MHz NFC/RFID 线圈天线设计培训课程套装

套装包含 4 门视频培训课程, 培训将 13.56MHz 线圈天线设计原理和仿真设计实践相结合, 全面系统地讲解了 13.56MHz 线圈天线的工作原理、设计方法、设计考量以及使用 HFSS 和 CST 仿真分析线圈天线的具体操作, 同时还介绍了 13.56MHz 线圈天线匹配电路的设计和调试。通过该套课程的学习, 可以帮助您快速学习掌握 13.56MHz 线圈天线及其匹配电路的原理、设计和调试…

详情浏览: <http://www.edatop.com/peixun/antenna/116.html>

## 我们的课程优势:

- ※ 成立于 2004 年, 10 多年丰富的行业经验,

- ※ 一直致力并专注于微波射频和天线设计工程师的培养, 更了解该行业对人才的要求

- ※ 经验丰富的一线资深工程师讲授, 结合实际工程案例, 直观、实用、易学

## 联系我们:

- ※ 易迪拓培训官网: <http://www.edatop.com>

- ※ 微波 EDA 网: <http://www.mweda.com>

- ※ 官方淘宝店: <http://shop36920890.taobao.com>