## 电磁兼容性和 PCB 设计约束

## 中国电磁兼容网 http://www.emcchina.org

PCB 布线对 PCB 的电磁兼容性影响很大,为了使 PCB 上的电路正常工作,应根据本文所述的约束条件来优化布线以及元器件/接头和某些 IC 所用去耦电路的布局

## PCB 材料的选择

通过合理选择 PCB 的材料和印刷线路的布线路径,可以做出对其它线路耦合低的传输线。 当传输线导体间的距离 d 小于同其它相邻导体间的距离时,就能做到更低的耦合,或者更小的串扰(见《电子工程专辑》2000年第1期"应用指南")。

设计之前,可根据下列条件选择最经济的 PCB 形式:

对 EMC 的要求

- ·印制板的密集程度

- ·组装与生产的能力

- ·CAD 系统能力

- ·设计成本

- ·PCB 的数量

- ·电磁屏蔽的成本

当采用非屏蔽外壳产品结构时,尤其要注意产品的整体成本/元器件封装/管脚样式、PCB形式、电磁场屏蔽、构造和组装),在许多情况下,选好合适的 PCB形式可以不必在塑胶外壳里加入金属屏蔽盒。

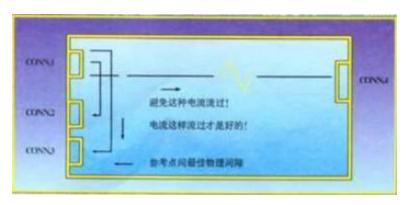

为了提高高速模拟电路和所有数字应用的抗扰性同时减少有害辐射,需要用到传输线技术。根据输出信号的转换情况, $S-V_{CC}$ 、 $S-V_{EE}$  及  $V_{EE}$ - $V_{CC}$ 之间的传输线需要表示出来,如图

# 1 所示。

信号电流由电路输出级的对称性决定。对 MOS 而言  $I_{OL} = I_{OH}$ ,而对 TTL 而言  $I_{OL} > I_{OH}$ .

| 功能/逻辑类型  | $Z_{O}(\Omega)$ |

|----------|-----------------|

| 电源 (典型值) | <<10            |

| ECL 逻辑   | 50              |

| TTL 逻辑   | 100             |

| HC(T)逻辑  | 200             |

表 1: 几种信号路径的传输线阻抗 Zo。

逻辑器件类型和功能上的原因决定了传输线典型特征阻抗  $Z_0$ ,如表 1 所示。

图 1:显示三种特定传输线的(数字)IC之间典型互联图

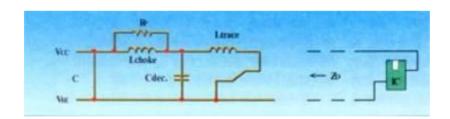

图 2: IC 去耦电路。

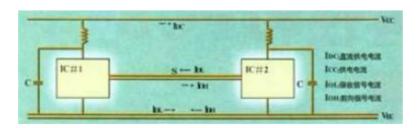

# 图 3: 正确的去耦电路块

表 2: 去耦电容 Cdec..的推荐值。

| 逻辑电路噪声容限 |      | Di/dt | Cdec |      |

|----------|------|-------|------|------|

| volt     |      | mA ns | nF   |      |

| COMS(5V) | 1.75 | 2     | 100  | 0.5  |

| TTL-LS   | 0.4  | 50    | 10   | 5.0  |

| TTL-F    | 0.4  | 50    | 2-3  | 22.0 |

| НСТ      | 0. 7 | 50    | 2-3  | 12.8 |

| HC(5V)   | 12   | 50    | 2-3  | 7.5  |

| ACT      | 17   | 175   | 1-2  | 35.0 |

|          |      |       |      |      |

## 信号线路及其信号回路

传送信号的线路要与其信号回路尽可能靠近,以防止这些线路包围的环路区域产生辐射, 并降低环路感应电压的磁化系数。

一般情况下,当两条线路间的距离等于线宽时,耦合系数大约为 0.5 到 0.6,线路的有效自感应从  $1\mu H/m$  降到 0.4- $0.5\mu$  H/m.

这就意味着信号回路电流的 40%到 50% 自由地就流向了 PCB 上其它线路。

对两个(子)电路块间的每一块信号路径,无论是模拟的还是数字的,都可以用三种传输 线来表示,如图1所示,其中阻抗可从表1得到。

TTL逻辑电路由高电平向低电平转换时,吸收电流会大于电源电流以,在这种情况下,通常将传输线定义在 Vcc 和 S 之间,而不是 VEE 和 S 之间。通过采用铁氧体磁环可完全控

制信号线和信号回路线上的电流。

在平行导体情况下,传输线的特征阻抗会因为铁氧体而受到影响,而在同轴电缆的情况下, 铁氧体只会对电缆的外部参数有影响。

因此,相邻线路应尽可能细,而上下排列的则相反(通常距离小于 1.5mm/双层板中环氧树脂的厚度)。布线应使每条信号线和它的信号回路尽可能靠近(信号和电源布线均适用)。如果传输线导体间耦合不够,可采用铁氧体磁环。

## IC 的去耦

通常 IC 仅通过电容来达到去耦的目的,因为电容并不理想,所以会产生谐振。在大于谐振频率时,电容表现得象个电感,这就意味着 di/dt 受到了限制。电容的值由 IC 管脚间允许的电源电压波动来决定,根据资深设计人员的实践经验,电压波动应小于信号线最坏状况下的噪声容限的 25%,下面公式可计算出每种逻辑系列输出门电路的最佳去耦电容值:

### $I=c\cdot dV/dt$

表 2 给出了几种逻辑系列门电路在最坏情况下信号线噪声的容限,同时还给出每个输出级应加的去耦电容 Cdec.的推荐值。

图 4: PCB 上环路的辐射

对快速逻辑电路来说,如果去耦电容含有很大串联电感(这种电感也许是由电容的结构、长的连接线或 PCB 的印制线路造成的),电容的值可能不再有用。这时则需要在尽可能靠近 IC 管脚的地方加入另外一个小陶瓷电容(100-100Pf),与"LF-"去耦电容并联。陶瓷电容的谐振频率(包括到 IC 电源管脚的线路长度)应高于逻辑电路的带宽[1/(π.τr)],其中,τr 是逻辑电路中电压的上升时间。

如果每个 IC 都有去耦电容,信号回路电流可选择最方便的路径, $V_{EE}$  或者  $V_{CC}$ ,这可以由传送信号的线路和电源线路间的互耦来决定。

在两个去耦电容(每个 IC 一个)和电源线路形成的电感 Ltrace 之间,会形成串联谐振电路,这种谐振只可以发生在低频(<1MHz)或谐振电路的 Q 值较低(<2)的情况下。

通过将高射频损耗扼流线圈串联在 Vcc 网络和要去耦的 IC 中,可使谐振频率保持在 1MHz 以下,如果射频损耗太低可通过并联或串联电阻来补偿(图 2)。

扼流线圈应该总是采用封闭的内芯,否则它会成为一个射频发射器或磁场铁感应器。

例如:  $1MHz*1\mu Hz$   $Z_1=6.28\Omega$   $Rs=3.14\Omega$  Q<2  $Rp=12.56\Omega$

大于谐振频率时,"传输线"的特征阻抗  $Z_0$ (此时将 IC 的阻抗看作电源负载)等于:  $Z_0$  = (Ltrace/Cdecoupling) 的平方根

去耦电容的串联电感和连接线路的电感对射频电源电流分配没有多大影响,比如采用了一个 1μH 扼流线圈的情况。但它仍然会决定 IC 电源管脚间的电压波动,表 3 给出了电源信噪容限为 25%时,推荐的最大电感值 Ltrace.根据图 2 所建议的去耦方法,两个 IC 间的传输线数量从 3 条减少到了 1 条(见图 3)。

因此,对每个IC采用适当的去耦方法:Lchoke+Cdec.电路块间就只需定义一条传输线。

对于 tr<3ns 的高速逻辑电路,与去耦电容串联的全部电感必须要很低(见表 3)。与电源管脚串联的 50mm 印制线路相当于一个 50hH 电感,与输出端的负载(典型值为 50pF)一起决定了最小上升时间为 3.2ns。如要求更快的上升时间,就必须缩短去耦电容的引脚。长度(最好无引脚)并缩短 IC 封装的引脚,例如可以用 IC 去耦电容,或最好采用将(电源)管脚在中间的 IC 与很小的 3E 间距(DIL)无引脚陶瓷电容相结合等方法来达到这一目的,也可以用带电源层和接地层的多层电路板。另外采用电源管脚在中间的 SO 封装还可得到进一步的改善。但是,使用快速逻辑电路时,应采用多层电路板。

## 根据辐射决定环路面积

无终点传输线的反射情况决定了线路的最大长度。由于对产品的 EM 辐射有强制性要求,

因此环路区域的面积和线路长度都受到限制,如果采用非屏蔽外壳,这种限制将直接由 PCB 来实现。

注意:如果在异步逻辑电路设计中采用串联端接负载,必须要注意会出现准稳性,特别是对称逻辑输入电路无法确定输入信号是高还是低,而且可能会导致非定义输出情况。

表 3: 允许的(电源)串联电感。

| 逻辑电路噪声容限 |      | Di/dt |     | Cdec |

|----------|------|-------|-----|------|

| volt     |      | mA ns |     | nF   |

| COMS(5V) | 1.75 | 2     | 100 | 0.5  |

| TTL-LS   | 0.4  | 50    | 10  | 5.0  |

| TTL-F    | 0.4  | 50    | 2-3 | 22.0 |

| НСТ      | 1. 7 | 50    | 2-3 | 12.8 |

| HC(5V)   | 1. 2 | 50    | 2-3 | 7.5  |

| ACT      | 1. 7 | 175   | 1-2 | 35.0 |

|          |      |       |     |      |

表 4: 无端接负载或串联端接负载允许的线路长度。

| 逻辑电路噪声   | 容限   | df  | 最大线路长度  |        |

|----------|------|-----|---------|--------|

| valt     |      | ns  | 无端接负载   | 串联端接负载 |

| COMS(5V) | 1.75 | 100 | 14.3 -1 |        |

| TTL-LS   | 0.4  | 10  | 0.4 0.5 |        |

| TTL-F    | 0.4  | 2-3 | 0.08    | 0. 15  |

| НСТ    | 0.7  | 2-3 | 0.14 | 0  |  |

|--------|------|-----|------|----|--|

| HC(5V) | 1. 2 | 2-3 | 0.24 | -1 |  |

| ACT    | 1. 7 | 1-2 | 0.18 | -1 |  |

|        |      |     |      |    |  |

图 3: 正确的去耦电路块。

对于频域中的逻辑信号,频谱的电流幅度在超出逻辑信号带宽(=1/π.τr)的频率上与频率的平方成反比。用角频率表示,环路的辐射阻抗仍随频率平方成正比。因而可计算出最大的环路面积,它由时钟速率或重复速率、逻辑信号的上升时间或带宽以及时域的电流幅度决定。电流波形由电压波形决定,电流半宽时间约等于电压的上升时间。

电流幅度可用角频率  $(=1/\pi.\tau r)$  表示为:  $I(f)=2.I.\tau r/T$

其中: I=为时域电流幅度; T=为时钟速率的倒数,即周期;

τr 为电压的上升时间,约等于电流半宽时间 τH。

从这一等式可计算出某种逻辑系列电路在某一时钟速率下最大环路面积,表 5 给出了相应的环路面积。最大环路面积由时钟速率、逻辑电路类型(=输出电流)和 PCB 上同时存在的开关环路数量 n 决定。

如果所用的时钟速率超过 30MHz, 就必须要采用多层电路板,在这种情况下,环氧树脂的厚度与层数有关,在 60 至 300μm之间。只有当 PCB上的高速时钟信号的数量有限时,通过采用层到层的线路进行仔细布线,也可在双层板上得到可以接受的结果。

注意: 在这种情况下,如采用普通 DIL 封装,则会超过环路面积的限制,一定要有另外的屏蔽措施和适当的滤波。

表 4: 无端接负载或串联端接负载允许的线路长度

| 逻辑电路类    | dl  | df  | 在不同时钟速率下的最大环路面积(用 mm2 表示) |                     |         |          |

|----------|-----|-----|---------------------------|---------------------|---------|----------|

| 型        | Δ   |     | f=4MHz                    | f=10MHz             | f=30MHz | f=100MHz |

|          | mA  | ns  |                           |                     |         |          |

| COMS(5V) | 2   | 2   | 4.5 10 <sup>6</sup>       | 1.8 10 <sup>6</sup> | _       | -        |

| TTL-LS   | 50  | 50  | 1.8 10 <sup>6</sup>       | 7200                | 2400    | -        |

| TTL-F    | 50  | 50  | 1.8 10 <sup>6</sup>       | 1400                | 480     | 144      |

| НСТ      | 50  | 50  | 1.8 10 <sup>6</sup>       | 1400                | 480     | 144      |

| HC(5V)   | 50  | 50  | 1.8 10 <sup>6</sup>       | 1400                | 480     | 144      |

| ACT      | 175 | 175 | 515                       | 206                 | 69      | 21       |

## 连接头的布局

所有连接到其它面板及部件的连接头必须尽可能相互靠近放置,这样在电缆中传导的共模电流就不会流入 PCB 电路中的线路,另外,PCB 上参考点间的电压降也无法激励(天线)电缆。

为避免这种共模影响,必须使靠近接头的参考地和 PCB 上电路的接地层、接地网格或电路参考地隔开,如果可能,这些接地片应接到产品的金属外壳上。从这个接地片上,只有高阻器件如电感、电阻、簧片继电器和光耦合器可接在两个地之间。所有的接头要尽可能靠近放置,以防止外部电流流过 PCB 上的线路或参考地。

## 电缆及接头的正确选择

电缆的选择由流过电缆的信号幅度和频率成分决定。对于位于产品外部的电缆来说,如果 传送 10kHz 以上时钟速率的数据信号,则一定要用到屏蔽(产品要求),屏蔽部分应在电缆 的两端连接到地(金属外壳产品),这样能确保对电场和磁场都进行屏蔽。

如果用的是分开接地,则应连到"接头地"而不是"电路地"。

如果时钟速率在 10kHz 到 1MHz 之间,并且逻辑电路的上升时间尽可能保持低,将可以得到 80%以上的光覆盖或小于 10Nh/m 的转移阻抗。如果时钟速率超过 1MHz 时,就需要更好的屏蔽电缆。

通常,除同轴电缆外,电缆的屏蔽不应用作为信号回路。

通过在信号输入/输出和地/参考点之间串入无源滤波器以减少射频成分,可以不必采用高质量屏蔽和相应接头。好的屏蔽电缆应配备合适的连接头。

PDF 文件制作: 中国 PCB 技术网

2004-09-08

$\underline{http://www.pcbtech.net}$

http://www.pcbbbs.com

http://www.pcber.net

# 射频和天线设计培训课程推荐

易迪拓培训(www.edatop.com)由数名来自于研发第一线的资深工程师发起成立,致力并专注于微波、射频、天线设计研发人才的培养;我们于2006年整合合并微波EDA网(www.mweda.com),现已发展成为国内最大的微波射频和天线设计人才培养基地,成功推出多套微波射频以及天线设计经典培训课程和ADS、HFSS等专业软件使用培训课程,广受客户好评;并先后与人民邮电出版社、电子工业出版社合作出版了多本专业图书,帮助数万名工程师提升了专业技术能力。客户遍布中兴通讯、研通高频、埃威航电、国人通信等多家国内知名公司,以及台湾工业技术研究院、永业科技、全一电子等多家台湾地区企业。

易迪拓培训课程列表: http://www.edatop.com/peixun/rfe/129.html

# 射频工程师养成培训课程套装

该套装精选了射频专业基础培训课程、射频仿真设计培训课程和射频电路测量培训课程三个类别共 30 门视频培训课程和 3 本图书教材;旨在引领学员全面学习一个射频工程师需要熟悉、理解和掌握的专业知识和研发设计能力。通过套装的学习,能够让学员完全达到和胜任一个合格的射频工程师的要求…

课程网址: http://www.edatop.com/peixun/rfe/110.html

## ADS 学习培训课程套装

该套装是迄今国内最全面、最权威的 ADS 培训教程, 共包含 10 门 ADS 学习培训课程。课程是由具有多年 ADS 使用经验的微波射频与通信系统设计领域资深专家讲解,并多结合设计实例,由浅入深、详细而又全面地讲解了 ADS 在微波射频电路设计、通信系统设计和电磁仿真设计方面的内容。能让您在最短的时间内学会使用 ADS, 迅速提升个人技术能力,把 ADS 真正应用到实际研发工作中去,成为 ADS 设计专家...

课程网址: http://www.edatop.com/peixun/ads/13.html

## HFSS 学习培训课程套装

该套课程套装包含了本站全部 HFSS 培训课程,是迄今国内最全面、最专业的 HFSS 培训教程套装,可以帮助您从零开始,全面深入学习 HFSS 的各项功能和在多个方面的工程应用。购买套装,更可超值赠送 3 个月免费学习答疑,随时解答您学习过程中遇到的棘手问题,让您的 HFSS 学习更加轻松顺畅···

课程网址: http://www.edatop.com/peixun/hfss/11.html

# CST 学习培训课程套装

该培训套装由易迪拓培训联合微波 EDA 网共同推出,是最全面、系统、 专业的 CST 微波工作室培训课程套装, 所有课程都由经验丰富的专家授 课,视频教学,可以帮助您从零开始,全面系统地学习 CST 微波工作的 各项功能及其在微波射频、天线设计等领域的设计应用。且购买该套装, 还可超值赠送3个月免费学习答疑…

# HFSS 天线设计培训课程套装

套装包含6门视频课程和1本图书,课程从基础讲起,内容由浅入深, 理论介绍和实际操作讲解相结合,全面系统的讲解了 HFSS 天线设计的 全过程。是国内最全面、最专业的 HFSS 天线设计课程,可以帮助您快 速学习掌握如何使用 HFSS 设计天线, 让天线设计不再难…

课程网址: http://www.edatop.com/peixun/hfss/122.html

# 13.56MHz NFC/RFID 线圈天线设计培训课程套装

套装包含 4 门视频培训课程,培训将 13.56MHz 线圈天线设计原理和仿 真设计实践相结合,全面系统地讲解了13.56MHz线圈天线的工作原理、 设计方法、设计考量以及使用 HFSS 和 CST 仿真分析线圈天线的具体 操作,同时还介绍了 13.56MHz 线圈天线匹配电路的设计和调试。通过 该套课程的学习,可以帮助您快速学习掌握 13.56MHz 线圈天线及其匹 配电路的原理、设计和调试…

详情浏览: http://www.edatop.com/peixun/antenna/116.html

# 我们的课程优势:

- ※ 成立于 2004年, 10 多年丰富的行业经验,

- ※ 一直致力并专注于微波射频和天线设计工程师的培养,更了解该行业对人才的要求

- ※ 经验丰富的一线资深工程师讲授,结合实际工程案例,直观、实用、易学

## 联系我们:

- ※ 易迪拓培训官网: http://www.edatop.com

- ※ 微波 EDA 网: http://www.mweda.com

- ※ 官方淘宝店: http://shop36920890.taobao.com

易迪拓信训 官方网址: http://www.edatop.com