## Features

- Fully qualified Bluetooth v2.1 + EDR specification system

- Best-in-class Bluetooth radio with 8dBm transmit power and -90dBm receive sensitivity

- 64MIPS Kalimba DSP coprocessor

- 16-bit internal stereo codec: 95dB SNR for DAC

- Low-power 1.5V operation, 1.8V to 3.6V I/O

- Integrated 1.5V and 1.8V linear regulators

- Integrated switch-mode regulator

- Integrated battery charger

- USB, I<sup>2</sup>C and UART with dual-port bypass mode to 4Mbps

- Supports up to 32Mb of external flash memory (8Mb typical requirement)

- Multi-configurable I<sup>2</sup>S, PCM or SPDIF interface

- Enhanced audibility and noise cancellation

- 8 x 8 x 1.2mm, 0.5mm pitch 169-ball TFBGA

- Support for IEEE 802.11 coexistence

- Green (RoHS compliant and no antimony or halogenated flame retardants)

## General Description

The BlueCore®5-Multimedia External is a product from CSR's Connectivity Centre. It is a single-chip radio and baseband IC for Bluetooth 2.4GHz systems.

BlueCore5-Multimedia External interfaces up to 32Mb of external flash memory. When used with the CSR Bluetooth stack, it provides a fully compliant Bluetooth v2.1 + EDR specification system for data and voice.

BlueCore5-Multimedia External contains the Kalimba DSP coprocessor with double the MIPS of BlueCore3-Multimedia External, supporting enhanced audio applications.

BlueCore5-Multimedia External is designed to reduce the number of external components required which ensures production costs are minimised. The device incorporates auto-calibration and BIST routines to simplify development, type approval and production test.

## BlueCore®5-Multimedia External

Fully Qualified Single-chip

Bluetooth® v2.1 + EDR System

Production Information

BC57E687C

Issue 4

# BlueCore5-Multimedia External (BC57E687C) Data Sheet

## Applications

- High-quality stereo wireless headsets

- High-quality mono headsets

- Hands-free car kits

- Wireless speakers

- VoIP handsets

- Analogue and USB multimedia dongles

- Bluetooth automotive wireless gateways

To improve the performance of both Bluetooth and 802.11 b/g co-located systems, dedicated hardware has been implemented to support coexistence features including support for CSR's Unity coexistence scheme.

For radio performance over temperature and additional performance information refer to the *BlueCore®5-Multimedia External Performance Specification*.

## Document History

| Revision | Date      | Change Reason                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Issue 1  | 10 JUL 08 | Original publication of document as BlueCore5-Multimedia External changed to revision C silicon.<br>Data sheet replaces revision B silicon, document number CS-101568-DSP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Issue 2  | 15 JUL 08 | USB interface updated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Issue 3  | 08 MAY 09 | Internal release only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Issue 4  | 09 FEB 10 | SPI interface updated.<br>High-voltage linear regulator description updated.<br>Electrical Characteristics updates: <ul style="list-style-type: none"><li>■ Correction of the units for the stereo codec ADC mic mode impedance</li><li>■ Reworded output current parameter in all linear regulator electrical characterisation tables to remove ambiguity</li><li>■ ESD precautions section moved to Electrical Characteristics</li></ul> Tape dimensions added.<br>Status Information updated.<br>Power Consumption conditions updated.<br>Various editorial updates.<br>If you have any comments about this document, email <a href="mailto:comments@csr.com">comments@csr.com</a> giving number, title and section with your feedback. |

## Status Information

The status of this Data Sheet is **Production Information**.

CSR Product Data Sheets progress according to the following format:

### Advance Information

Information for designers concerning CSR product in development. All values specified are the target values of the design. Minimum and maximum values specified are only given as guidance to the final specification limits and must not be considered as the final values.

All detailed specifications including pinouts and electrical specifications may be changed by CSR without notice.

### Pre-production Information

Pinout and mechanical dimension specifications finalised. All values specified are the target values of the design. Minimum and maximum values specified are only given as guidance to the final specification limits and must not be considered as the final values.

All electrical specifications may be changed by CSR without notice.

### Production Information

Final Data Sheet including the guaranteed minimum and maximum limits for the electrical specifications.

Production Data Sheets supersede all previous document versions.

### Life Support Policy and Use in Safety-critical Applications

CSR's products are not authorised for use in life-support or safety-critical applications. Use in such applications is done at the sole discretion of the customer. CSR will not warrant the use of its devices in such applications.

### CSR Green Semiconductor Products and RoHS Compliance

BlueCore5-Multimedia External devices meet the requirements of Directive 2002/95/EC of the European Parliament and of the Council on the Restriction of Hazardous Substance (RoHS).

BlueCore5-Multimedia External devices are also free from halogenated or antimony trioxide-based flame retardants and other hazardous chemicals. For more information, see CSR's *Environmental Compliance Statement for CSR Green Semiconductor Products*.

### Trademarks, Patents and Licences

Unless otherwise stated, words and logos marked with <sup>TM</sup> or <sup>®</sup> are trademarks registered or owned by CSR plc or its affiliates. Bluetooth <sup>®</sup> and the Bluetooth <sup>®</sup> logos are trademarks owned by Bluetooth <sup>®</sup> SIG, Inc. and licensed to CSR. Other products, services and names used in this document may have been trademarked by their respective owners.

The publication of this information does not imply that any license is granted under any patent or other rights owned by CSR plc and/or its affiliates.

CSR reserves the right to make technical changes to its products as part of its development programme.

While every care has been taken to ensure the accuracy of the contents of this document, CSR cannot accept responsibility for any errors.

Refer to [www.csrsupport.com](http://www.csrsupport.com) for compliance and conformance to standards information.

No statements or representations in this document are to be construed as advertising, marketing, or offering for sale in the United States imported covered products subject to the Cease and Desist Order issued by the U.S. International Trade Commission in its Investigation No. 337-TA-602. Such products include SiRFstarIII chips that operate with SiRF software that supports SiRFInstantFix, and/or SiRFLoc servers, or contains SyncFreeNav functionality.

## Contents

|       |                                                                   |    |

|-------|-------------------------------------------------------------------|----|

| 1     | Device Details .....                                              | 10 |

| 2     | Functional Block Diagram .....                                    | 11 |

| 3     | Package Information .....                                         | 12 |

| 3.1   | Pinout Diagram .....                                              | 12 |

| 3.2   | Device Terminal Functions .....                                   | 13 |

| 3.3   | Package Dimensions .....                                          | 21 |

| 3.4   | PCB Design and Assembly Considerations .....                      | 22 |

| 3.5   | Typical Solder Reflow Profile .....                               | 22 |

| 4     | Bluetooth Modem .....                                             | 23 |

| 4.1   | RF Ports .....                                                    | 23 |

| 4.1.1 | RF_N and RF_P .....                                               | 23 |

| 4.2   | RF Receiver .....                                                 | 23 |

| 4.2.1 | Low Noise Amplifier .....                                         | 23 |

| 4.2.2 | RSSI Analogue to Digital Converter .....                          | 23 |

| 4.3   | RF Transmitter .....                                              | 23 |

| 4.3.1 | IQ Modulator .....                                                | 23 |

| 4.3.2 | Power Amplifier .....                                             | 24 |

| 4.3.3 | Transmit RF Power Control for Class 1 Applications (TX_PWR) ..... | 24 |

| 4.4   | Bluetooth Radio Synthesiser .....                                 | 25 |

| 4.5   | Baseband .....                                                    | 25 |

| 4.5.1 | Burst Mode Controller .....                                       | 25 |

| 4.5.2 | Physical Layer Hardware Engine .....                              | 25 |

| 4.6   | Basic Rate Modem .....                                            | 25 |

| 4.7   | Enhanced Data Rate Modem .....                                    | 25 |

| 5     | Clock Generation .....                                            | 27 |

| 5.1   | Clock Architecture .....                                          | 27 |

| 5.2   | Input Frequencies and PS Key Settings .....                       | 27 |

| 5.3   | External Reference Clock .....                                    | 28 |

| 5.3.1 | Input (XTAL_IN) .....                                             | 28 |

| 5.3.2 | XTAL_IN Impedance in External Mode .....                          | 28 |

| 5.3.3 | Clock Start-up Delay .....                                        | 28 |

| 5.3.4 | Clock Timing Accuracy .....                                       | 28 |

| 5.4   | Crystal Oscillator (XTAL_IN, XTAL_OUT) .....                      | 29 |

| 5.4.1 | Load Capacitance .....                                            | 30 |

| 5.4.2 | Frequency Trim .....                                              | 30 |

| 5.4.3 | Transconductance Driver Model .....                               | 31 |

| 5.4.4 | Negative Resistance Model .....                                   | 31 |

| 5.4.5 | Crystal PS Key Settings .....                                     | 31 |

| 6     | Bluetooth Stack Microcontroller .....                             | 32 |

| 6.1   | Programmable I/O Ports, PIO and AIO .....                         | 32 |

| 6.2   | TCXO Enable OR Function .....                                     | 32 |

| 6.3   | WLAN Coexistence Interface .....                                  | 33 |

| 7     | Kalimba DSP .....                                                 | 34 |

| 8     | Memory Interface and Management .....                             | 35 |

| 8.1   | Memory Management Unit .....                                      | 35 |

| 8.2   | System RAM .....                                                  | 35 |

| 8.3   | Kalimba DSP RAM .....                                             | 35 |

| 8.4   | External Memory Driver .....                                      | 35 |

| 8.5   | External Flash Memory (32Mb) .....                                | 35 |

| 8.6   | Off-chip Program Memory .....                                     | 35 |

|           |                                                  |           |

|-----------|--------------------------------------------------|-----------|

| 8.6.1     | Minimum Flash Specification .....                | 36        |

| 8.6.2     | Common Flash Interface .....                     | 36        |

| 8.6.3     | Virtual Machine Requirements .....               | 37        |

| 8.6.4     | Memory Timing .....                              | 38        |

| <b>9</b>  | <b>Serial Interfaces .....</b>                   | <b>40</b> |

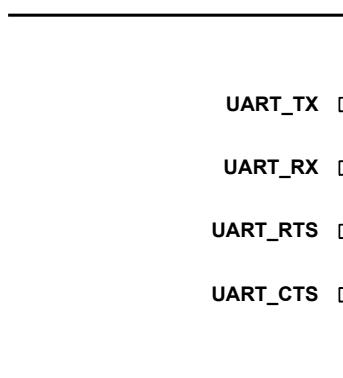

| 9.1       | UART Interface .....                             | 40        |

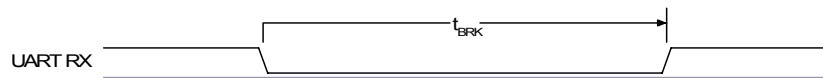

| 9.1.1     | UART Configuration While Reset is Active .....   | 41        |

| 9.1.2     | UART Bypass Mode .....                           | 42        |

| 9.1.3     | Current Consumption in UART Bypass Mode .....    | 42        |

| 9.2       | USB Interface .....                              | 42        |

| 9.3       | Programming and Debug Interface .....            | 43        |

| 9.3.1     | Instruction Cycle .....                          | 43        |

| 9.3.2     | Multi-slave Operation .....                      | 43        |

| 9.4       | I <sup>2</sup> C Interface .....                 | 43        |

| 9.4.1     | Software I <sup>2</sup> C Interface .....        | 43        |

| 9.4.2     | Bit-serialiser Interface .....                   | 44        |

| <b>10</b> | <b>Audio Interface .....</b>                     | <b>45</b> |

| 10.1      | Audio Input and Output .....                     | 45        |

| 10.2      | Stereo Audio Codec Interface .....               | 45        |

| 10.2.1    | Stereo Audio Codec Block Diagram .....           | 46        |

| 10.2.2    | Stereo Codec Set-up .....                        | 46        |

| 10.2.3    | ADC .....                                        | 47        |

| 10.2.4    | ADC Sample Rate Selection .....                  | 47        |

| 10.2.5    | ADC Digital Gain .....                           | 47        |

| 10.2.6    | ADC Analogue Gain .....                          | 47        |

| 10.2.7    | DAC .....                                        | 48        |

| 10.2.8    | DAC Sample Rate Selection .....                  | 48        |

| 10.2.9    | DAC Digital Gain .....                           | 48        |

| 10.2.10   | DAC Analogue Gain .....                          | 49        |

| 10.2.11   | IEC 60958 Interface .....                        | 49        |

| 10.2.12   | Microphone Input .....                           | 50        |

| 10.2.13   | Line Input .....                                 | 53        |

| 10.2.14   | Output Stage .....                               | 54        |

| 10.2.15   | Mono Operation .....                             | 55        |

| 10.2.16   | Side Tone .....                                  | 55        |

| 10.2.17   | Integrated Digital Filter .....                  | 55        |

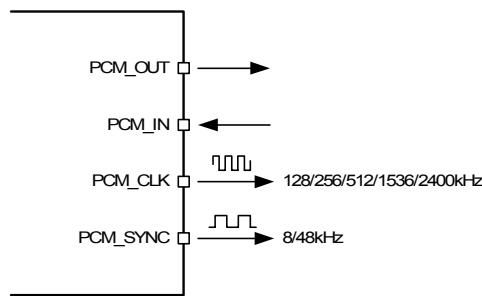

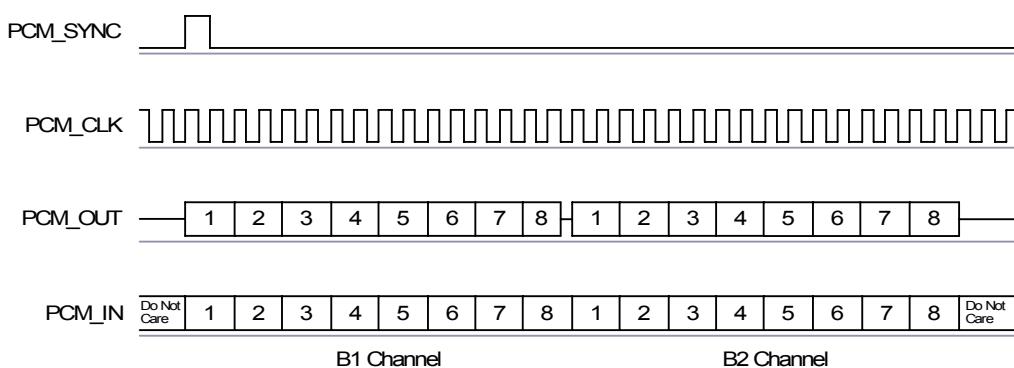

| 10.3      | PCM Interface .....                              | 56        |

| 10.3.1    | PCM Interface Master/Slave .....                 | 56        |

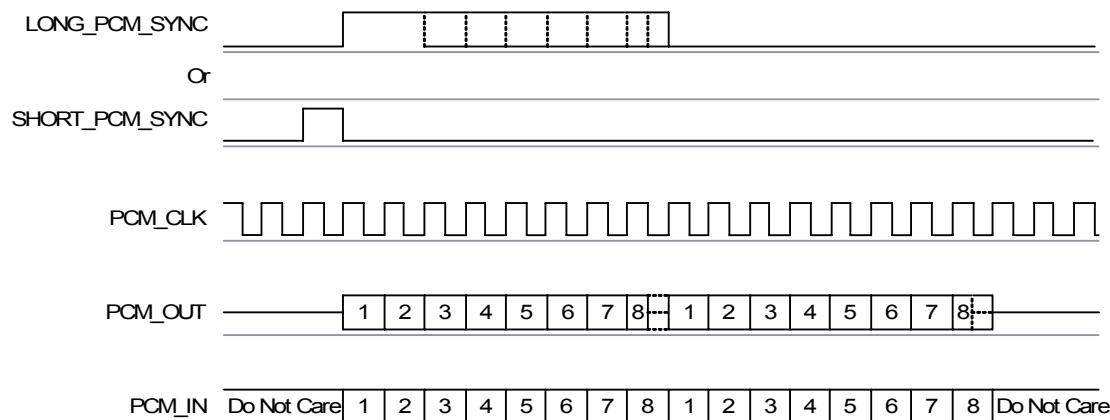

| 10.3.2    | Long Frame Sync .....                            | 57        |

| 10.3.3    | Short Frame Sync .....                           | 57        |

| 10.3.4    | Multi-slot Operation .....                       | 58        |

| 10.3.5    | GCI Interface .....                              | 58        |

| 10.3.6    | Slots and Sample Formats .....                   | 59        |

| 10.3.7    | Additional Features .....                        | 59        |

| 10.3.8    | PCM Timing Information .....                     | 60        |

| 10.3.9    | PCM_CLK and PCM_SYNC Generation .....            | 63        |

| 10.3.10   | PCM Configuration .....                          | 63        |

| 10.4      | Digital Audio Interface (I <sup>2</sup> S) ..... | 65        |

| <b>11</b> | <b>Power Control and Regulation .....</b>        | <b>70</b> |

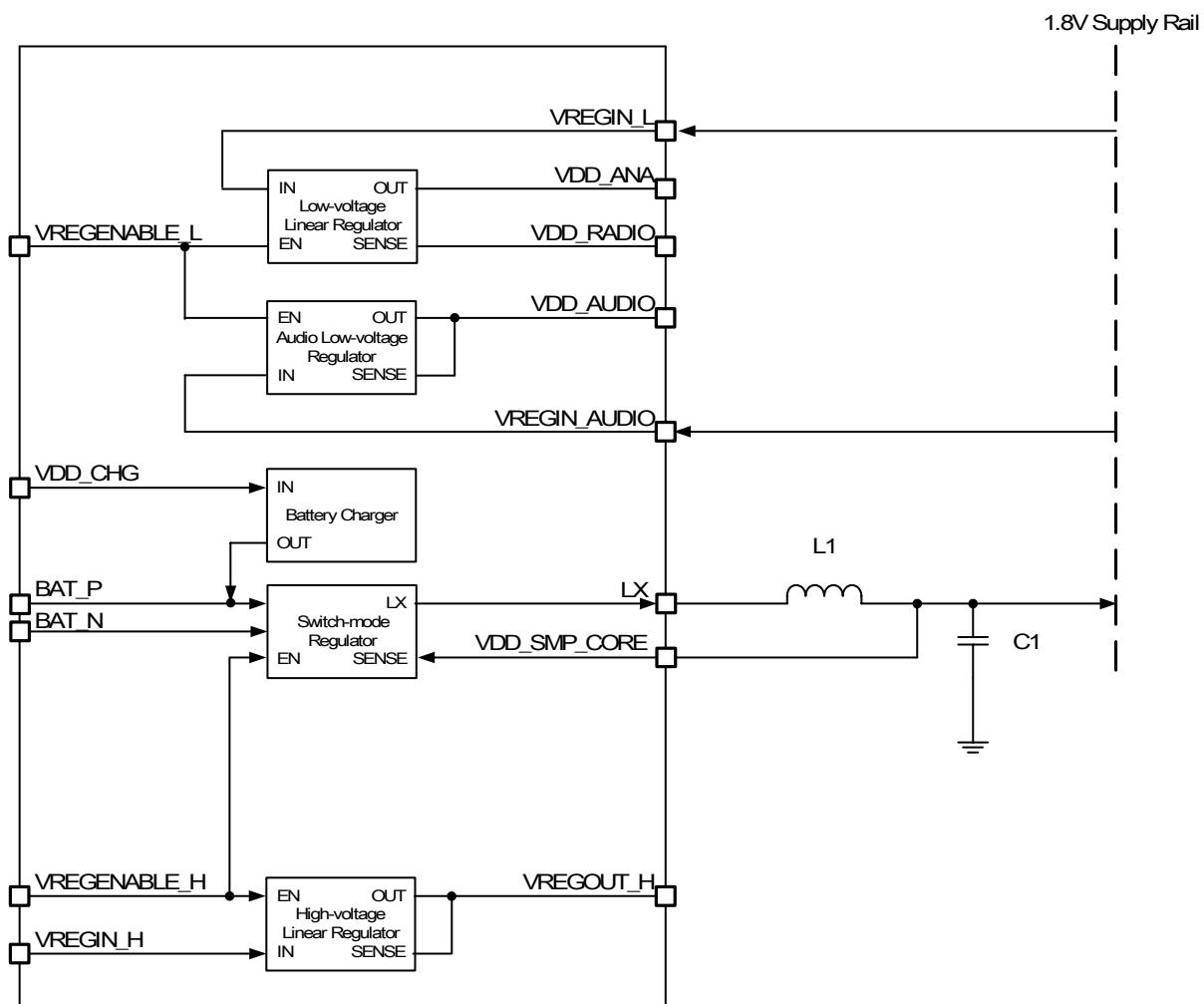

| 11.1      | Power Sequencing .....                           | 70        |

| 11.2      | External Voltage Source .....                    | 71        |

| 11.3      | Switch-mode Regulator .....                      | 71        |

| 11.4      | High-voltage Linear Regulator .....              | 71        |

| 11.5      | Low-voltage Linear Regulator .....               | 71        |

|         |                                                                       |     |

|---------|-----------------------------------------------------------------------|-----|

| 11.6    | Low-voltage Audio Linear Regulator .....                              | 72  |

| 11.7    | Voltage Regulator Enable Pins .....                                   | 72  |

| 11.8    | Battery Charger .....                                                 | 72  |

| 11.9    | LED Drivers .....                                                     | 73  |

| 11.10   | Reset, RST# .....                                                     | 74  |

| 11.10.1 | Digital Pin States on Reset .....                                     | 74  |

| 11.10.2 | Status after Reset .....                                              | 75  |

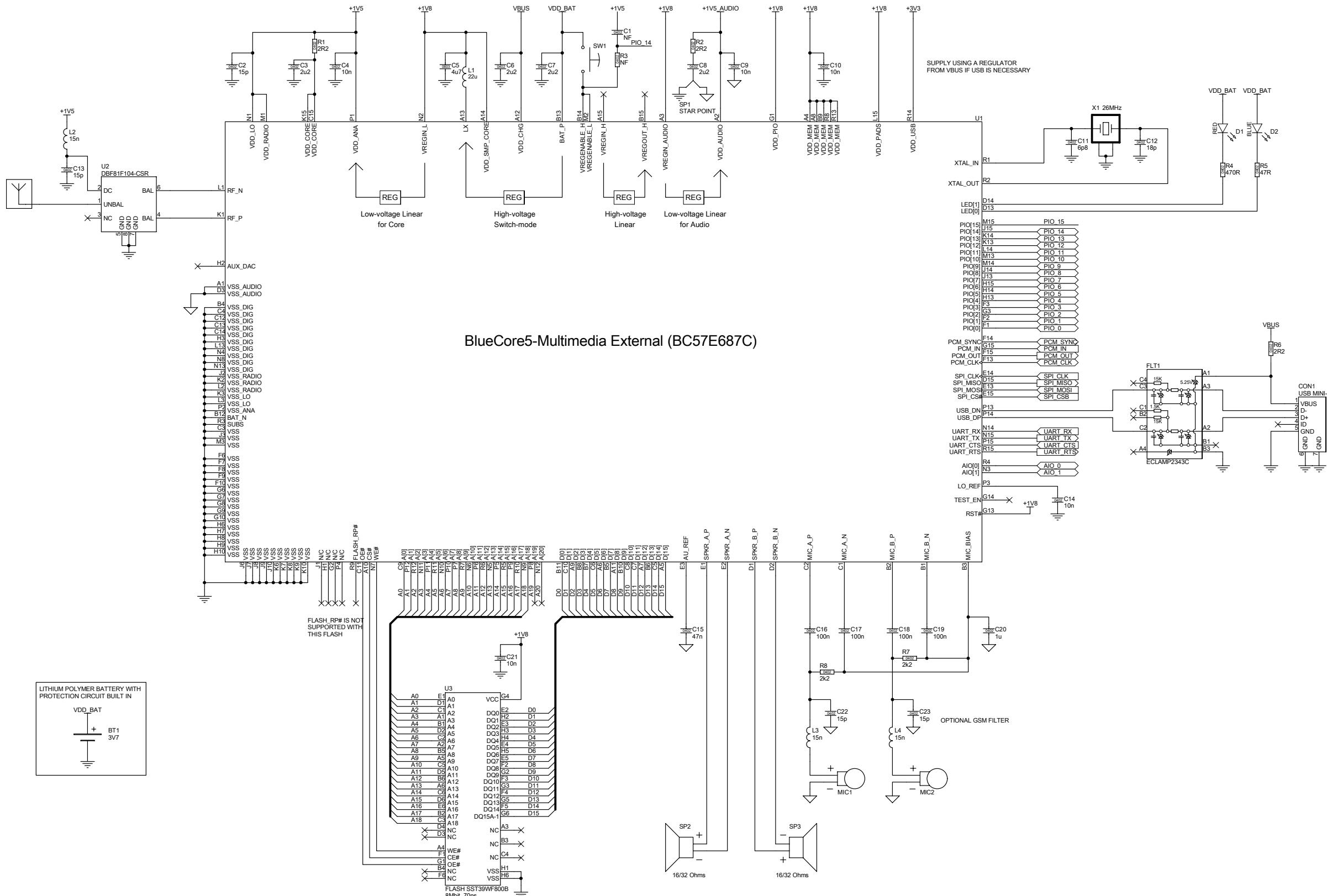

| 12      | <b>Example Application Schematic</b> .....                            | 76  |

| 13      | <b>Electrical Characteristics</b> .....                               | 77  |

| 13.1    | Absolute Maximum Ratings .....                                        | 77  |

| 13.2    | Recommended Operating Conditions .....                                | 77  |

| 13.3    | Input/Output Terminal Characteristics .....                           | 78  |

| 13.3.1  | High-voltage Linear Regulator .....                                   | 78  |

| 13.3.2  | Low-voltage Linear Regulator .....                                    | 79  |

| 13.3.3  | Low-voltage Linear Audio Regulator .....                              | 80  |

| 13.3.4  | Reset .....                                                           | 81  |

| 13.3.5  | Regulator Enable .....                                                | 81  |

| 13.3.6  | Switch-mode Regulator .....                                           | 82  |

| 13.3.7  | Battery Charger .....                                                 | 83  |

| 13.3.8  | Digital Terminals .....                                               | 84  |

| 13.3.9  | LED Driver Pads .....                                                 | 85  |

| 13.3.10 | USB .....                                                             | 85  |

| 13.3.11 | Auxiliary ADC .....                                                   | 86  |

| 13.3.12 | Auxiliary DAC .....                                                   | 86  |

| 13.3.13 | Clocks .....                                                          | 87  |

| 13.3.14 | Stereo Codec: Analogue to Digital Converter .....                     | 88  |

| 13.3.15 | Stereo Codec: Digital to Analogue Converter .....                     | 89  |

| 13.4    | ESD Precautions .....                                                 | 89  |

| 14      | <b>Power Consumption</b> .....                                        | 90  |

| 14.1    | Kalimba DSP Typical Average Current Consumption .....                 | 91  |

| 14.2    | Typical Peak Current at 20°C .....                                    | 91  |

| 14.3    | Conditions .....                                                      | 91  |

| 15      | <b>CSR Green Semiconductor Products and RoHS Compliance</b> .....     | 92  |

| 15.1    | RoHS Statement .....                                                  | 92  |

| 15.1.1  | List of Restricted Materials .....                                    | 92  |

| 16      | <b>CSR Synergy and Bluetooth Software Stack</b> .....                 | 93  |

| 16.1    | BlueCore HCI Stack .....                                              | 93  |

| 16.1.1  | Key Features of the HCI Stack: Standard Bluetooth Functionality ..... | 93  |

| 16.1.2  | Key Features of the HCI Stack: Extra Functionality .....              | 95  |

| 16.2    | Host-Side Software .....                                              | 95  |

| 16.3    | CSR Development Systems .....                                         | 95  |

| 16.4    | eXtension .....                                                       | 95  |

| 17      | <b>Ordering Information</b> .....                                     | 96  |

| 18      | <b>Tape and Reel Information</b> .....                                | 97  |

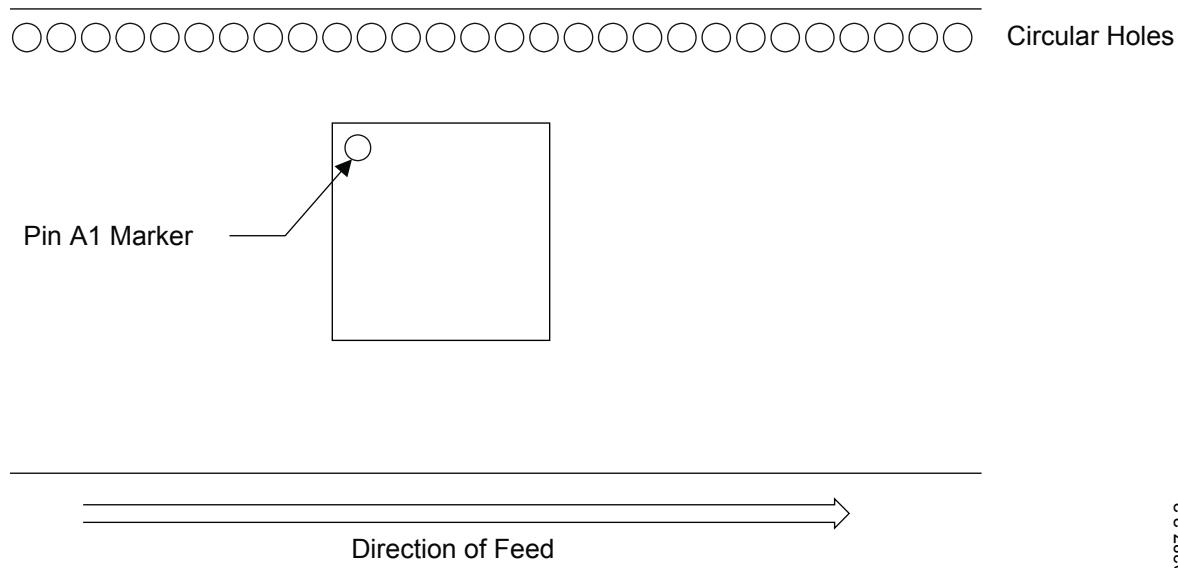

| 18.1    | Tape Orientation .....                                                | 97  |

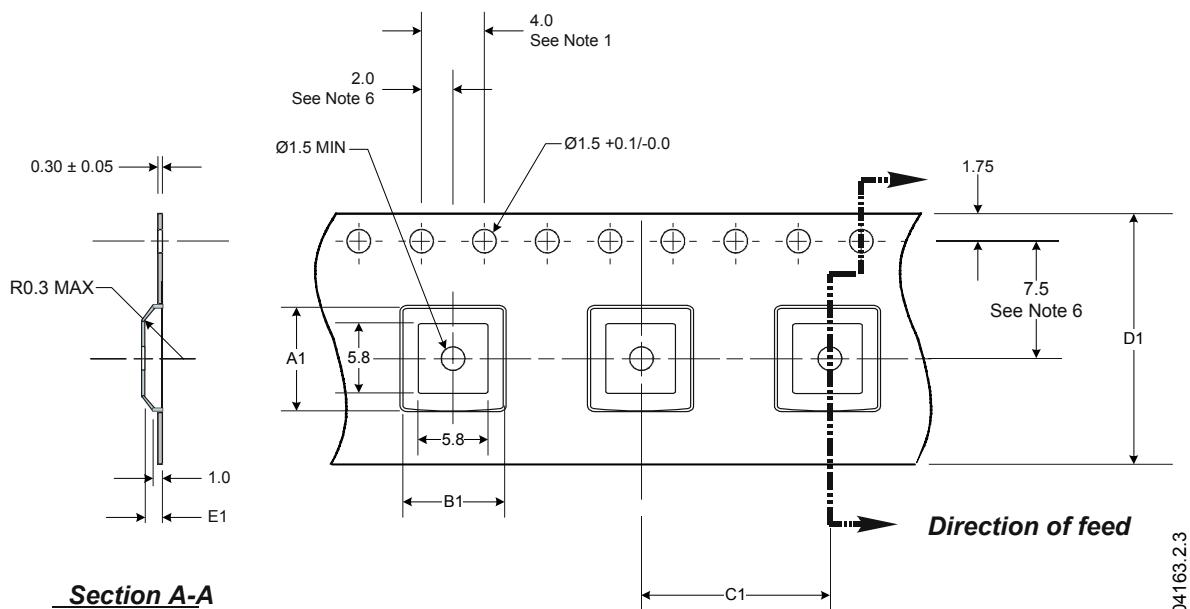

| 18.2    | Tape Dimensions .....                                                 | 98  |

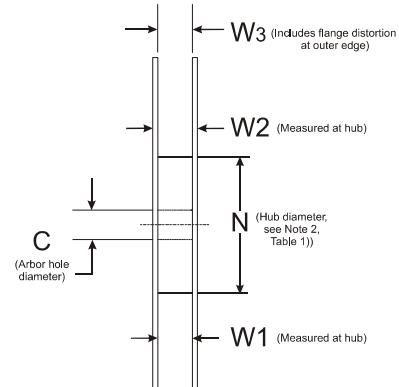

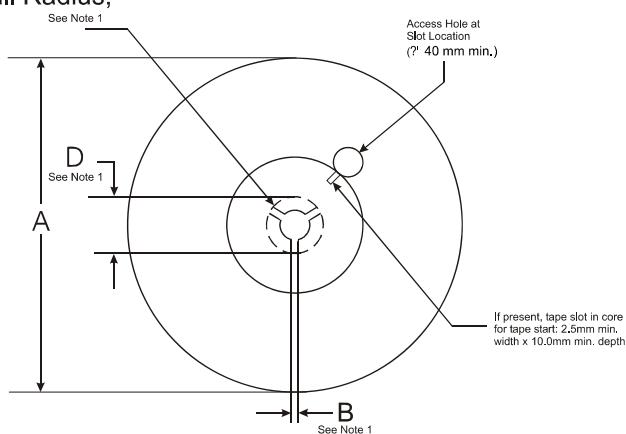

| 18.3    | Reel Information .....                                                | 99  |

| 18.4    | Moisture Sensitivity Level .....                                      | 99  |

| 19      | <b>Document References</b> .....                                      | 100 |

|         | <b>Terms and Definitions</b> .....                                    | 101 |

## List of Figures

|              |                                                                       |    |

|--------------|-----------------------------------------------------------------------|----|

| Figure 2.1   | Functional Block Diagram .....                                        | 11 |

| Figure 3.1   | Device Pinout .....                                                   | 12 |

| Figure 3.2   | 169-ball TFBGA Package Dimensions .....                               | 21 |

| Figure 4.1   | Simplified Circuit RF_N and RF_P .....                                | 23 |

| Figure 4.2   | Internal Power Ramping .....                                          | 24 |

| Figure 4.3   | BDR and EDR Packet Structure .....                                    | 26 |

| Figure 5.1   | Clock Architecture .....                                              | 27 |

| Figure 5.2   | TCXO Clock Accuracy .....                                             | 29 |

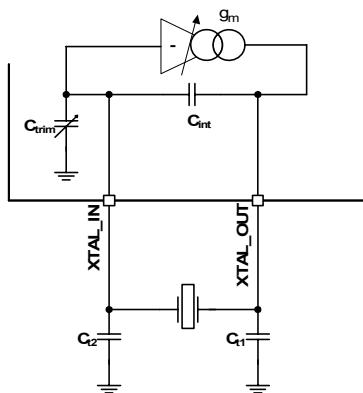

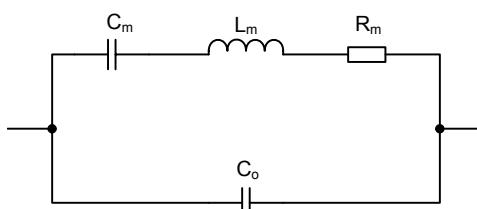

| Figure 5.3   | Crystal Driver Circuit .....                                          | 29 |

| Figure 5.4   | Crystal Equivalent Circuit .....                                      | 29 |

| Figure 6.1   | Example TCXO Enable OR Function .....                                 | 32 |

| Figure 7.1   | Kalimba DSP Interface to Internal Functions .....                     | 34 |

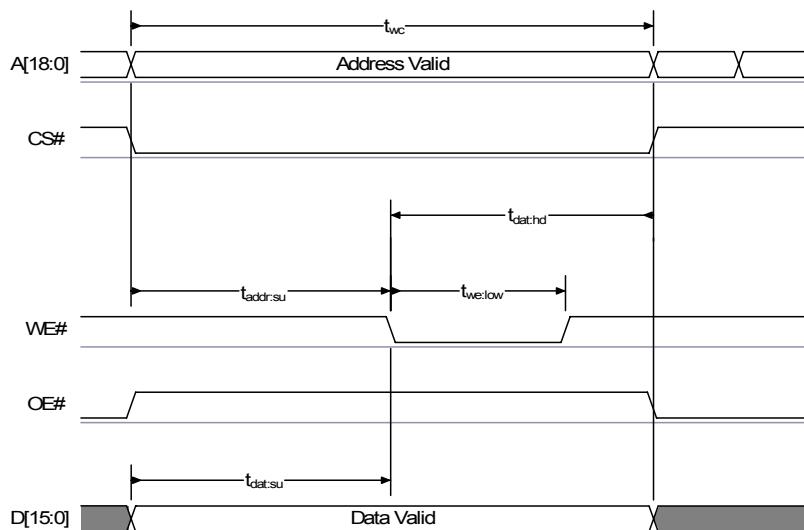

| Figure 8.1   | Memory Write Cycle .....                                              | 38 |

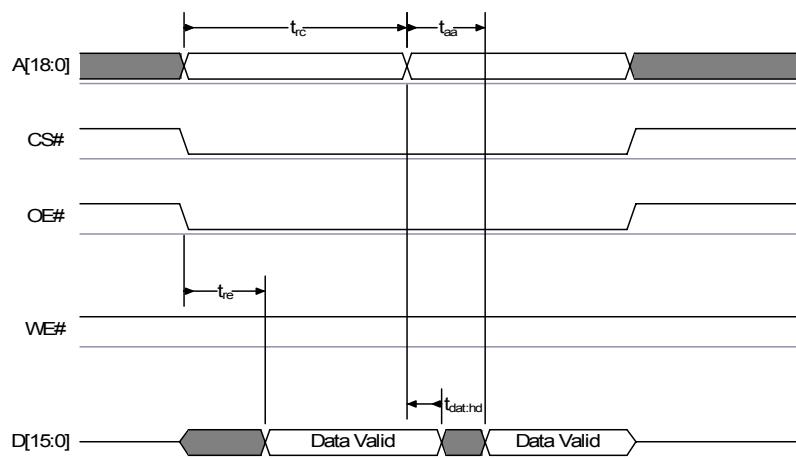

| Figure 8.2   | Memory Read Cycle .....                                               | 39 |

| Figure 9.1   | Universal Asynchronous Receiver .....                                 | 40 |

| Figure 9.2   | Break Signal .....                                                    | 41 |

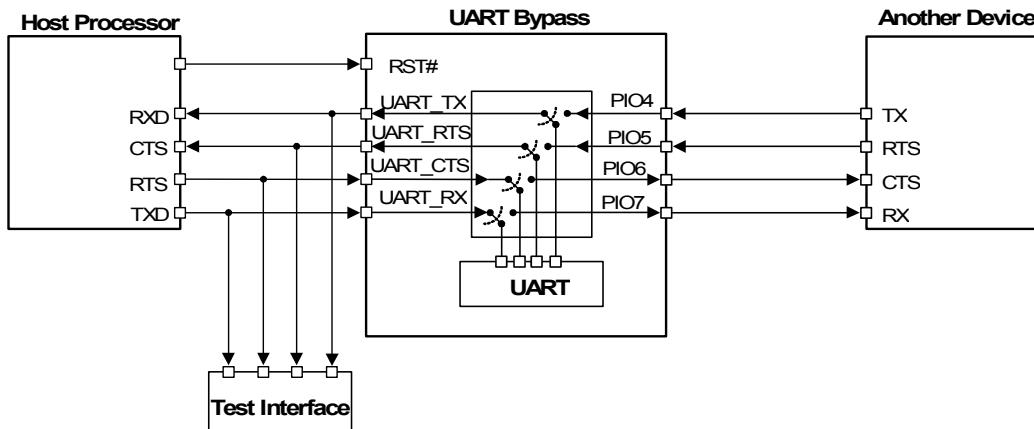

| Figure 9.3   | UART Bypass Architecture .....                                        | 42 |

| Figure 9.4   | Example EEPROM Connection .....                                       | 44 |

| Figure 10.1  | Audio Interface .....                                                 | 45 |

| Figure 10.2  | Stereo Codec Audio Input and Output Stages .....                      | 46 |

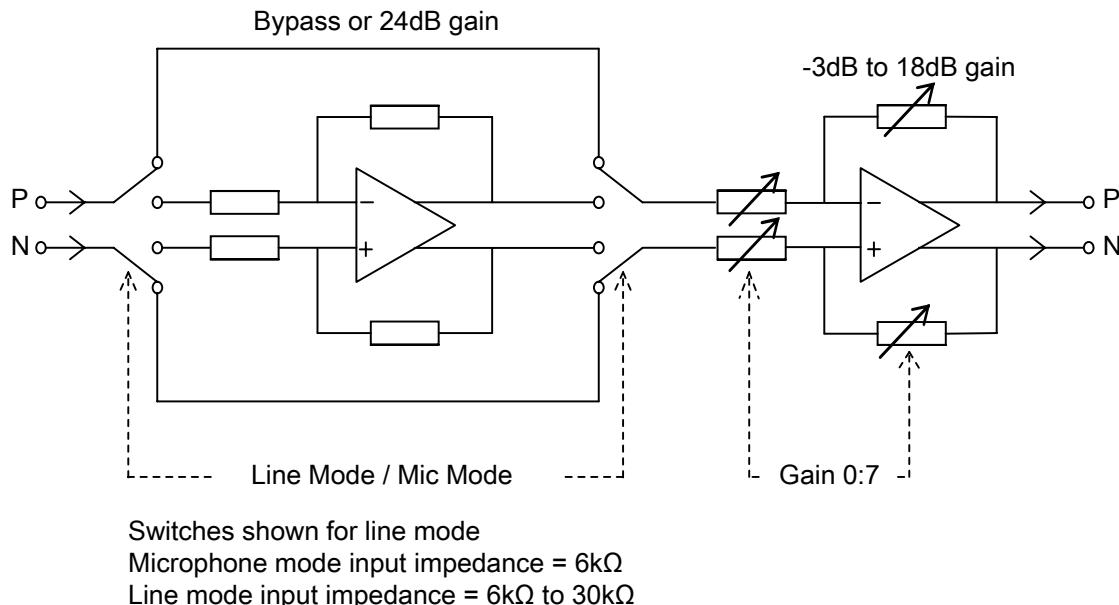

| Figure 10.3  | ADC Analogue Amplifier Block Diagram .....                            | 48 |

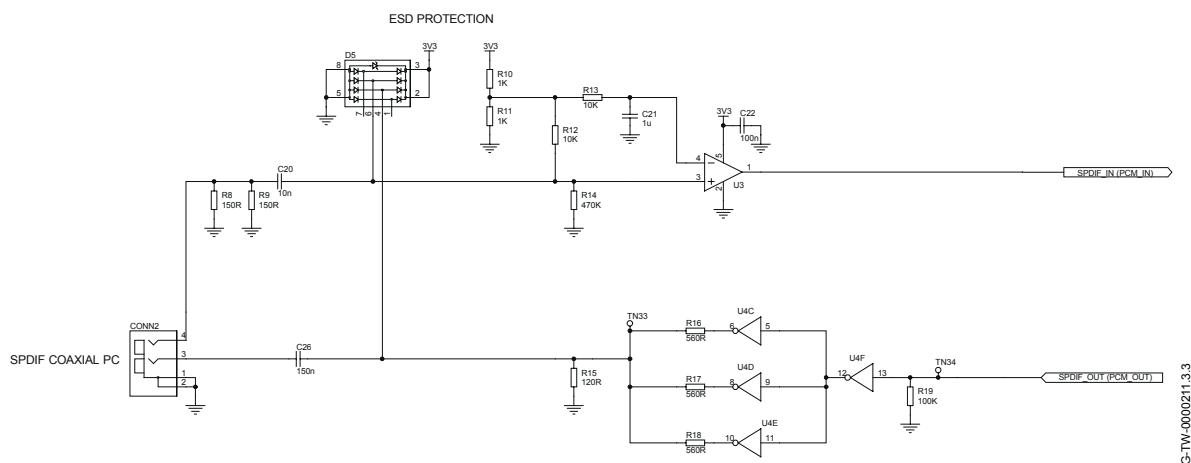

| Figure 10.4  | Example Circuit for SPDIF Interface (Co-Axial) .....                  | 50 |

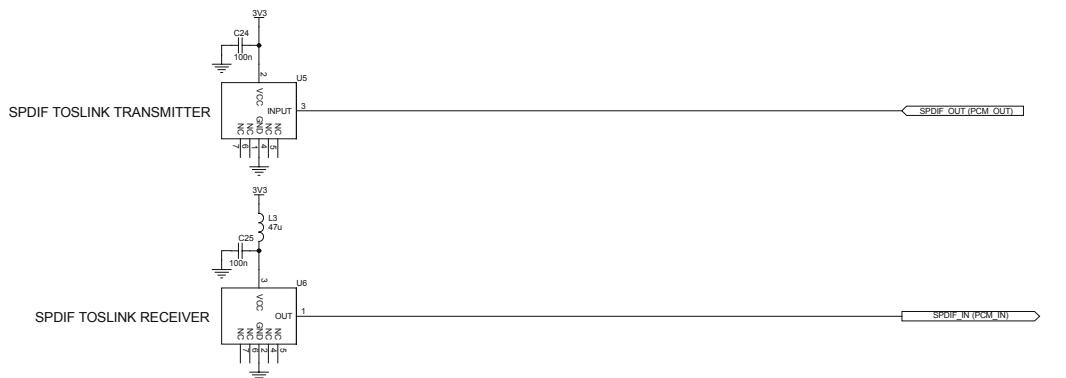

| Figure 10.5  | Example Circuit for SPDIF Interface (Optical) .....                   | 50 |

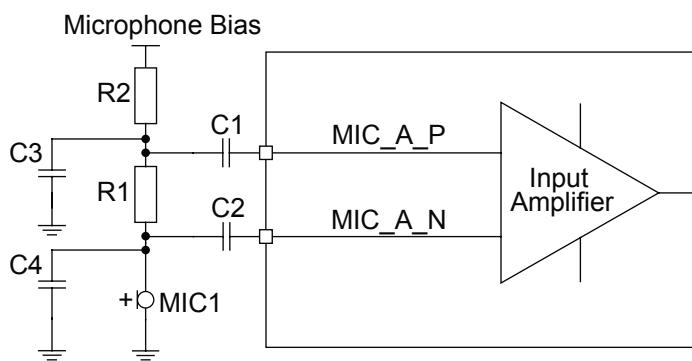

| Figure 10.6  | Microphone Biasing .....                                              | 50 |

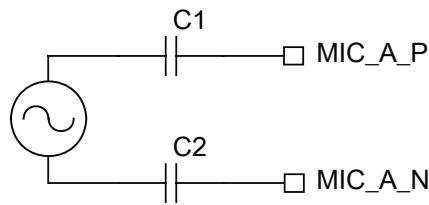

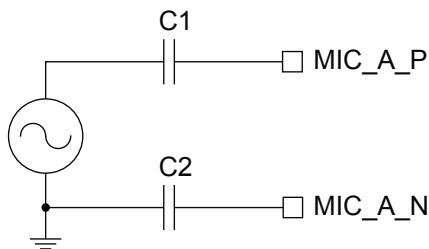

| Figure 10.7  | Differential Input .....                                              | 54 |

| Figure 10.8  | Single-ended Input .....                                              | 54 |

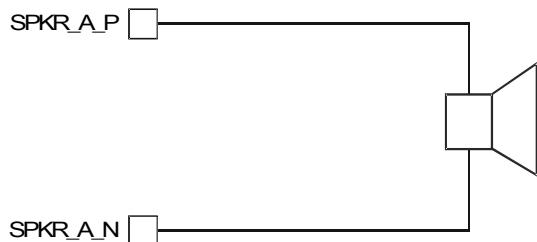

| Figure 10.9  | Speaker Output .....                                                  | 54 |

| Figure 10.10 | PCM Interface Master .....                                            | 57 |

| Figure 10.11 | PCM Interface Slave .....                                             | 57 |

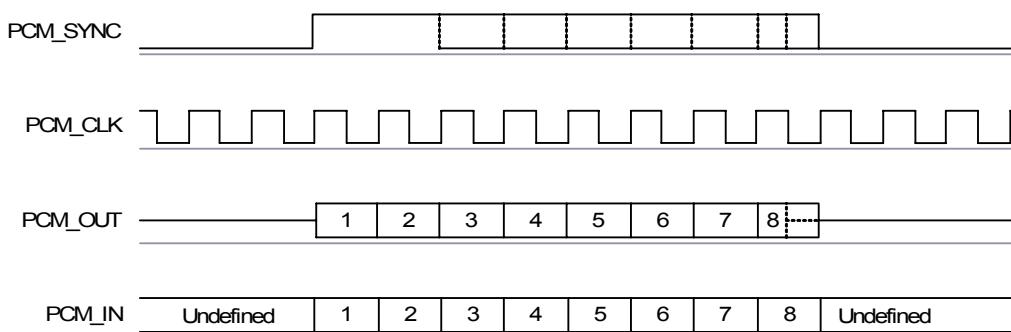

| Figure 10.12 | Long Frame Sync (Shown with 8-bit Companded Sample) .....             | 57 |

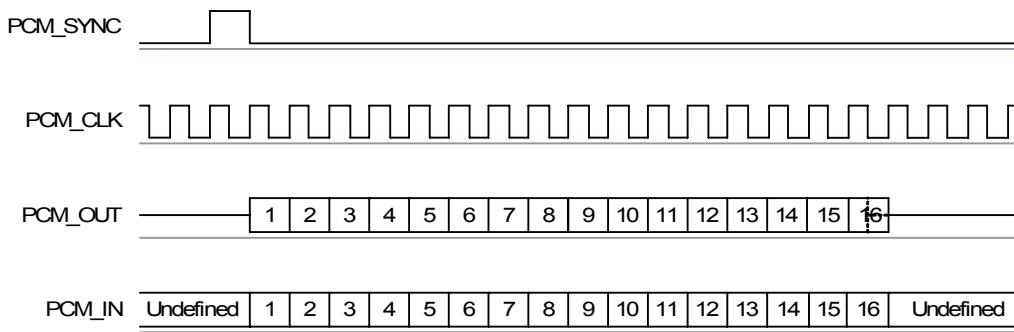

| Figure 10.13 | Short Frame Sync (Shown with 16-bit Sample) .....                     | 58 |

| Figure 10.14 | Multi-slot Operation with Two Slots and 8-bit Companded Samples ..... | 58 |

| Figure 10.15 | GCI Interface .....                                                   | 58 |

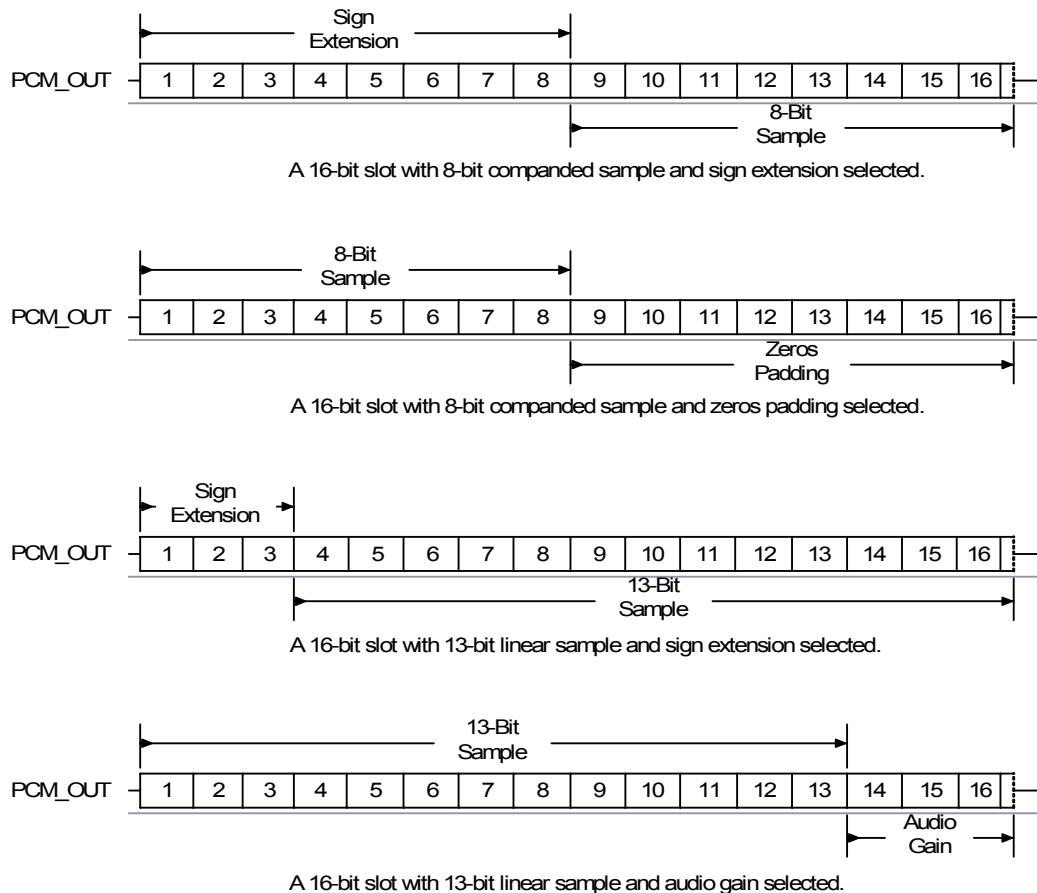

| Figure 10.16 | 16-Bit Slot Length and Sample Formats .....                           | 59 |

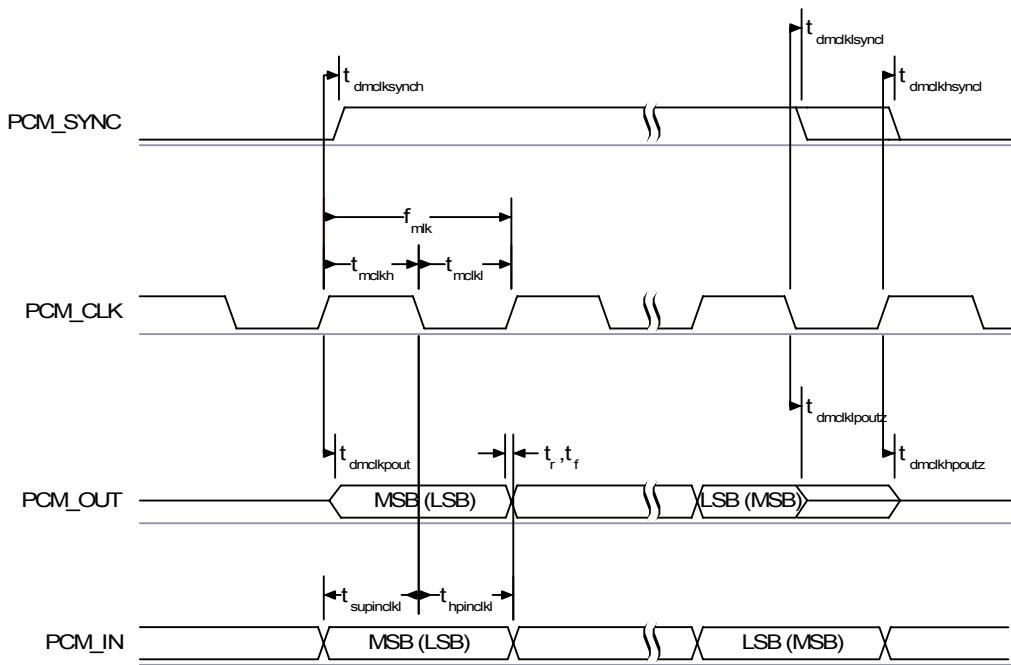

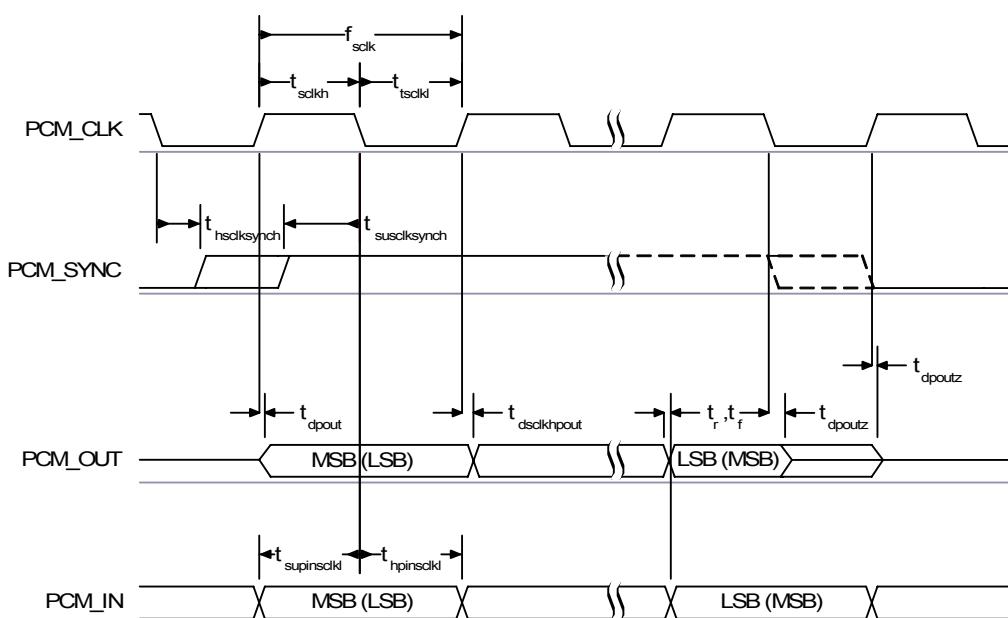

| Figure 10.17 | PCM Master Timing Long Frame Sync .....                               | 61 |

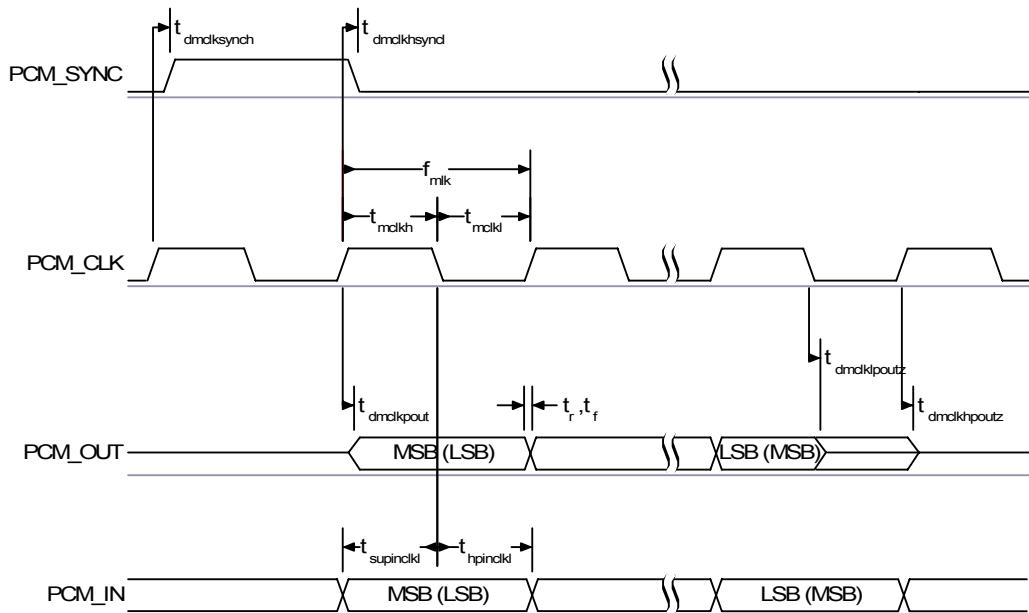

| Figure 10.18 | PCM Master Timing Short Frame Sync .....                              | 61 |

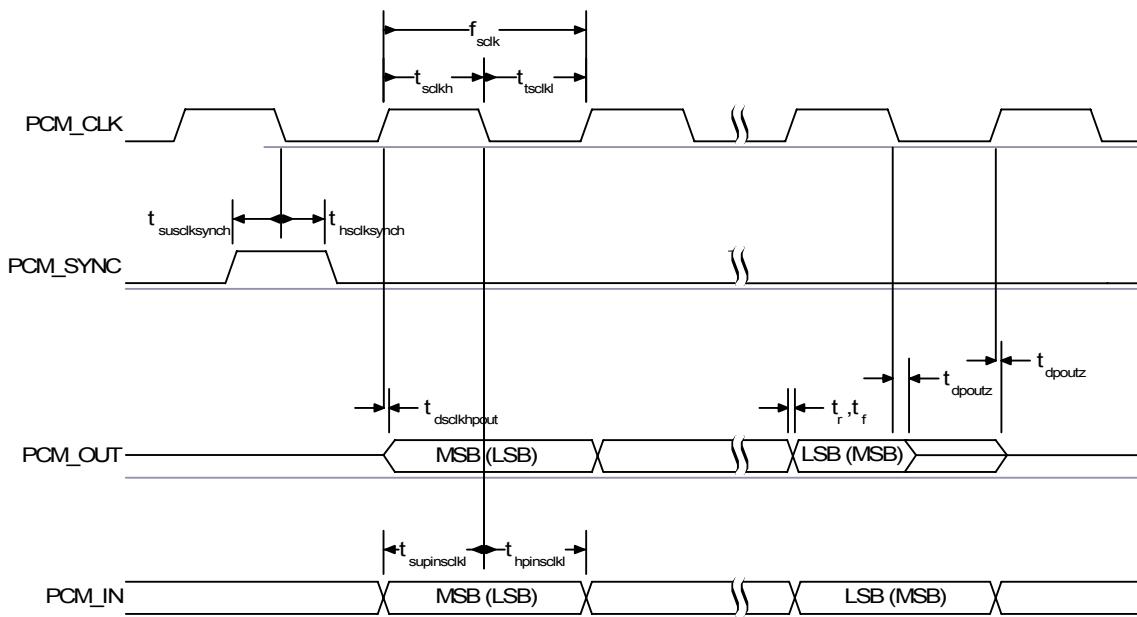

| Figure 10.19 | PCM Slave Timing Long Frame Sync .....                                | 62 |

| Figure 10.20 | PCM Slave Timing Short Frame Sync .....                               | 63 |

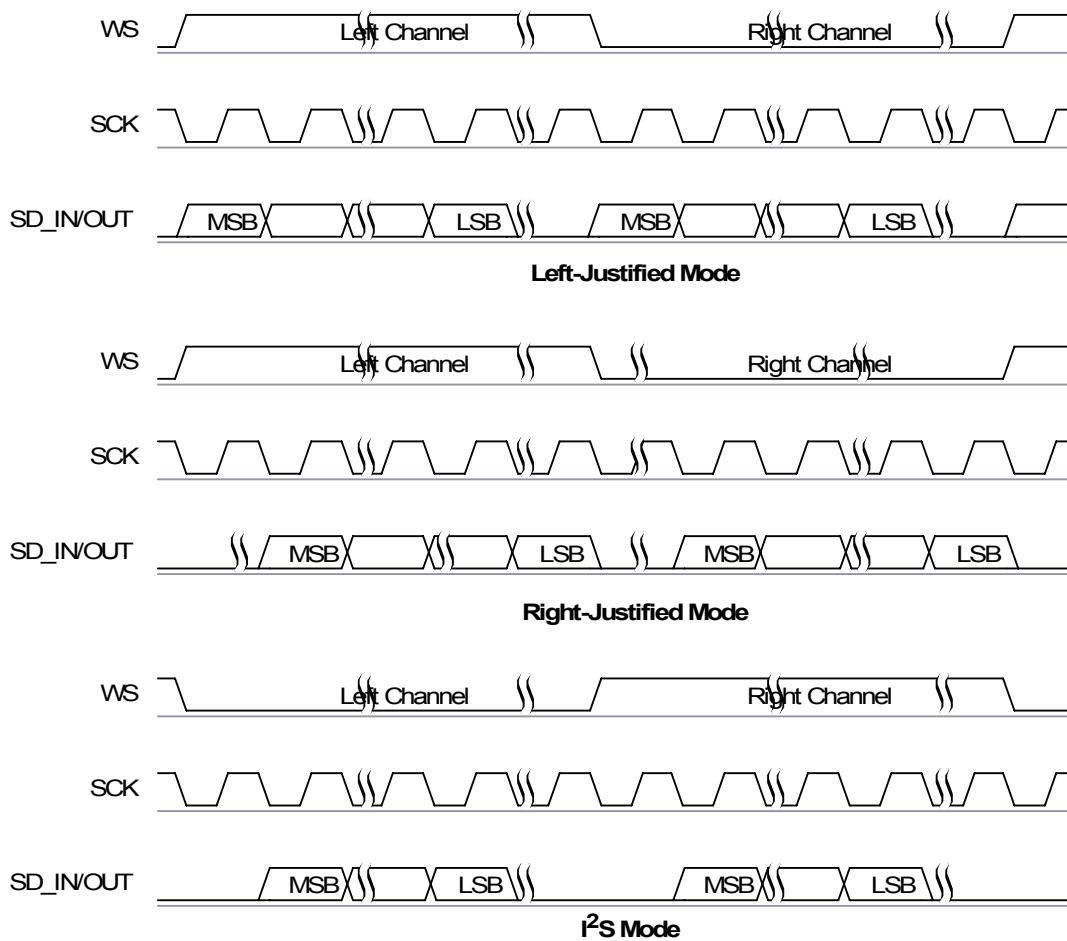

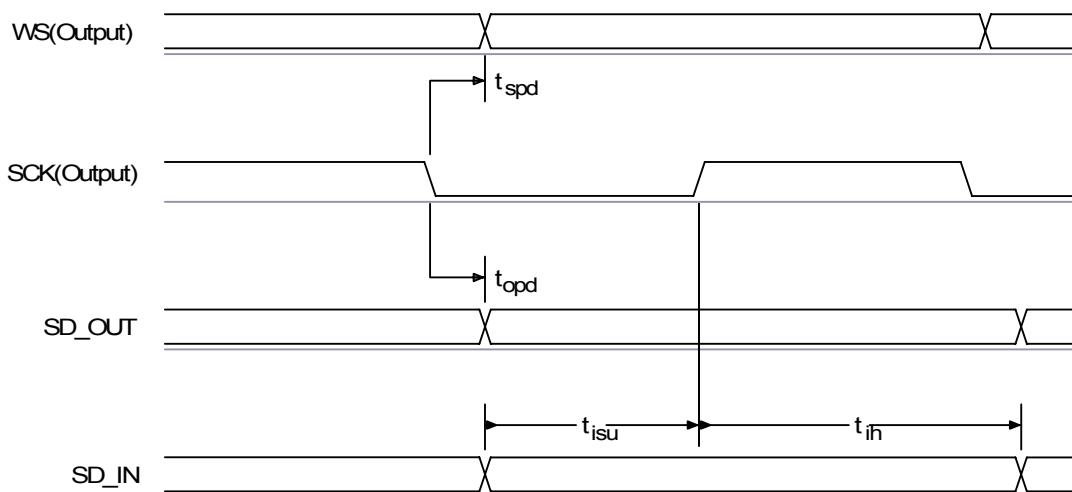

| Figure 10.21 | Digital Audio Interface Modes .....                                   | 67 |

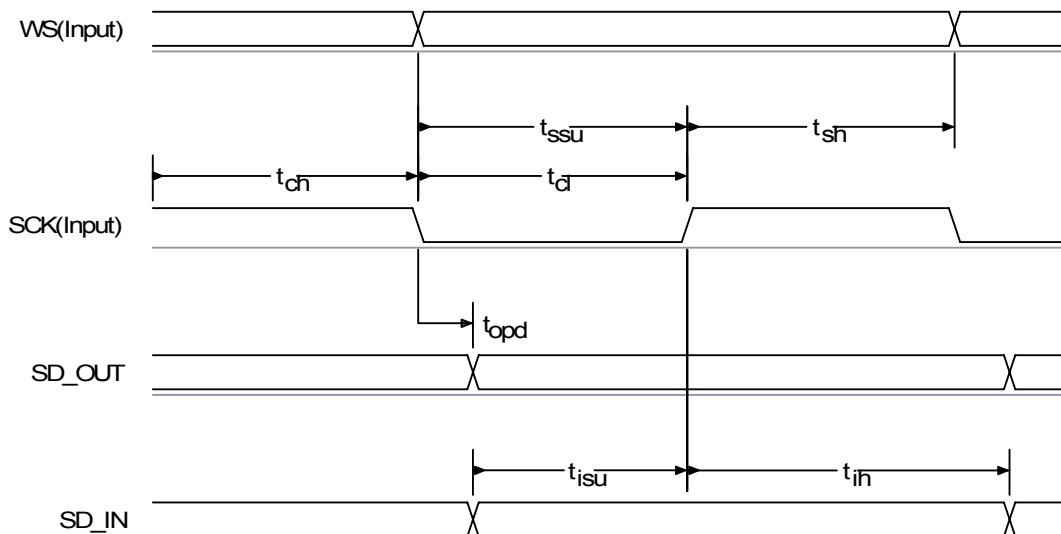

| Figure 10.22 | Digital Audio Interface Slave Timing .....                            | 68 |

| Figure 10.23 | Digital Audio Interface Master Timing .....                           | 69 |

| Figure 11.1  | Voltage Regulator Configuration .....                                 | 70 |

| Figure 11.2  | LED Equivalent Circuit .....                                          | 73 |

| Figure 12.1  | Example Application Schematic .....                                   | 76 |

| Figure 16.1  | BlueCore HCI Stack .....                                              | 93 |

| Figure 18.1  | Tape and Reel Orientation .....                                       | 97 |

| Figure 18.2  | Tape Dimensions .....                                                 | 98 |

| Figure 18.3  | Reel Dimensions .....                                                 | 99 |

## List of Tables

|             |                                                                                       |    |

|-------------|---------------------------------------------------------------------------------------|----|

| Table 4.1   | TXRX_PIO_CONTROL Values .....                                                         | 24 |

| Table 4.2   | Data Rate Schemes .....                                                               | 26 |

| Table 5.1   | PS Key Values for CDMA/3G Phone TCXO .....                                            | 27 |

| Table 5.2   | External Clock Specifications .....                                                   | 28 |

| Table 5.3   | Crystal Specification .....                                                           | 29 |

| Table 8.1   | Flash Device Hardware Requirements .....                                              | 36 |

| Table 8.2   | Flash Sector Boundaries .....                                                         | 36 |

| Table 8.3   | Common Flash Interface Algorithm Command Set Codes .....                              | 37 |

| Table 8.4   | Erase Block Region Information for Uniform 2KW Sectors .....                          | 37 |

| Table 8.5   | Erase Block Region Information for Uniform 1KW Sectors .....                          | 37 |

| Table 8.6   | Erase Block Region Information for 8 x 4KW, n x 32KW Sectors .....                    | 37 |

| Table 8.7   | Erase Block Region Information for 1 x 8KW, 2 x 4KW, 1 x 16KW, n x 32KW Sectors ..... | 37 |

| Table 8.8   | Memory Write Cycle .....                                                              | 38 |

| Table 8.9   | Memory Read Cycle .....                                                               | 39 |

| Table 9.1   | Possible UART Settings .....                                                          | 40 |

| Table 9.2   | Standard Baud Rates .....                                                             | 41 |

| Table 9.3   | Instruction Cycle for a SPI Transaction .....                                         | 43 |

| Table 10.1  | Alternative Functions of the Digital Audio Bus Interface on the PCM Interface .....   | 45 |

| Table 10.2  | ADC Digital Gain Rate Selection .....                                                 | 47 |

| Table 10.3  | DAC Digital Gain Rate Selection .....                                                 | 49 |

| Table 10.4  | DAC Analogue Gain Rate Selection .....                                                | 49 |

| Table 10.5  | Voltage Output Steps .....                                                            | 52 |

| Table 10.6  | Current Output Steps .....                                                            | 53 |

| Table 10.7  | PCM Master Timing .....                                                               | 60 |

| Table 10.8  | PCM Slave Timing .....                                                                | 62 |

| Table 10.9  | PSKEY_PCM_LOW_JITTER_CONFIG Description .....                                         | 64 |

| Table 10.10 | PSKEY_PCM_CONFIG32 Description .....                                                  | 64 |

| Table 10.11 | Alternative Functions of the Digital Audio Bus Interface on the PCM Interface .....   | 65 |

| Table 10.12 | PSKEY_DIGITAL_AUDIO_CONFIG .....                                                      | 66 |

| Table 10.13 | Digital Audio Interface Slave Timing .....                                            | 68 |

| Table 10.14 | Digital Audio Interface Master Timing .....                                           | 69 |

| Table 11.1  | BlueCore5-Multimedia External Voltage Regulator Enable Pins .....                     | 72 |

| Table 11.2  | Pin States on Reset .....                                                             | 74 |

## List of Equations

|               |                                                                             |    |

|---------------|-----------------------------------------------------------------------------|----|

| Equation 4.1  | Output Voltage with Load Current I .....                                    | 24 |

| Equation 4.2  | Output Voltage with No Load Current .....                                   | 24 |

| Equation 5.1  | Load Capacitance .....                                                      | 30 |

| Equation 5.2  | Trim Capacitance .....                                                      | 30 |

| Equation 5.3  | Frequency Trim .....                                                        | 30 |

| Equation 5.4  | Pullability .....                                                           | 30 |

| Equation 5.5  | Transconductance Required for Oscillation .....                             | 31 |

| Equation 5.6  | Equivalent Negative Resistance .....                                        | 31 |

| Equation 9.1  | Baud Rate .....                                                             | 41 |

| Equation 10.1 | IIR Filter Transfer Function, $H(z)$ .....                                  | 56 |

| Equation 10.2 | IIR Filter plus DC Blocking Transfer Function, $H_{DC}(z)$ .....            | 56 |

| Equation 10.3 | PCM_CLK Frequency When Being Generated Using the Internal 48MHz Clock ..... | 63 |

|                                                            |    |

|------------------------------------------------------------|----|

| Equation 10.4 PCM_SYNC Frequency Relative to PCM_CLK ..... | 63 |

| Equation 11.1 LED Current .....                            | 74 |

| Equation 11.2 LED PAD Voltage .....                        | 74 |

# 1 Device Details

## Radio

- Common TX/RX terminal simplifies external matching; eliminates external antenna switch

- BIST minimises production test time

- Bluetooth v2.1 + EDR specification compliant

## Transmitter

- 8dBm RF transmit power with level control from on-chip 6-bit DAC over a dynamic range >30dB

- Class 2 and Class 3 support without the need for an external power amplifier or TX/RX switch

## Receiver

- Receiver sensitivity of -90dBm

- Integrated channel filters

- Digital demodulator for improved sensitivity and co-channel rejection

- Real-time digitised RSSI available on HCI interface

- Fast AGC for enhanced dynamic range

## Synthesiser

- Fully integrated synthesiser requires no external VCO, varactor diode, resonator or loop filter

- Compatible with crystals 16MHz to 26MHz or an external clock 12MHz to 52MHz

- Accepts 14.40, 15.36, 16.2, 16.8, 19.2, 19.44, 19.68, 19.8 and 38.4MHz TCXO frequencies for GSM and CDMA devices with sinusoidal or logic level signals

## Baseband and Software

- 32Mb external flash

- 48KB internal RAM, allows full-speed data transfer, mixed voice/data and full piconet support

- Logic for forward error correction, header error control, access code correlation, CRC, demodulation, encryption bit stream generation, whitening and transmit pulse shaping

- Transcoders for A-law, μ-law and linear voice from host and A-law, μ-law and CVSD voice over air

## Physical Interfaces

- SPI with clock speeds up to 64MHz in master mode, requires firmware support, and 32MHz in slave mode

- I<sup>2</sup>C master compatible interface

- UART interface with programmable data rate up to 3Mbits/s with an optional bypass mode

- USB v2.0 interface

- Bidirectional serial programmable audio interface supporting PCM, I<sup>2</sup>S and SPDIF formats

- 2 LED drivers with faders

## Kalimba DSP

- Very low power Kalimba DSP coprocessor, 64MIPS, 24-bit fixed point core

- SBC decode takes approximately 4mW power consumption while streaming music

- Single-cycle MAC; 24 x 24-bit multiply and 56-bit accumulator

- 32-bit instruction word, dual 24-bit data memory

- 6K x 32-bit program RAM, 16K x 24-bit + 12K x 24-bit data RAM

- 64-word x 32-bit program memory cache when executing from external flash

## Stereo Audio Codec

- 16-bit internal stereo codec

- Dual ADC and DAC for stereo audio

- Integrated amplifiers for driving 16Ω speakers; no need for external components

- Support for single-ended speaker termination and line output

- Integrated low-noise microphone bias

- ADC sample rates are 8, 11.025, 16, 22.05, 32 and 44.1kHz

- DAC sample rates are 8, 11.025, 12, 16, 22.05, 24, 32, 44.1 and 48kHz

## Auxiliary Features

- User space on processor for customer applications

- Crystal oscillator with built-in digital trimming

- Power management includes digital shutdown and wake-up commands with an integrated low-power oscillator for ultra-low power Park/Sniff/Hold mode

- Clock request output to control external clock

- On-chip regulators: 1.5V output from 1.8V to 2.7V input and 1.8V output from 2.7V to 4.5V input

- On-chip high-efficiency switch-mode regulator; 1.8V output from 2.7V to 4.4V input

- Power-on-reset cell detects low supply voltage

- 10-bit ADC and 8-bit DAC available to applications

- On-chip charger for lithium ion/polymer batteries

## Bluetooth Stack

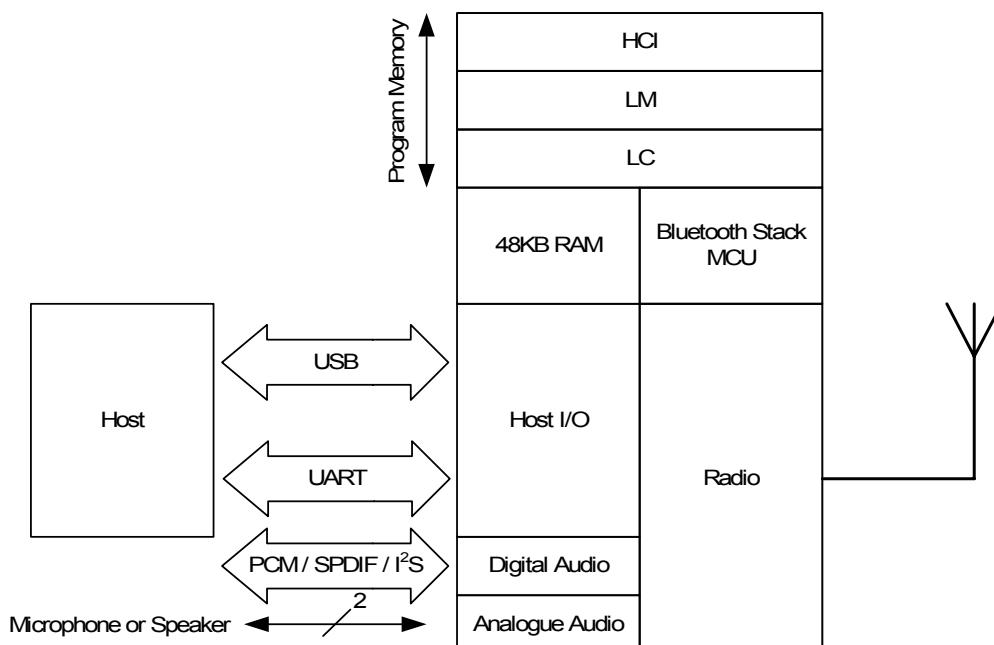

CSR's Bluetooth Protocol Stack runs on the on-chip MCU in a variety of configurations:

- Standard HCI, UART or USB

- Audio codec and echo-noise suppression or customer-specific algorithms running on the DSP

## Package Option

- TFBGA 169-ball, 8 x 8 x 1.2mm, 0.5mm pitch

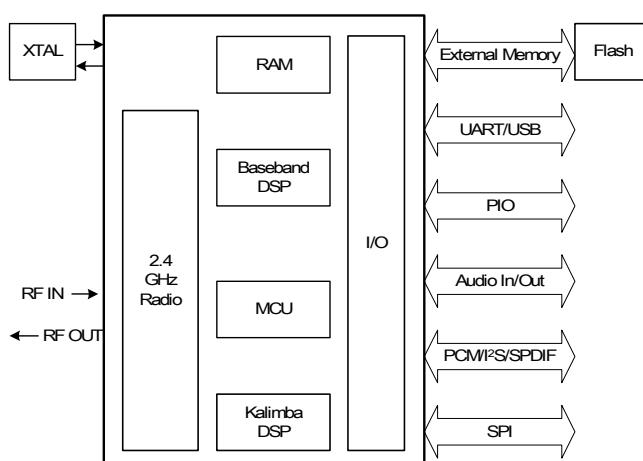

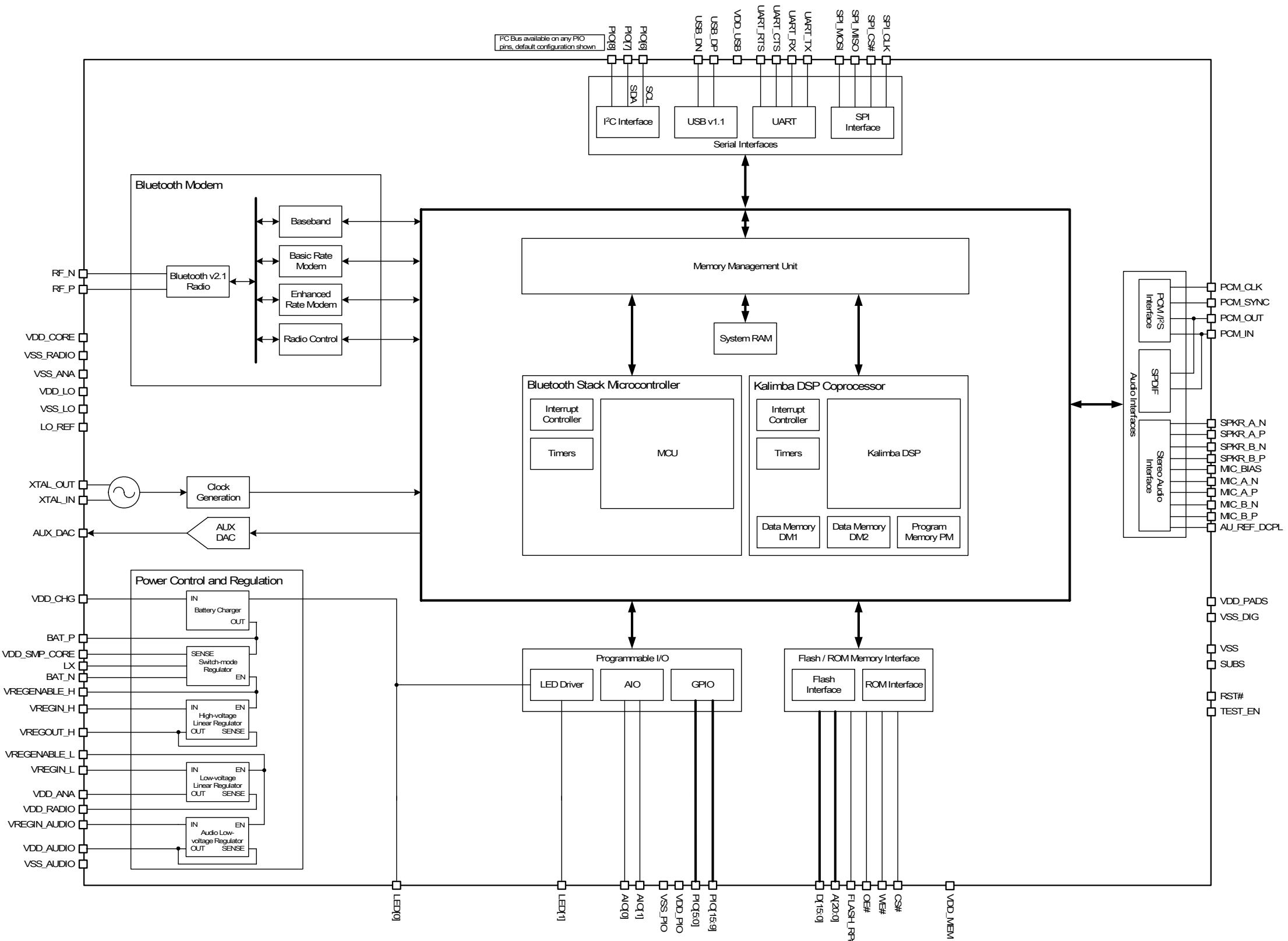

## 2 Functional Block Diagram

Figure 2.1: Functional Block Diagram

### 3 Package Information

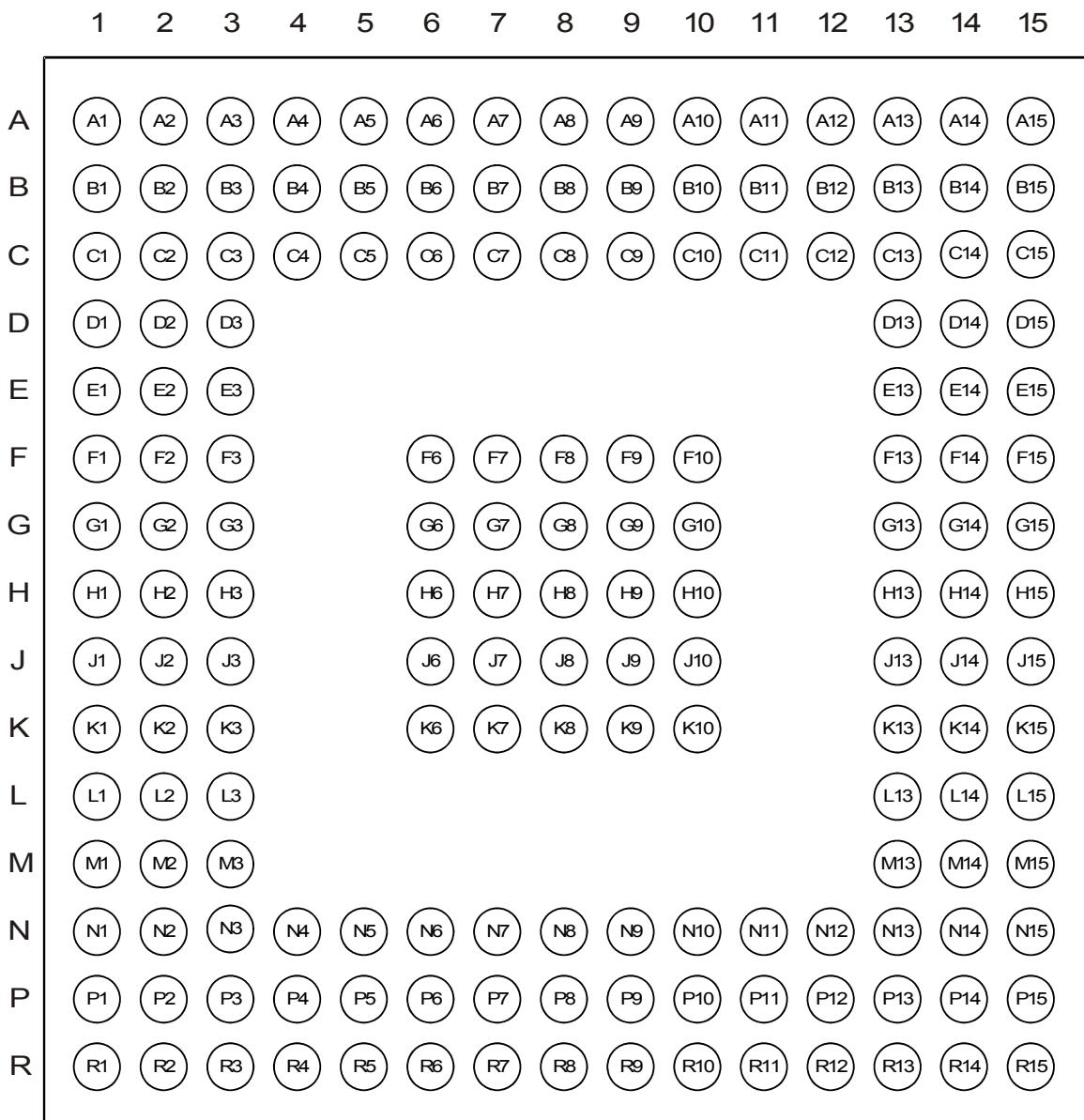

#### 3.1 Pinout Diagram

Orientation from Top

Figure 3.1: Device Pinout

### 3.2 Device Terminal Functions

| Radio   | Ball | Pad Type | Supply Domain | Description                                |

|---------|------|----------|---------------|--------------------------------------------|

| RF_P    | K1   | RF       | VDD_RADIO     | Transmitter output/switched receiver input |

| RF_N    | L1   | RF       | VDD_RADIO     | Complement of RF_P                         |

| AUX_DAC | H2   | Analogue | VDD_PIO       | 8-bit voltage-output DAC                   |

| Synthesiser and Oscillator | Ball | Pad Type | Supply Domain | Description                                   |

|----------------------------|------|----------|---------------|-----------------------------------------------|

| XTAL_IN                    | R1   | Analogue | VDD_ANA       | For crystal or external clock input           |

| XTAL_OUT                   | R2   | Analogue | VDD_ANA       | Drive for crystal                             |

| LO_REF                     | P3   | Analogue | VDD_ANA       | Reference voltage to decouple the synthesiser |

| UART     | Ball | Pad Type                                                        | Supply Domain | Description                     |

|----------|------|-----------------------------------------------------------------|---------------|---------------------------------|

| UART_TX  | N15  | Bidirectional CMOS output, tristate, with weak internal pull-up | VDD_USB       | UART data output                |

| UART_RX  | N14  | CMOS input with weak internal pull-down                         | VDD_USB       | UART data input                 |

| UART_RTS | R15  | Bidirectional CMOS output, tristate, with weak internal pull-up | VDD_USB       | UART request to send active low |

| UART_CTS | P15  | CMOS input with weak internal pull-down                         | VDD_USB       | UART clear to send active low   |

| USB    | Ball | Pad Type      | Supply Domain | Description                                                   |

|--------|------|---------------|---------------|---------------------------------------------------------------|

| USB_DP | P14  | Bidirectional | VDD_USB       | USB data plus with selectable internal 1.5kΩ pull-up resistor |

| USB_DN | P13  | Bidirectional | VDD_USB       | USB data minus                                                |

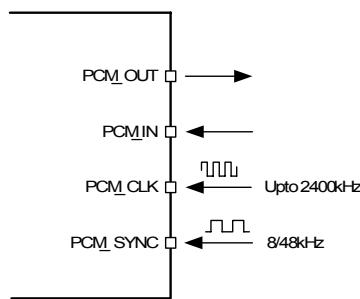

| PCM Interface | Ball | Pad Type                                            | Supply Domain | Description             |

|---------------|------|-----------------------------------------------------|---------------|-------------------------|

| PCM_OUT       | F15  | CMOS output, tristate, with weak internal pull-down | VDD_PADS      | Synchronous data output |

| PCM_IN        | G15  | CMOS input, with weak internal pull-down            | VDD_PADS      | Synchronous data input  |

| PCM_SYNC      | F14  | Bidirectional with weak internal pull-down          | VDD_PADS      | Synchronous data sync   |

| PCM_CLK       | F13  | Bidirectional with weak internal pull-down          | VDD_PADS      | Synchronous data clock  |

| SPI Interface | Ball | Pad Type                                            | Supply Domain | Description                     |

|---------------|------|-----------------------------------------------------|---------------|---------------------------------|

| SPI_MISO      | D15  | CMOS output, tristate, with weak internal pull-down | VDD_PADS      | SPI data output                 |

| SPI_MOSI      | E13  | CMOS input, with weak internal pull-down            | VDD_PADS      | SPI data input                  |

| SPI_CS#       | E15  | Input with weak internal pull-up                    | VDD_PADS      | Chip select for SPI, active low |

| SPI_CLK       | E14  | Input with weak internal pull-down                  | VDD_PADS      | SPI clock                       |

| PIO Port | Ball | Pad Type                                                       | Supply Domain | Description                                    |

|----------|------|----------------------------------------------------------------|---------------|------------------------------------------------|

| PIO[15]  | M15  | Bidirectional with programmable strength internal pull-up/down | VDD_PADS      | Programmable input/output line                 |

| PIO[14]  | J15  |                                                                |               |                                                |

| PIO[13]  | K14  |                                                                |               |                                                |

| PIO[12]  | K13  |                                                                |               |                                                |

| PIO[11]  | L14  |                                                                |               |                                                |

| PIO[10]  | M13  |                                                                |               |                                                |

| PIO[9]   | M14  |                                                                |               |                                                |

| PIO[8]   | J14  |                                                                |               |                                                |

| PIO[7]   | J13  |                                                                |               |                                                |

| PIO[6]   | H15  |                                                                |               |                                                |

| PIO[5]   | H14  | Bidirectional with programmable strength internal pull-up/down | VDD_PIO       | Programmable input/output line (external TXEN) |

| PIO[4]   | H13  |                                                                |               | Programmable input/output line (external RXEN) |

| PIO[3]   | F3   |                                                                |               | Programmable input/output line                 |

| PIO[2]   | G3   |                                                                |               | Programmable input/output line                 |

| PIO[1]   | F2   | Bidirectional                                                  | VDD_ANA       | Analogue programmable input/output line        |

| PIO[0]   | F1   |                                                                |               |                                                |

| AIO[1]   | N3   | Bidirectional                                                  | VDD_ANA       | Analogue programmable input/output line        |

| AIO[0]   | R4   |                                                                |               |                                                |

| Test and Debug | Ball | Pad Type                                  | Supply Domain | Description                                                            |

|----------------|------|-------------------------------------------|---------------|------------------------------------------------------------------------|

| RST#           | G13  | CMOS input with weak internal pull-up     | VDD_PADS      | Reset if low. Input debounced so must be low for >5ms to cause a reset |

| TEST_EN        | G14  | CMOS input with strong internal pull-down | VDD_PADS      | For test purposes only (leave unconnected)                             |

| External Memory Address Interface | Ball | Pad Type                                     | Supply Domain | Description  |

|-----------------------------------|------|----------------------------------------------|---------------|--------------|

| A[20]                             | N12  |                                              |               |              |

| A[19]                             | P8   |                                              |               |              |

| A[18]                             | N9   |                                              |               |              |

| A[17]                             | R10  |                                              |               |              |

| A[16]                             | P9   |                                              |               |              |

| A[15]                             | R5   |                                              |               |              |

| A[14]                             | P5   |                                              |               |              |

| A[13]                             | N5   |                                              |               |              |

| A[12]                             | R6   |                                              |               |              |

| A[11]                             | P6   |                                              |               |              |

| A[10]                             | N6   | CMOS output,<br>tristate, weak pull-<br>down | VDD_MEM       | Address line |

| A[9]                              | R7   |                                              |               |              |

| A[8]                              | P7   |                                              |               |              |

| A[7]                              | P10  |                                              |               |              |

| A[6]                              | N10  |                                              |               |              |

| A[5]                              | R11  |                                              |               |              |

| A[4]                              | P11  |                                              |               |              |

| A[3]                              | N11  |                                              |               |              |

| A[2]                              | R12  |                                              |               |              |

| A[1]                              | P12  |                                              |               |              |

| A[0]                              | C9   |                                              |               |              |

| External Memory Data Interface | Ball | Pad Type                                   | Supply Domain | Description |

|--------------------------------|------|--------------------------------------------|---------------|-------------|

| D[15]                          | A5   | Bidirectional with weak internal pull-down | VDD_MEM       | Data line   |

| D[14]                          | C5   |                                            |               |             |

| D[13]                          | B6   |                                            |               |             |

| D[12]                          | A7   |                                            |               |             |

| D[11]                          | C7   |                                            |               |             |

| D[10]                          | C8   |                                            |               |             |

| D[9]                           | B10  |                                            |               |             |

| D[8]                           | A11  |                                            |               |             |

| D[7]                           | B5   |                                            |               |             |

| D[6]                           | A6   |                                            |               |             |

| D[5]                           | C6   |                                            |               |             |

| D[4]                           | B7   |                                            |               |             |

| D[3]                           | B8   |                                            |               |             |

| D[2]                           | A9   |                                            |               |             |

| D[1]                           | C10  |                                            |               |             |

| D[0]                           | B11  |                                            |               |             |

| External Memory Interface | Ball | Pad Type                                         | Supply Domain | Description                                        |

|---------------------------|------|--------------------------------------------------|---------------|----------------------------------------------------|

| FLASH_RP#                 | R9   | CMOS output, tristate with internal weak pull-up | VDD_MEM       | Flash reset                                        |

| OE#                       | C11  | CMOS output, tristate with internal weak pull-up | VDD_MEM       | Output enable for external memory, active low      |

| WE#                       | N7   | CMOS output, tristate with internal weak pull-up | VDD_MEM       | Flash write enable for external memory, active low |

| CS#                       | A10  | CMOS output, tristate with internal weak pull-up | VDD_MEM       | Chip select for external memory, active low        |

| Codec       | Ball | Pad Type | Supply Domain    | Description                                            |

|-------------|------|----------|------------------|--------------------------------------------------------|

| MIC_A_P     | C2   | Analogue | VDD_AUDIO        | Microphone input positive, left                        |

| MIC_A_N     | C1   | Analogue | VDD_AUDIO        | Microphone input negative, left                        |

| MIC_B_P     | B2   | Analogue | VDD_AUDIO        | Microphone input positive, right                       |

| MIC_B_N     | B1   | Analogue | VDD_AUDIO        | Microphone input negative, right                       |

| SPKR_A_P    | E1   | Analogue | VDD_AUDIO        | Speaker output positive, left                          |

| SPKR_A_N    | E2   | Analogue | VDD_AUDIO        | Speaker output negative, left                          |

| SPKR_B_P    | D1   | Analogue | VDD_AUDIO        | Speaker output positive, right                         |

| SPKR_B_N    | D2   | Analogue | VDD_AUDIO        | Speaker output negative, right                         |

| MIC_BIAS    | B3   | Analogue | VDD_AUDIO, BAT_P | Microphone bias                                        |

| AU_REF_DCPL | E3   | Analogue | VDD_AUDIO        | Decoupling of audio reference (for high-quality audio) |

| LED Drivers | Ball | Pad Type          | Supply Domain    | Description |

|-------------|------|-------------------|------------------|-------------|

| LED[1]      | D14  | Open drain output | See Section 11.9 | LED driver  |

| LED[0]      | D13  | Open drain output | See Section 11.9 | LED driver  |

| Power Supplies and Control | Ball | Pad Type                         | Description                                                                                                   |

|----------------------------|------|----------------------------------|---------------------------------------------------------------------------------------------------------------|

| VREGENABLE_H               | B14  | Analogue                         | Take high to enable high-voltage linear regulator and switch-mode regulator                                   |

| VREGIN_H                   | A15  | Regulator input                  | Input to internal high-voltage linear regulator                                                               |

| VREGOUT_H                  | B15  | Supply                           | High-voltage linear regulator output                                                                          |

| VREGENABLE_L               | M2   | Analogue                         | Take high to enable both low-voltage regulator and audio low-voltage regulator                                |

| VREGIN_L                   | N2   | Regulator input                  | Input to internal low-voltage linear regulator for non-audio core circuitry                                   |

| VDD_ANA                    | P1   | VDD/Low-voltage regulator output | Positive supply output for analogue circuitry and 1.5V regulated output (from internal low-voltage regulator) |

| VREGIN_AUDIO               | A3   | Regulator input                  | Input to internal audio low-voltage linear regulator                                                          |

| Power Supplies and Control | Ball                                         | Pad Type                           | Description                                                                                                |

|----------------------------|----------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------|

| VDD_AUDIO                  | A2                                           | VDD/Low-voltage regulator output   | Positive supply output for audio circuitry and 1.5V regulated output (from internal low-voltage regulator) |

| VDD_CHG                    | A12                                          | Charger input                      | Lithium ion/polymer battery charger input                                                                  |

| BAT_P                      | B13                                          | Battery terminal +ve               | Lithium ion/polymer battery positive terminal. Battery charger output and input to switch-mode regulator   |

| VDD_SMP_CORE               | A14                                          | VDD                                | Positive supply for switch mode control circuitry                                                          |

| LX                         | A13                                          | Switch-mode power regulator output | Switch-mode power regulator output                                                                         |

| VDD_CORE                   | C15, K15                                     | VDD                                | Positive supply for internal digital circuitry, 1.5V                                                       |

| VDD_RADIO                  | M1                                           | VDD/Low-voltage regulator sense    | Positive supply for RF circuitry, 1.5V                                                                     |

| VDD_LO                     | N1                                           | VDD                                | Positive supply for local oscillator circuitry, 1.5V                                                       |

| VDD_USB                    | R14                                          | VDD                                | Positive supply for UART/USB ports                                                                         |

| VDD_PIO                    | G1                                           | VDD                                | Positive supply for PIO[3:0] and auxiliary DAC                                                             |

| VDD_PADS                   | L15                                          | VDD                                | Positive supply for all other digital Input/Output ports, SPI/PCM ports and PIO[15:4]                      |

| VDD_MEM                    | A4, A8, B9, R8, R13                          | VDD                                | Positive supply for flash pads                                                                             |

| VSS_DIG                    | B4, C4, C12, C13, C14, H3, L13, N4, N8, N13, | VSS                                | Ground connection for internal digital circuitry                                                           |

| VSS_RADIO                  | J2, K2, L2                                   | VSS                                | Ground connections for RF circuitry                                                                        |

| Power Supplies and Control | Ball                                             | Pad Type             | Description                                                                                |

|----------------------------|--------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------|

| VSS_LO                     | K3, L3                                           | VSS                  | Ground connections for local oscillator                                                    |

| VSS_ANA                    | P2                                               | VSS                  | Ground connections for analogue circuitry                                                  |

| VSS_AUDIO                  | A1, D3                                           | VSS                  | Ground connection for audio                                                                |

| VSS                        | C3, F6-F10, G6-G10, H6-H10, J3,J6-J10, K6-10, M3 | VSS                  | Ground connection                                                                          |

| BAT_N                      | B12                                              | Battery terminal -ve | Lithium ion/polymer battery negative terminal. Ground connection for switch-mode regulator |

| SUBS                       | R3                                               | VSS                  | Connection to internal die substrate<br>Connect to lowest possible potential               |

| Unconnected Terminals | Ball           | Description       |

|-----------------------|----------------|-------------------|

| NC                    | G2, H1, J1, P4 | Leave unconnected |

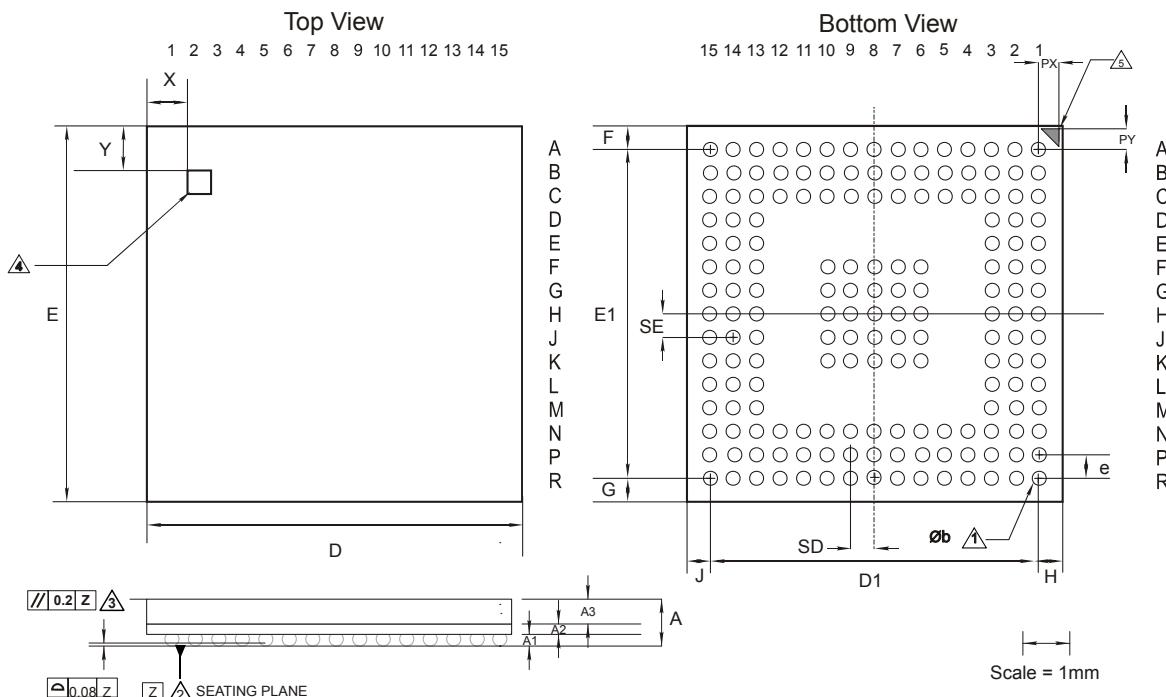

### 3.3 Package Dimensions

| Description       | 169-Ball Thin Fine-Pitch Ball Grid Array (TFBGA)        |         |         |                                                                                                                                                                                       |

|-------------------|---------------------------------------------------------|---------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Size              | 8 x 8 x 1.2mm                                           |         |         |                                                                                                                                                                                       |

| Pitch             | 0.5mm                                                   |         |         |                                                                                                                                                                                       |

| Package Ball Land | Solder mask defined. Solder mask aperture 275 $\mu$ m Ø |         |         |                                                                                                                                                                                       |

| Dimension         | Minimum                                                 | Typical | Maximum | Notes                                                                                                                                                                                 |

| A                 |                                                         |         | 1.2     |                                                                                                                                                                                       |

| A1                | 0.16                                                    | 0.21    | 0.26    |  Dimension b is measured at the maximum solder ball diameter parallel to datum plane Z             |

| A2                |                                                         | 0.21    |         |                                                                                                                                                                                       |

| A3                |                                                         | 0.7     |         |  Datum Z is defined by the spherical crowns of the solder balls                                    |

| b                 | 0.27                                                    | 0.32    | 0.37    |  Parallelism measurement shall exclude any effect of mark on top surface of package                |

| D                 | 7.90                                                    | 8.00    | 8.10    |                                                                                                                                                                                       |

| E                 | 7.90                                                    | 8.00    | 8.10    |                                                                                                                                                                                       |

| e                 |                                                         | 0.5     |         |                                                                                                                                                                                       |

| D1                |                                                         | 7.00    |         |  Top-side polarity mark. The dimensions of the square polarity mark are 0.75 x 0.75mm.             |

| E1                |                                                         | 7.00    |         |                                                                                                                                                                                       |

| F                 |                                                         | 0.50    |         |                                                                                                                                                                                       |

| G                 |                                                         | 0.50    |         |                                                                                                                                                                                       |

| H                 |                                                         | 0.50    |         |                                                                                                                                                                                       |

| J                 |                                                         | 0.50    |         |                                                                                                                                                                                       |

| PX                |                                                         | 0.35    |         |  Bottom-side polarity mark. The dimensions of the triangular polarity mark are 0.3 x 0.3 x 0.42mm. |

| PY                |                                                         | 0.35    |         |                                                                                                                                                                                       |

| SD                |                                                         | 0.5     |         |                                                                                                                                                                                       |

| SE                |                                                         | 0.5     |         |                                                                                                                                                                                       |

| X                 |                                                         | 1.35    |         |                                                                                                                                                                                       |

| Y                 |                                                         | 0.85    |         |                                                                                                                                                                                       |

| JEDEC             | MO-195                                                  |         |         |                                                                                                                                                                                       |

| Unit              | mm                                                      |         |         |                                                                                                                                                                                       |

Figure 3.2: 169-ball TFBGA Package Dimensions

### 3.4 PCB Design and Assembly Considerations

This section lists recommendations to achieve maximum board-level reliability of the 8 x 8 x 1.2mm TFBGA 169-ball package:

- NSMD lands, i.e. lands smaller than the solder mask aperture, are preferred because of the greater accuracy of the metal definition process compared to the solder mask process. With solder mask defined pads, the overlap of the solder mask on the land creates a step in the solder at the land interface, which can cause stress concentration and act as a point for crack initiation.

- Ideally, via-in-pad technology should be used to achieve truly NSMD lands. Where this is not possible, a maximum of one trace connected to each land is preferred and this trace should be as thin as possible – taking into consideration its current carrying and the RF requirements.

- 35 $\mu$ m thick (1oz) copper lands are recommended rather than 17 $\mu$ m thick (0.5oz). This results in a greater standoff which has been proven to provide greater reliability during thermal cycling.

- Land diameter should be the same as that on the package to achieve optimum reliability.

- Solder paste is preferred to flux during the assembly process because this adds to the final volume of solder in the joint, increasing its reliability.

- Where a nickel gold plating finish is used, the gold thickness should be kept below 0.5 $\mu$ m to prevent brittle gold/tin intermetallics forming in the solder.

### 3.5 Typical Solder Reflow Profile

See *Typical Solder Reflow Profile for Lead-free Devices* for information.

## 4 Bluetooth Modem

### 4.1 RF Ports

#### 4.1.1 RF\_N and RF\_P

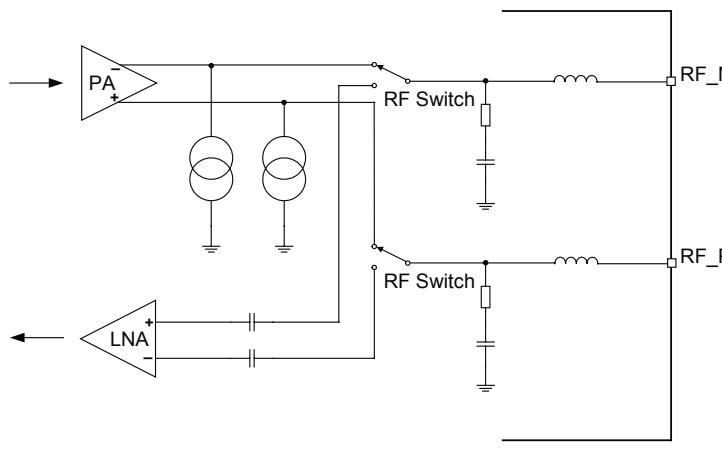

RF\_N and RF\_P form a complementary balanced pair and are available for both transmit and receive. On transmit their outputs are combined using an external balun into the single-ended output required for the antenna. Similarly, on receive their input signals are combined internally.

Both terminals present similar complex impedances that may require matching networks between them and the balun. Viewed from the chip, the outputs can each be modelled as an ideal current source in parallel with a lossy capacitor. An equivalent series inductance can represent the package parasitics.

GTW-0003422

Figure 4.1: Simplified Circuit RF\_N and RF\_P

RF\_N and RF\_P require an external DC bias. The DC level must be set at VDD\_RADIO.

### 4.2 RF Receiver

The receiver features a near-zero IF architecture that allows the channel filters to be integrated onto the die. Sufficient out-of-band blocking specification at the LNA input allows the receiver to be used in close proximity to GSM and W-CDMA cellular phone transmitters without being desensitised. The use of a digital FSK discriminator means that no discriminator tank is needed and its excellent performance in the presence of noise allows BlueCore5-Multimedia External to exceed the Bluetooth requirements for co-channel and adjacent channel rejection.

For EDR, the demodulator contains an ADC which digitises the IF received signal. This information is then passed to the EDR modem.

#### 4.2.1 Low Noise Amplifier

The LNA operates in differential mode and takes its input from the shared RF port.

#### 4.2.2 RSSI Analogue to Digital Converter

The ADC implements fast AGC. The ADC samples the RSSI voltage on a slot-by-slot basis. The front-end LNA gain is changed according to the measured RSSI value, keeping the first mixer input signal within a limited range. This improves the dynamic range of the receiver, improving performance in interference limited environments.

### 4.3 RF Transmitter

#### 4.3.1 IQ Modulator

The transmitter features a direct IQ modulator to minimise frequency drift during a transmit timeslot, which results in a controlled modulation index. Digital baseband transmit circuitry provides the required spectral shaping.

### 4.3.2 Power Amplifier

The internal PA has a maximum output power that allows BlueCore5-Multimedia External to be used in Class 2 and Class 3 radios without an external RF PA.

### 4.3.3 Transmit RF Power Control for Class 1 Applications (TX\_PWR)

An 8-bit voltage DAC, AUX\_DAC, controls the amplification level of the external PA for Class 1 operation. The DAC output is derived from the on-chip band gap and is virtually independent of temperature and supply voltage. Equation 4.1 and Equation 4.2 show the the output voltage:

$$V_{DAC} = \text{MIN} \left( \left( 3.7V \times \frac{\text{EXT\_PA\_GAIN}}{255} - 0.008 \times I \right), \text{PIOSupply} - 0.008 \times I \right)$$

Equation 4.1: Output Voltage with Load Current I

or

$$V_{DAC} = \text{MIN} \left( \left( 3.7V \times \frac{\text{EXT\_PA\_GAIN}}{255} \right), \text{PIO Supply} \right)$$

Equation 4.2: Output Voltage with No Load Current

Note:

$$\text{PIOSupply} = \text{VDD\_PIO}$$

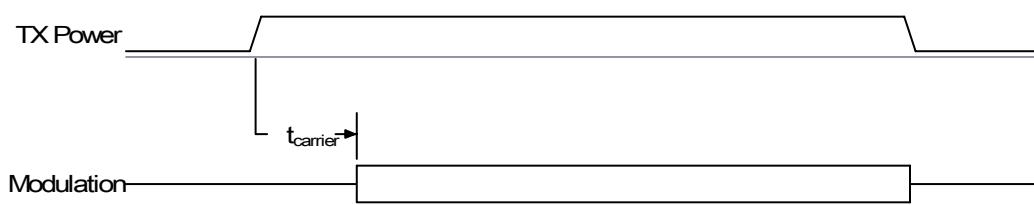

BlueCore5-Multimedia External enables the external PA only when transmitting. Before transmitting, the chip normally ramps up the power to the internal PA, then it ramps it down again afterwards. However, if a suitable external PA is used, it may be possible to ramp the power externally by driving the TX\_PWR pin on the PA from AUX\_DAC.

Figure 4.2: Internal Power Ramping

The PS Key PSKEY\_TX\_GAINRAMP, is used to control the delay, in units of  $\mu$ s, between the end of the transmit power ramp and the start of modulation.

PS Key TXRX\_PIO\_CONTROL controls external RF components such as a switch, an external PA or an external LNA. PIO[0], PIO[1] and the AUX\_DAC can be used for this purpose, as Table 4.1 shows.

| TXRX_PIO_CONTROL Value | PIO and AUX_DAC Use                                                                                                     |

|------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 0                      | PIO[0], PIO[1], and AUX_DAC not used to control RF. Power ramping is internal.                                          |

| 1                      | PIO[0] is high during RX, PIO[1] is high during TX. AUX_DAC not used. Power ramping is internal.                        |

| 2                      | PIO[0] is high during RX, PIO[1] is high during TX. AUX_DAC used to set gain of external PA. Power ramping is external. |

| 3                      | PIO[0] is low during RX, PIO[1] is low during TX. AUX_DAC used to set gain of external PA. Power ramping is external.   |

| 4                      | PIO[0] is high during RX, PIO[1] is high during TX. AUX_DAC used to set gain of external PA. Power ramping is internal. |

Table 4.1: TXRX\_PIO\_CONTROL Values

## 4.4 Bluetooth Radio Synthesiser

The Bluetooth radio synthesiser is fully integrated onto the die with no requirement for an external VCO screening can, varactor tuning diodes, LC resonators or loop filter. The synthesiser is guaranteed to lock in sufficient time across the guaranteed temperature range to meet the Bluetooth v2.1 + EDR specification.

## 4.5 Baseband

### 4.5.1 Burst Mode Controller

During transmission the BMC constructs a packet from header information previously loaded into memory-mapped registers by the software and payload data/voice taken from the appropriate ring buffer in the RAM. During reception, the BMC stores the packet header in memory-mapped registers and the payload data in the appropriate ring buffer in RAM. This architecture minimises the intervention required by the processor during transmission and reception.

### 4.5.2 Physical Layer Hardware Engine

Dedicated logic performs the following:

- Forward error correction

- Header error control

- Cyclic redundancy check

- Encryption

- Data whitening

- Access code correlation

- Audio transcoding

Firmware performs the following voice data translations and operations:

- A-law/μ-law/linear voice data (from host)

- A-law/μ-law/CVSD (over the air)

- Voice interpolation for lost packets

- Rate mismatch correction

The hardware supports all optional and mandatory features of Bluetooth v2.1 + EDR specification including AFH and eSCO.

## 4.6 Basic Rate Modem

The basic rate modem satisfies the basic data rate requirements of the Bluetooth v2.1 + EDR specification. The basic rate was the standard data rate available on the Bluetooth v1.2 specification and below, it is based on GFSK modulation scheme.

Including the basic rate modem allows BlueCore5-Multimedia External compatibility with earlier Bluetooth products.

The basic rate modem uses the RF ports, receiver, transmitter and synthesiser, alongside the baseband components described in Section 4.5.

## 4.7 Enhanced Data Rate Modem

The EDR modem satisfies the requirements of the Bluetooth v2.1 + EDR specification. EDR has been introduced to provide 2x and 3x data rates with minimal disruption to higher layers of the Bluetooth stack.

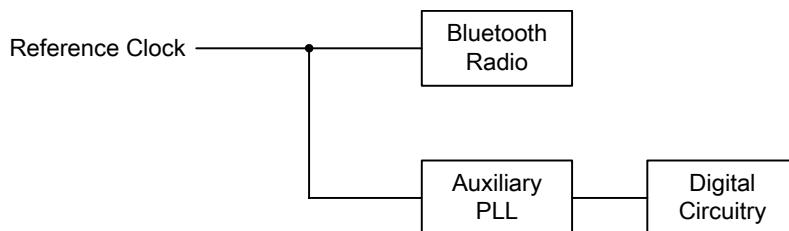

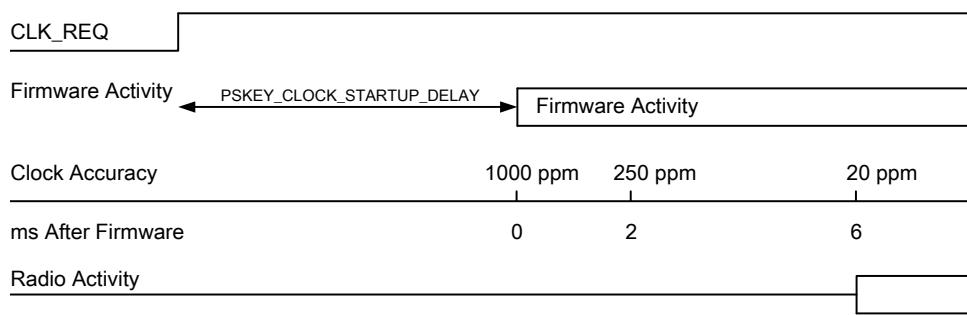

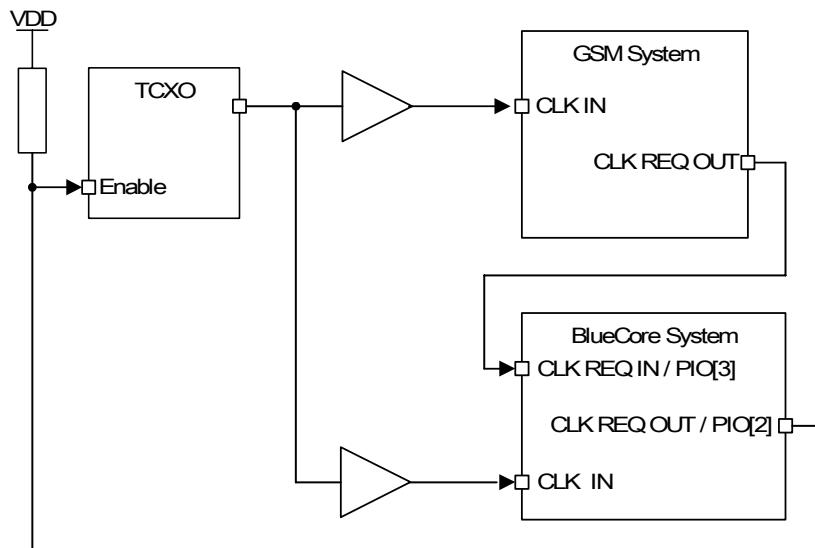

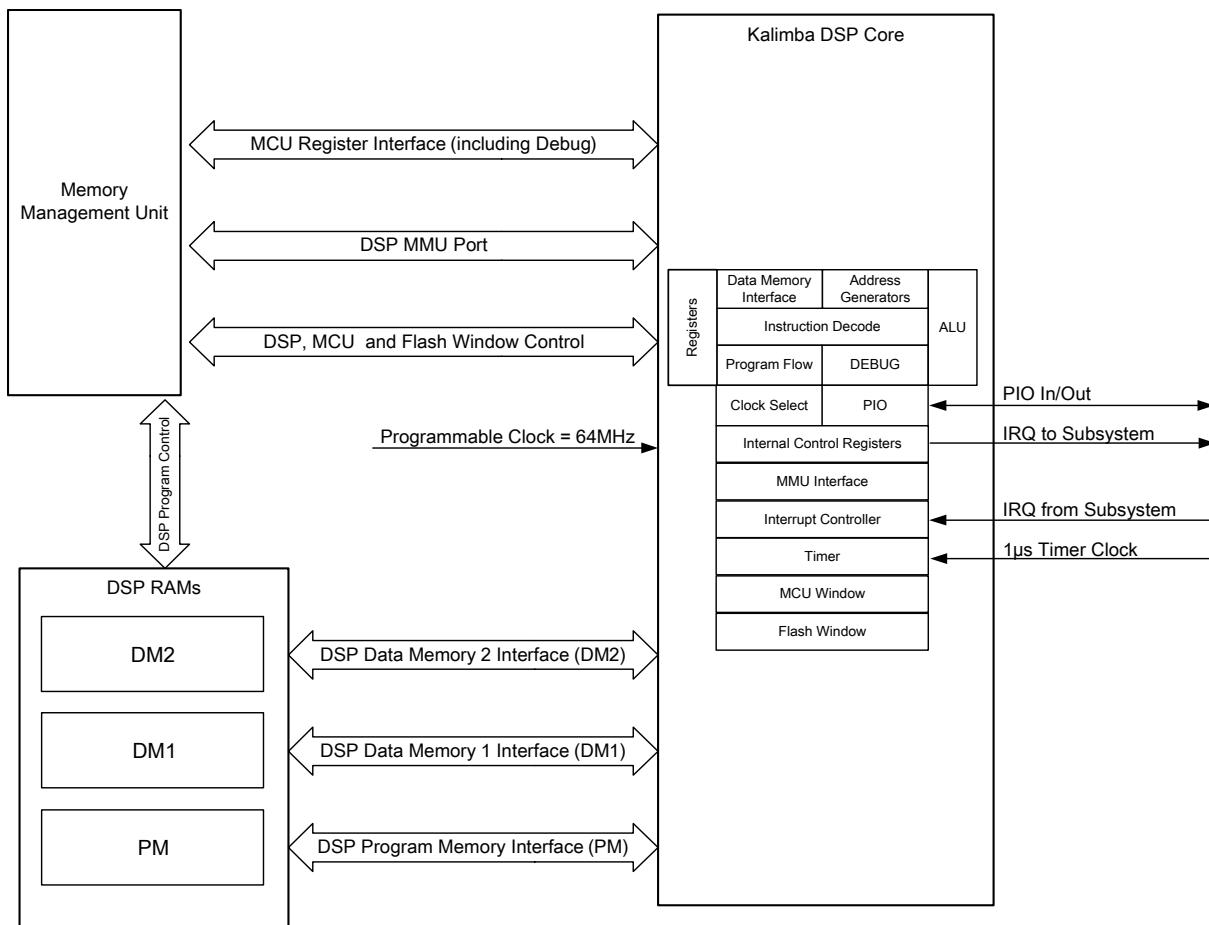

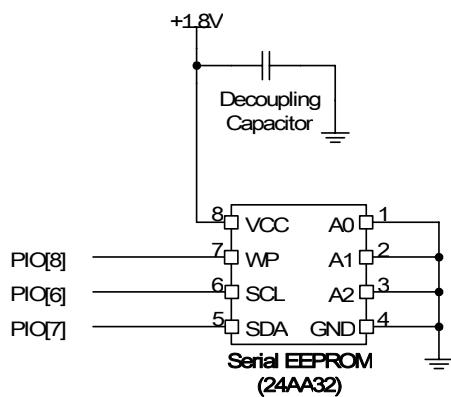

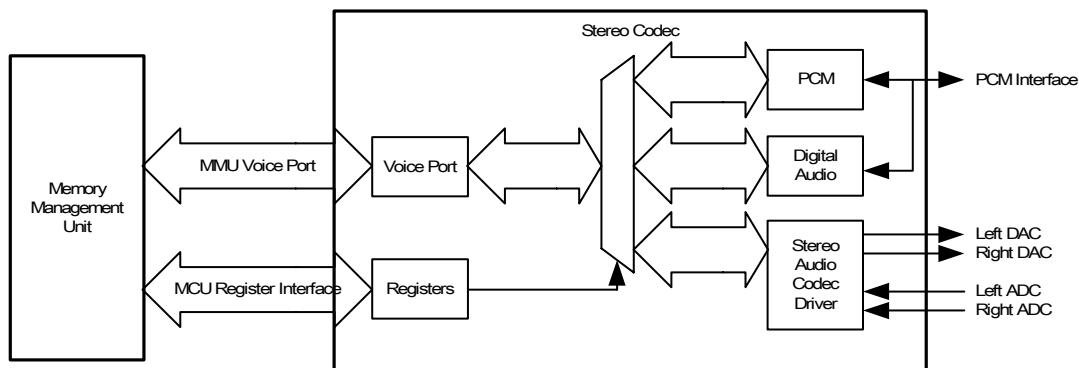

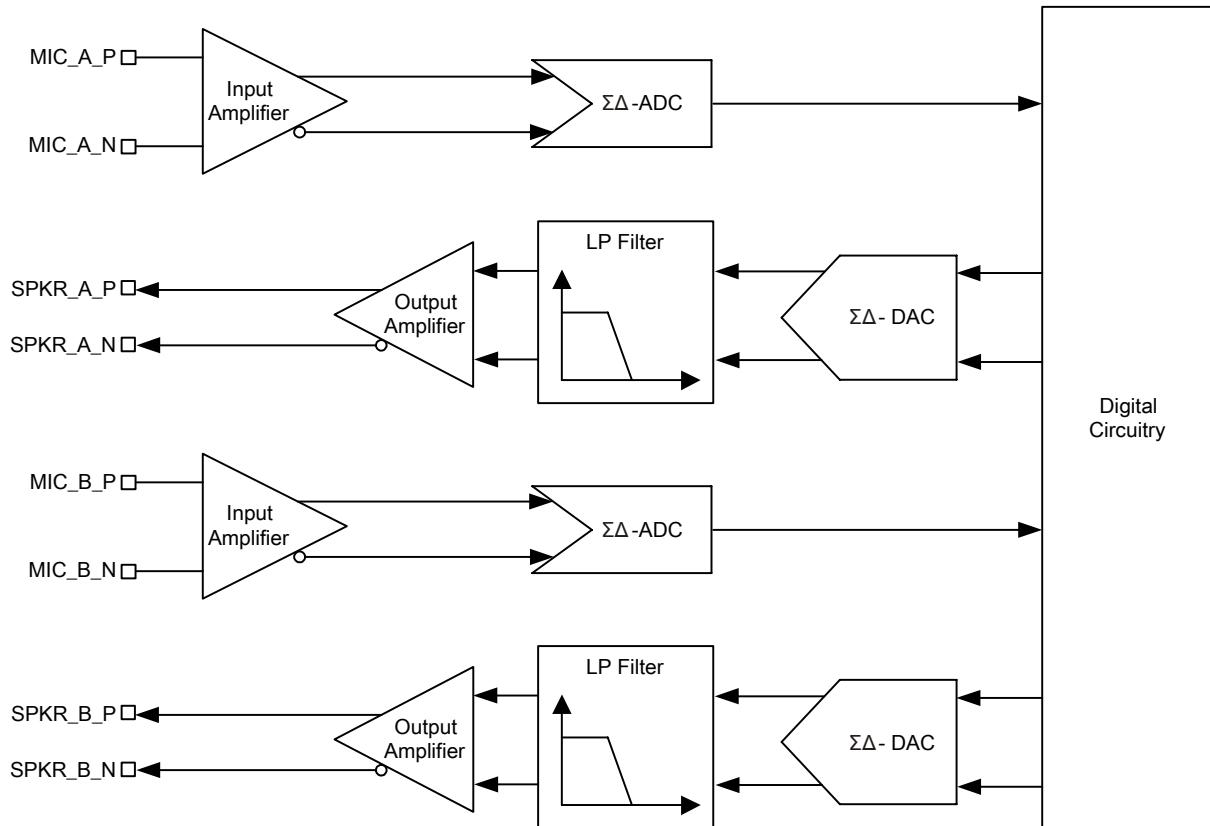

BlueCore5-Multimedia External supports both the basic and enhanced data rates and is compliant with the Bluetooth v2.1 + EDR specification.