# 基于 C8051F060 SOC 芯片的高频网络分析仪

干敏梁, 聂佰玲

(南京航空航天大学 民航学院, 江苏 南京 210016)

**摘要:** 介绍了一种 1 GHz 的智能化标量网络分析仪, 详细叙述了该系统的硬件设计和软件设计。该仪器采用 Cygnal 公司的专利 CIP51 微处理器内核的 C8051F060 单片机作为控制器, 使用锁相环+直接数字合成+下变频的方法构成扫频信号源, 用直接数字频率合成 (DDS) 芯片 AD9852 实现扫频信号的控制, 产生的扫频信号的范围为 1~1 000 MHz。该标量网络分析仪能方便地测试一个系统的传输特性和反射特性, 与 PC 机通过通用串行总线 (USB) 接口, 实现被测网络频率特性的图形显示、保存、打印及参数设置功能。充分利用了 C8051F060 内部的 ADC 和 DAC 及其他片内资源使得整个系统体积小, 重量轻, 低功耗, 性能稳定, 成本低, 具有较高的实用价值。

**关键词:** 网络分析仪; C8051F060; 直接数字频率合成 (DDS); 通用串行总线 (USB)

中图分类号: TM935.2 文献标识码: A 文章编号: 1000-8829(2006)S0-0271-03

## High Frequency Network Analyzer Based on C8051F060 SOC

GAN Min-Liang, NIE Bai-Ling

(College of Civil Aviation, Nanjing University of Aeronautics and Astronautics, Nanjing 210016, China)

**Abstract:** The software and hardware design of an intelligent, 1GHz scalar, network analyzer is described in the paper. By using C8051F060 to control DDS chip AD9852, using PLL + DDS + frequency changer as sweep frequency source, the output frequency range is up to 1000 MHz. The instrument is easy to measure the transport and reflect characteristic of the system. Connected PC with USB, the system can give, print, and save the frequency response curve. By full using ADCs and DACs on chip, the system has the characteristics such as small volume, little weight, and low cost, which make it more applicable.

**Key words:** scalar network analyzer; C8051F060 microcontroller; direct digital frequency synthesis(DDS); universal serial bus (USB)

美国 Cygnal 公司推出的 C8051F 系列单片机将 51 系列单片机从 MCU 级推向了 SOC 时代。其中 C8051F06X 更是集当前单片机最新发展技术于一身, 其功能已经完全达到板卡级水平。C8051F060 是高集成度的片上系统混合信号单片机, 它采用与 8051 兼容的 CIP51 专利微处理器内核, 速度高达 25MIPS, 有多达 59 个数字 I/O 口, 5 个 16 位通用定时器, 6 个带有捕捉/比较模块的可编程定时器/计数器, 8 路 10 位的 ADC (带可编程放大器和多路选择器), 2 路采样速率

收稿日期: 2006-05-17

作者简介: 干敏梁 (1945—), 男, 教授, 中国电子学会会员, 中国航空学会会员, 研究方向为电子信息处理及智能控制, 近年来在各级杂志发表论文 20 多篇; 聂佰玲, 女, 硕士研究生。

可达 1 MSPS 的 16 位 ADC, 2 路 12 位的 DAC, 3 个电压比较器, 1 个片内温度传感器和参考电压源, 内置串行口 SPI、Smbus/I<sup>2</sup>C 和 UART, 片上 CAN2.0B 控制器、看门狗定时器、电源监视器, 片内 JTAG 调试和边界扫描单元, 2.7~3.5 V 供电等。这些功能部件的高度集成, 为设计小体积、低功耗、高可靠性、高性能的单片机应用系统提供了很大的方便。本研究研制的网络分析仪采用 C8051F060 作控制核心, 使用锁相环+直接数字合成+下变频的方法构成扫频信号源, 其中直接数字频率合成用 AD9852 DDS 芯片实现, 产生的扫频信号的范围为 1~1 000 MHz。仪器配置 USB 接口, 可与 PC 机通信, 实现被测网络频率特性的图形显示、保存、打印及参数设置功能。

## 1 系统总体方案

### 1.1 硬件方案

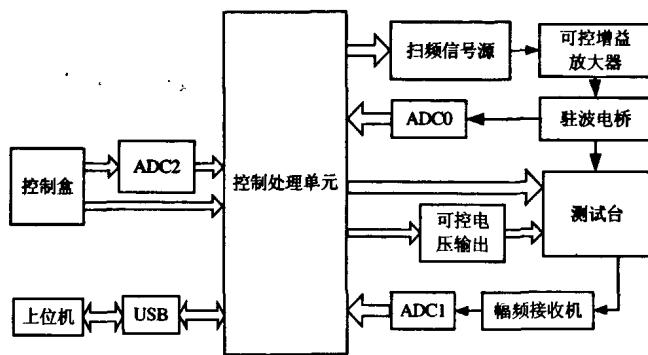

根据所要求的测试功能及技术指标, 确定系统由控制盒、测试台、上位机、扫频信号发生器、可控增益放大器、幅频接收机等部分组成, 如图1所示。

图1 系统总体框图

信号源电路由信号发生电路和信号调理电路组成。在系统中, 信号发生电路采用 DDS 技术(使用集成 DDS 芯片 AD9852) +PLL+下变频方式实现, 用于产生频率、持续时间等均可控的扫频信号; 信号调理电路主要是对信号中的噪声进行抑制并对输出信号的平坦度起到自动调节控制作用。

幅频接收机采用扫频外差接收机技术, 用 DDS(使用集成 DDS 芯片 AD9852) 技术产生一个跟踪输入频率变化的扫频信号, 与输入信号混频, 把高频信号搬到较低的中频上进行处理, 降低噪声, 同时降低后续处理难度。

控制处理单元 C8051F060 主要完成逻辑控制、数据采集、与人机接口部分通信 3 个主要功能, 控制整个系统的协调工作, 并对测量及人机接口部分来的数据进行分析处理。

上位机负责设置测量时扫频信号所需要的起始频率、终止频率、频率间隔、信号功率、工作电压等参数, 并将各种参数通过 USB 送给下位机; 上位机还负责设置显示方式、文字标注方式等。控制盒上安装了测量过程中的各种常用操作按键和电位器, 以方便操作和检修。

可控增益放大电路负责把扫频信号源的输出调整到测试所需的范围内(该初始范围由上位机设置)。

### 1.2 软件方案

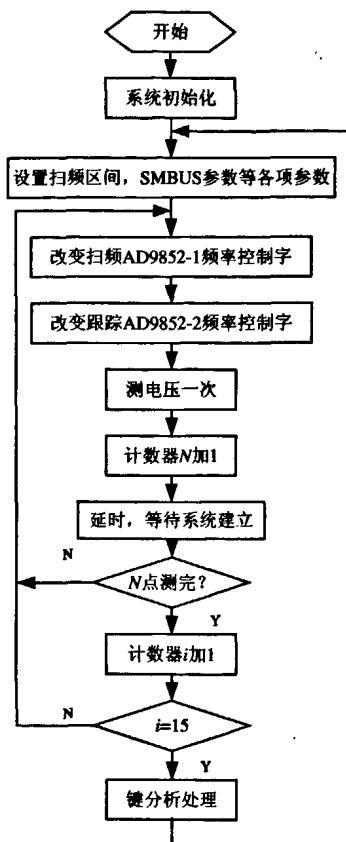

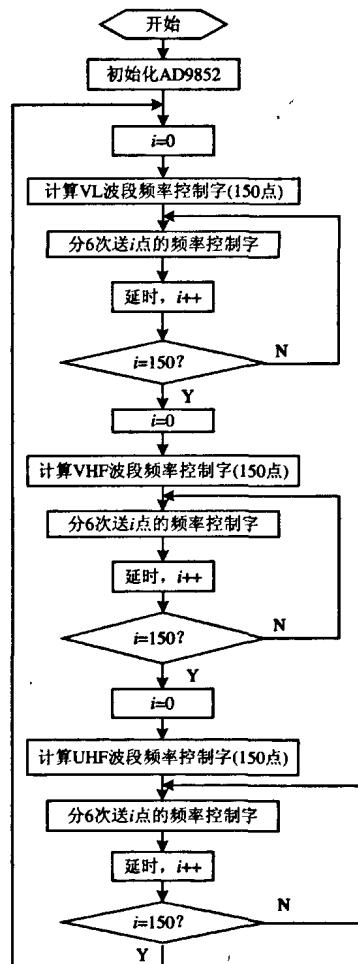

主程序流程如图 2 所示。主程序和子程序都存放在 C8051F060 单片机的 64 KB 的 FLASH 中。主程序的功能是负责开机后对芯片内数字资源(定时器、PCA、ADC、DAC、SMBUS) 和接口芯片的初始化, 接收通过 USB 传送过来的设置参数, 控制扫频信号源

进行扫频、键分析处理。

图2 主程序流程图

AD9852-1 控制扫频信号源的输出频率, AD9852-2 控制幅频接收机扫频本振的输出频率, 每输出一个频率点, 延时一段时间, 等待系统建立, 然后测量响应幅度。

系统设置 3 个中断: INT0 用来处理 USB 芯片的中断申请信号; INT1 用来处理控制盒 PLL 按键输入, 控制高频头断开或接通; 比较器下降沿中断用来处理频道上翻键(UP 键)、下翻键(DOWN)、镜像抗干扰键(MIR) 和显示方式切换键(L/L)。

## 2 扫频信号源设计

### 2.1 基于 DDS 的扫频信号源硬件组成

直接数字频率合成(DDS) 技术是一种采用数字控制振荡器(NCO, numerically controlled oscillator) 作为核心, 来产生频率可调的、幅度为数字量表示的正弦波。这些数字量表示的波形幅值再通过一个数模转换器(DAC), 就得到正弦波的模拟波形。它是在时域中进行频率合成, 从而能够对输出频率进行快速而且精确的控制, 并且这种控制全部都是数字控制, 可以提供非常高的频率精度。

本仪器的扫频信号源采用 ADI 公司的 DDS 芯片 AD9852 实现。AD9852 内含 300 MHz 时钟、高速高

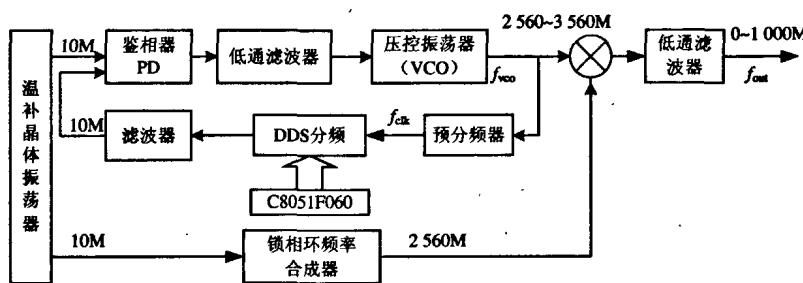

性能 D/A 转换器及高速比较器, 以形成可编程、可灵活使用的频率合成功能。外接精密时钟源时, AD9852 可以输出一个频谱纯净、频率和相位都可以编程控制且稳定性很高的模拟正弦波。但是, 因受限于器件可用的最高时钟频率, 致使合成频率不能太高。根据奈奎斯特定理, 其输出频率小于时钟频率的一半, 实际工作中 DDS 的最高输出频率为时钟频率的 40%。通常, 数字器件工作速率的提高, 器件成本和功耗都会大幅度地增加, 因此也限制了最高输出频率。本仪器若只是简单地使用 DDS 方式, 是不能满足对扫频范围要求的。同时考虑到信号在很宽的频带内, 谐波分量和杂散分量滤除的难易程度, 最终选择 DDS+PLL+倍频+下变频的混合频率合成方式。原理框图如图 3 所示。

图 3 扫频信号源框图

本系统是将 DDS 作为 PLL 回路的可编程的分频器。其分频系数可在  $1/2 \sim 1/2^N$  之间变化, 实现分辨率很高的小数分频, 考虑到 PLL 频率合成器常用于高频振荡源, 而 DDS 作为分频器, 其工作频率上限不可能太高, 因此, 在 DDS 分频之前, 先经过 32 分频, 通过控制 DDS 改变分频系数使压控振荡器的输出实现从 2 560 MHz 到 3 560 MHz 的输出, 再与 2 560 MHz 本振信号 (由 MPS2560 产生) 混频, 经过低通滤波器滤除不需要的高频分量, 从而实现了 1~1 000 MHz 的全景扫频。

## 2.2 扫频信号源控制软件流程

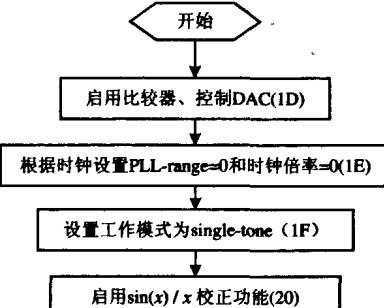

由于本仪器中, 频率控制字经常需要按用户设定变动, 故选择 Single-Tone 工作模式, 这种方式控制灵活, 修改方便。

AD9852 的频率控制字为:

$$FTW = \frac{f_0 \times 2^{48}}{f_{\text{clk}}} = \frac{f_0 \times 2^{48}}{\frac{1}{32} f_{\text{vco}}}$$

式中,  $f_{\text{vco}}$  为压控振荡器的输出,  $f_{\text{vco}} = f_{\text{out}} + 2560 \text{ MHz}$ ;  $f_0$  为 DDS 送鉴相器 PD 的输出, 固定为 10 MHz。根据需要的  $f_{\text{out}}$  算出  $f_{\text{vco}}$ , 然后由上式得到频率控制字 FTW, FTW 值取舍为整数转变为 16 进制数后写入频率控制字寄存器。

写 AD9852 的频率控制字, 开始时由于送入 AD9852 的参考时钟并不是 10 MHz 所需要的, 此时 AD9852 的输出不是 10 MHz, 锁相环进行调整, VCO 输出改变, 直到达到设定 FTW 时所对应的  $f_{\text{vco}}$ 。即所需要的 1~1 000 MHz 的输出。程序中按照用户设定的扫频方式或系统默认的扫频方式不断对频率控制字进行写入, 从而得到所需要的扫频信号。AD9852 的初始化和扫频调试程序流程如图 4 和图 5 所示。

图 4 AD9852 初始化流程图

图 5 扫频信号源控制程序流程图

(下转第 277 页)

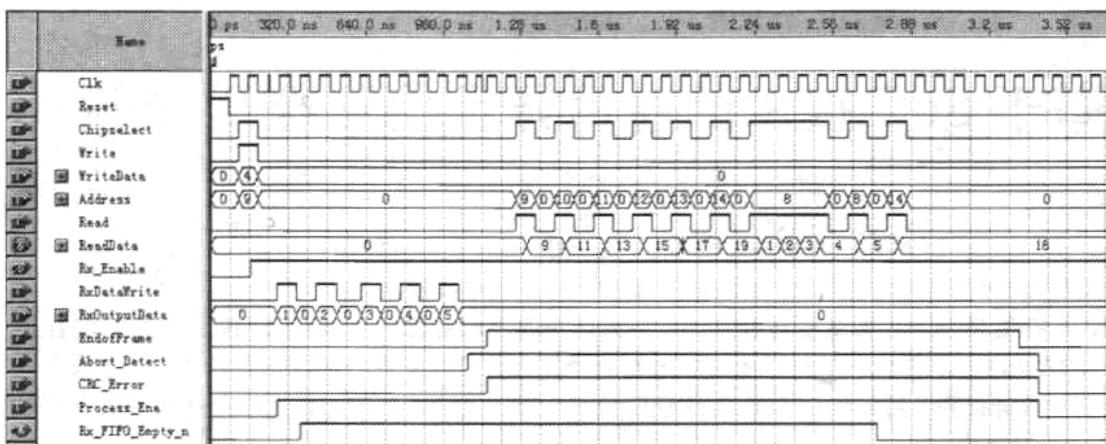

图 8 接口模块时序仿真波形

(2) 连接数据发送、接收引脚, 实现数据收、发片外环回;

(3) 使用 Nios II 处理器向发送缓存区写入序列: 1, 2, …, 201, 启动数据发送;

(4) 循环查询 EndofFrm 状态寄存器, 等待 HDLC 控制器接收完毕;

(5) 接收完毕后, 处理器读出接收缓存区中的数据和各状态寄存器值。

在 Nios II IDE 中查看接收缓存区中数据, 结果为 1, 2, …, 201, 213, 142, 0, …, 0 (共 98 个“0”)。其中 1-201 是接收到的数据, 213 和 142 是 CRC 校验码, 各状态寄存器的输出值也与期望值相一致。

测试结果表明所设计电路能正确完成 HDLC 协议处理。

#### 参考文献:

- 1] 陆国华. 多通道高速 HDLC 处理器的设计与实现[J]. 电子学报, 2003, 31(11): 1 630 - 1 633.

- 2] Chen He. ASIC design of high-speed low-power HDLC controller[J]. Journal of Beijing Institute of Technology, 2003, 12(S0): 66 - 69.

- 3] 潘松. SOPC 技术实用教程[M]. 北京: 清华大学出版社, 2005.

- 4] 王喜. HDLC 的 FPGA 实现方法[J]. 通信与广播电视, 2005, (3): 23 - 29.

- 5] 韩露. 专用 HDLC 协议芯片的应用[J]. 移动通信, 2003, (S0): 231 - 232.

(上接第 273 页)

### 3 结束语

本仪器充分利用了 C8051F060 SOC 内部的 ADC、DAC 及其他片内资源, 满足了系统所需的大量的数据采集、转换与控制功能要求; 采用了先进的可编程直接数字频率合成 (DDS) 芯片 AD9852; 使用了混合式频率合成技术: 锁相环+直接数字合成+下变频的方法构成扫频信号源。设计与调试结果表明, 整个系统体积小, 重量轻, 低功耗, 性能稳定, 成本低, 具有较高的实用价值。

#### 参考文献:

- [1] Silicon Laboratories Inc. Mixed Signal ISP Flash MCU Family C8051F060/1/2/3/4/5/6/7[Z]. 2004.

- [2] Analog Devices Inc. CMOS 300 MSPS Complete-DDS AD9852 Data Sheet[Z]. 2002.

- [3] Rahkonen T, Eksyma H, Mantyniemi A, et al. A DDS

synthesizer with digital time domain interpolator[J]. Analog Integrated Circuits and Signal Processing, 2001, 7(1): 111 - 118.

- [4] Bonfanti A, Amorosa F, Samori C, Lacaita A L. A DDS-based PLL for 2.4GHz frequency synthesis[J]. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 2003, 5(12): 1007 - 1010.

- [5] 聂信玲. 基于 DDS 技术的 1MHz 标量网络分析仪研制[D]. 南京: 南京航空航天大学, 2006.

- [6] 潘琢金, 孙德龙, 夏秀峰. C8051F 单片机应用解析[M]. 北京: 北京航空航天大学出版社, 2002.

- [7] 杨俊安, 钟子发. 采用 DDS+PLL 结构的分析接收机频率合成器的研究与实现[J]. 无线电通信技术, 2000, 26(3).

- [8] 吴捷, 王刚. DDS 在低频矢量网络分析仪中的应用[J]. 电子工程师, 2002, 28(7).

- [9] 陈光福, 王厚军, 田书林. 现代测试技术[M]. 成都: 电子科技大学出版社, 2002.

## 微波射频测试仪器使用操作培训

易迪拓培训([www.edatop.com](http://www.edatop.com))由数名来自于研发第一线的资深工程师发起成立, 致力并专注于微波、射频、天线设计研发人才的培养; 现已发展成为国内最大的微波射频和天线设计人才培养基地, 推出多套微波射频以及天线设计培训课程, 广受客户好评; 并先后与人民邮电出版社、电子工业出版社合作出版了多本专业图书, 帮助数万名工程师提升了专业技术能力。客户遍布中兴通讯、研通高频、埃威航电、国人通信等多家国内知名公司, 以及台湾工业技术研究院、永业科技、全一电子等多家台湾地区企业。

易迪拓培训课程列表: <http://www.edatop.com/peixun/rfe/129.html>

### 微波射频测量仪器操作培训课程合集

搞硬件、做射频, 不会仪器操作怎么行! 对于射频工程师和硬件工程师来说, 日常电路设计调试工作中, 经常需要使用各种测试仪器量测各种电信号来发现问题、解决问题。因此, 熟悉各种测量仪器原理, 正确地使用这些测试仪器, 是微波射频工程师和硬件工程师必须具备和掌握的工作技能, 该套射频仪器操作培训课程合集就可以帮助您快速熟悉掌握矢量网络分析仪、频谱仪、示波器等各种仪器的原理和使用操作…

课程网址: <http://www.edatop.com/peixun/rftest/vna/67.html>

### 矢量网络分析仪使用操作培训课程套装

矢量网络分析仪是最常用的测试仪器是射频工程师和天线设计工程师最常用的测试仪器; 该套培训课程套装是国内最专业、实用和全面的矢量网络分析仪培训教程套装, 包括安捷伦科技和罗德施瓦茨公司矢量网络分析仪的 5 套视频培训课程和一本矢网应用指南教材, 能够帮助微波、射频工程师快速地熟悉掌握矢量网络分析仪使用操作…

课程网址: <http://www.edatop.com/peixun/rftest/vna/34.html>

### 示波器使用操作培训课程套装

示波器是硬件和射频工程师几乎在每天的工作中都会用到仪器, 因此掌握示波器的原理并能够正确使用示波器是所有从事电子硬件电路设计和调试的工程师必须具备的最基本的技能。本站推出的示波器视频培训课程套装既有示波器的基本原理以及示波器性能参数对测量结果影响的讲解, 也有安捷伦和泰克多种常用示波器的实际操作讲解, 能够帮助您更加深入地理解手边常用的示波器从而更加正确地使用示波器…

课程网址: <http://www.edatop.com/peixun/rftest/osc/49.html>