- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PLL的电源管理设计(三)

录入:edatop.com 点击:

LDO滤波

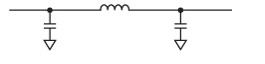

要改善LDO噪声,通常有两种选择:使用具有更少噪声的LDO,或者对LDO输出进行后置滤波。当无滤波器的噪声要求超过经济型LDO的能力时,滤波选项可能是不错的选择。简单的LC π 滤波器通常足以将带外LDO噪声降低20 dB(图5)。

图5.用于衰减LDO噪声的LCπ滤波器

选择器件时需要非常小心。典型电感为微亨利范围内(使用铁氧体磁芯),因此需要考虑电感数据手册中指定的饱和电流(ISAT), 作为电感下降10%时的直流电平。VCO消耗的电流应小于ISAT. 有效串联电阻(ESR) 也是一个问题,因为它会造成滤波器两端的IR压降。对于消耗300 mA直流电流的微波VCO,需要ESR小于0.33 ?的电感,以产生小于100 mV的IR压降。较低的非零ESR还可抑制滤波器响应并改善LDO稳定性。为此,选择具有极低寄生ESR的电容并添加专用串联电阻可能较为实际。上述方案可使用可下载的器件评估器如NI Multisim?在SPICE 中轻松实现仿真。

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:Allegro新建封装时无法添加PIN,是何原因?谢谢!

下一篇:聘PCB & Package设计工程师---外企(上海张江)