- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

allegro 敷铜问题请教

1) 动态敷铜的时候,可以自己画多边形(polygon),也可以使用z-copy命令,拷贝一个图形过来。

option里面的参数设置都是一样; dynamic copper, net name == AGND, line 45

我在使用这两种方式的时候,发现后者产生的岛无法删除 (使用delete island命令),这是怎么回事?

2)在敷铜的时候,如何定义多边形的转角处为圆弧拐角?有没有在哪里可以设置的,在使用polygon命令的时候,里面的Arc选项直接画出来圆弧,非我所想,我只是希望拐角的时候出现圆弧。

3)有两个元件的引脚连接到AGND,我并没有使用连线连接,只是把他们使用铜皮连接,当然铜皮的网络名称是AGND,但是在检查的时候 (unconnected pins report),总是提示这两个引脚没有连接,不知道这会不会影响最后出光绘文件?DRC是没有错误的。不知道有没有人遇到类似的情况,这是什么原因造成的呢?

4)敷铜的时候,静态和动态怎么选择呢?动态敷铜之后的形状很不规则,是不是需要后期调整啊,也很繁琐。

5)各位在布板的时候,是不是需要把各个平面的位置先试着摆开看看,要不,后期出来的铜皮效果杂乱不堪,有没有什么好的经验,介绍一下吧。

问题很多,最近被这块板子折腾的厉害。

QQ1289992389愿意解答你的问题,共同学习。

1. 如果这个情况在任何地方都能复现,大概是软件的bug,不妨升级一下软件到最新的补丁,可能会解决问题。如果问题依旧,可以的话,把问题复现的案例发给我,我报给Cadence原厂。另,印象中早期版本的Allegro是有一些动态铜皮的bug,新版本会好一些;我这边的软件16.5版本不能复现你的问题。

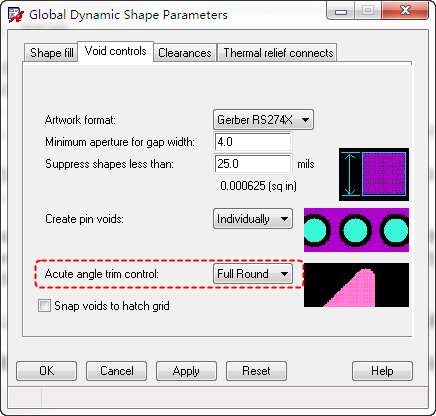

2. 可以直接在全局铜皮属性中修改“Acute angle trim control”为“Full Round”

3. 可能是你铜皮没有正确包裹管脚,如果铜皮选择全连接,铜皮的形状需要包裹管脚的中心点才会被认为两者相连;如果是使用花焊盘链接,需要花焊盘的设置和铜皮的形状满足对应的条件,才会有花焊盘幅线与管脚相连,不妨update动态铜皮到smooth,看是否相连;

4. 静态的好处主要是可以保护铜皮不被推挤影响以及在超大规模的设计中提高一些速度,正常情况下还是推荐动态,方便得多;

5. 布局前和布局时,本身就要了解整个板子的主要电源分布,在确定布局时,一般电源分割的方案已经有数了。

学习!

非常感谢小编的详细解答。

关于不能删除孤岛的那个问题,依然存在。估计是软件bug吧。

关于两个引脚没有连接的问题, 是我自己的疏忽, 我在敷铜的时候,有一块铜虽然定义为AGND,但是没有和其他的AGND连接在一起,所以一直报告这两个引脚没有连接上。

不知怎么回事,我现在发不了贴!在你后面更一下问题,希望小编谅解。

我用的是allegro 16.3 ,大面积铺铜时,不避让其他网络的过孔。不知是怎么回事?

铺的是动态铜不知道怎么搞的走线过孔都不避让,怀疑变成了静态铜,就重新铺了一遍(Z-COPY—>option中选择ETCH->TOP后,勾选create dynamic shape),问题还是存在。我已给铺铜分配了网络。求大侠指点指点

小编问题应该是动态铜应该是不能删除孤岛的,到后期修改完成后在转换成静态铜然后再删除。 6 楼的问题不是软件没有闭让啊,是你的设置没改,软件已经闭让了,而且没有DRC呢。在菜单shape的Global...然后看看shape fill中的dynamic fill 好象是选头1个我忘记了要不然就是第2个