- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDR3布线时的一些疑惑,求指导

录入:edatop.com 点击:

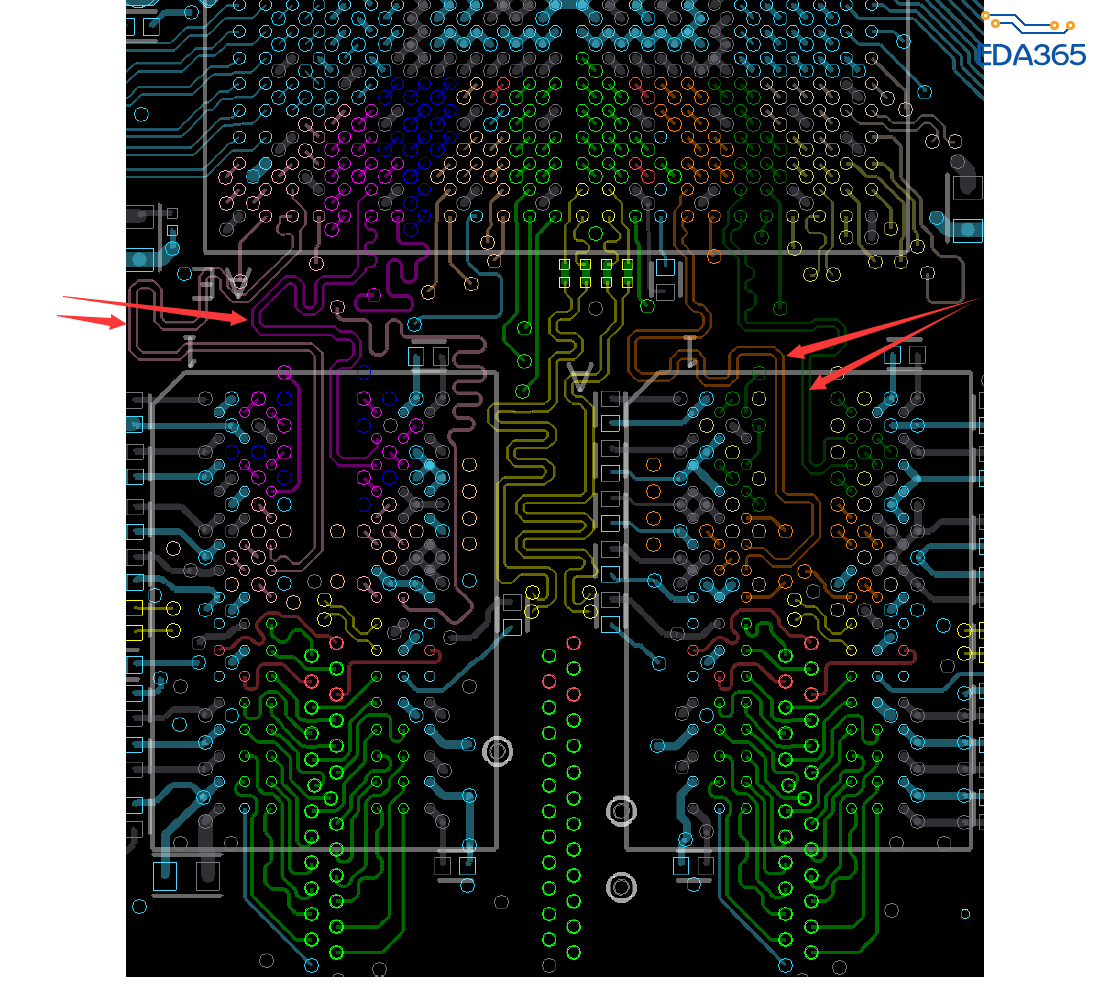

各位大师下午好,小弟最近在研究DDR3布线,也尝试自己动手实际练习,但是在布线的时候发现了一些比较让我疑惑的问题,首先,按照分组,很多文档上面都说分组的11根线都要求在同一个平面上,但是小弟在看芯片推荐布线手册的时候发现DQS+,-都布在了表层,跟另外9根线都不在同一个平面上,我的理解是为了方便做差分阻抗。不知道我的理解对不对,还有就是如果这样说的话是不是说这分组上面的线其实只要求数据线在同一个平面上面就行了呢?还请各位大师有空的话帮我理解一下这个问题。

小弟在补充一下图片。图片上面箭头指的,是DQS+-。

内层可能没有空间了,所以DQS+,-都布在了表层。同组同层也是为了控制时序方便,如果没有时序问题,那倒没关系。

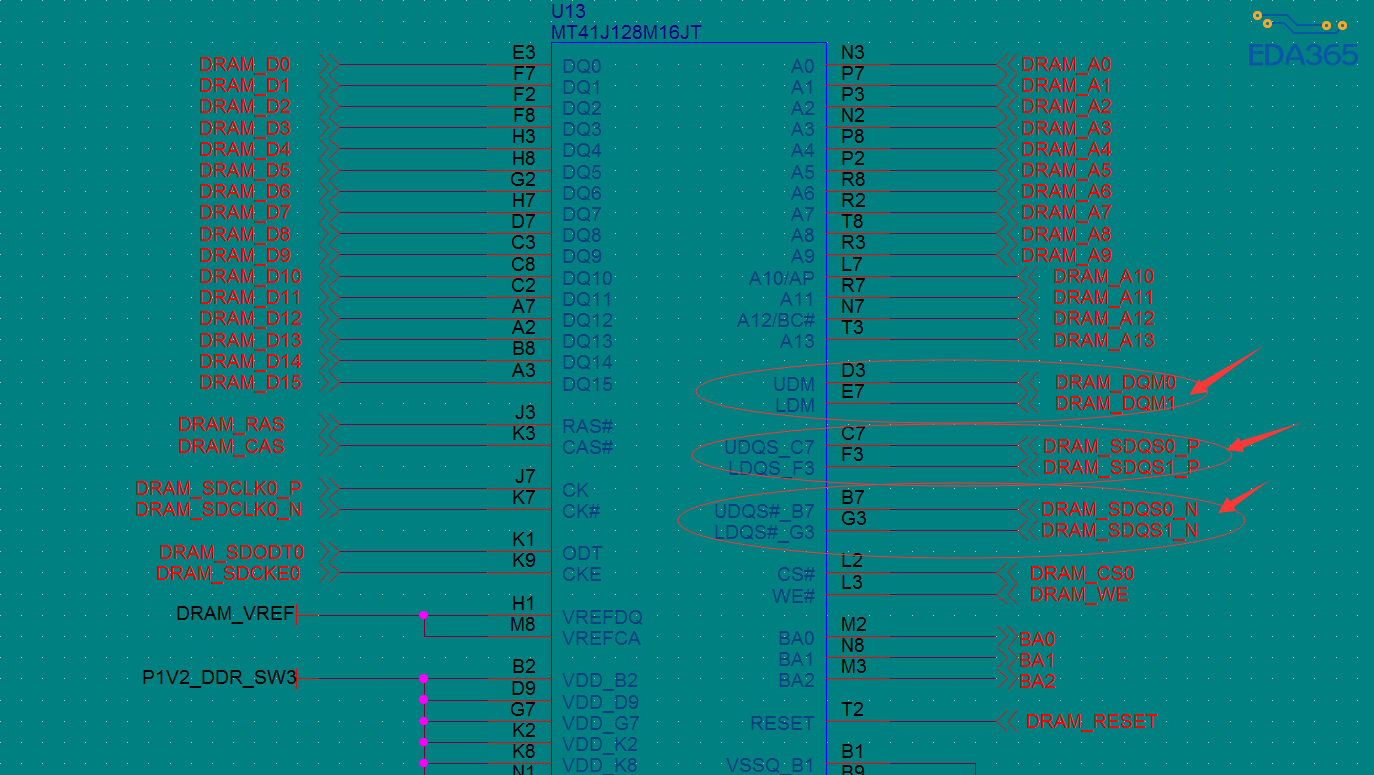

感谢小编大人的回复,还想请教一下,我自己阅读手册发现,这可能是一个64位的布线,底层应该还有两个DDR3芯片,只是没有画出来,而且中间还少了一层,手册也是坑爹啊,该是飞思卡尔官网下载的的。坑。

如果我想组成一个32位的系统,那么我这种连接方式是否正确呢?

DDR这边没有问题。

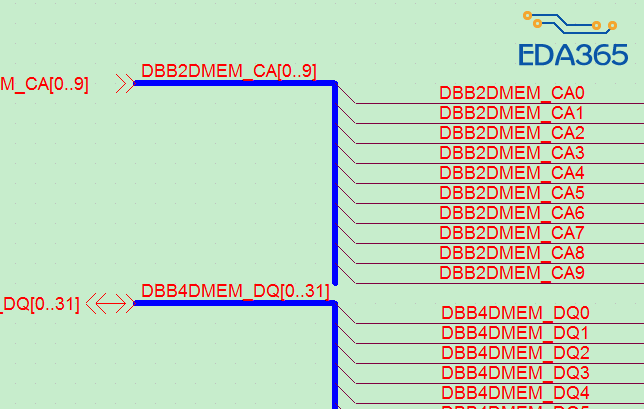

谢谢小编大人的回复,最后一张MCU部分的图,我感觉也应该没有问题的。还麻烦小编大人也顺便看一下吧。谢谢了~~

目测MCU侧也没有问题,建议数据和地址用总线连接比较好

MCU没什么问题,不过有的厂商会要求将无用的DQS管脚端接,具体参考datasheet。

好的,谢谢小编的回复和热心提醒,我会再去读一读手册的,谢谢!

我不知道为什么,总线老是连不上。DRC的时候总是提示我错误,我看错误显示的就是未连接,所以我就一直是这种接线方式。

总线在连接的时候要写上网络标号,like this

好的,谢谢!我试试去!

小编你的等长怎么的做的 加个好友企鹅202980656 向你请教

其实我的等长也调的不太好,很多细节还是没有考虑到,我也是在练手。要向大师们请教。

加个好友一起学习呗,想你请教1204094381

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:零件文字不小心删除框-16.6新指令解决

下一篇:板卡多次刷机后识别不了USB