- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

再次遇到奇怪的问题

录入:edatop.com 点击:

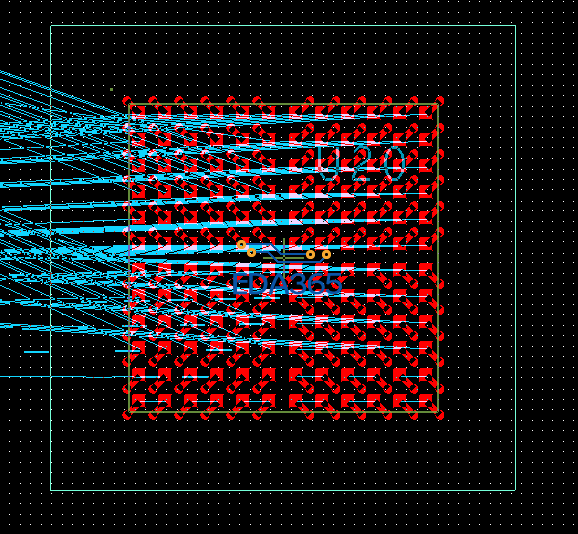

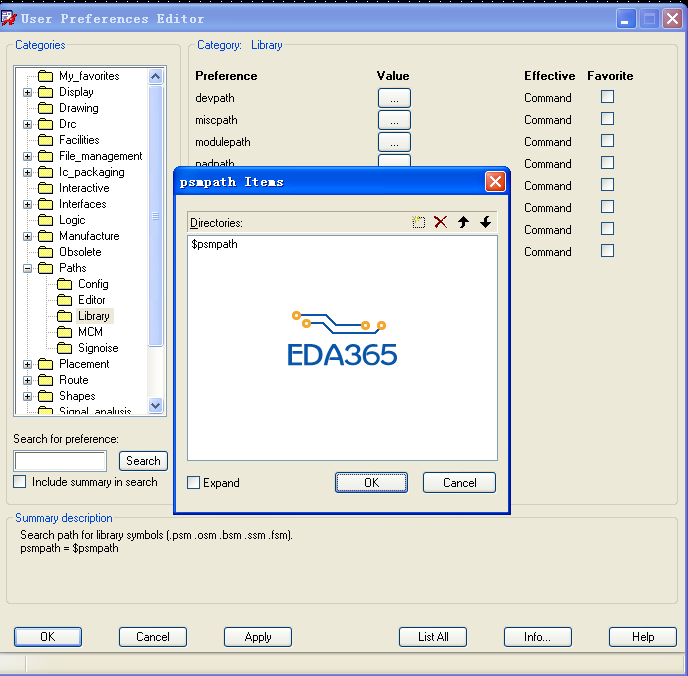

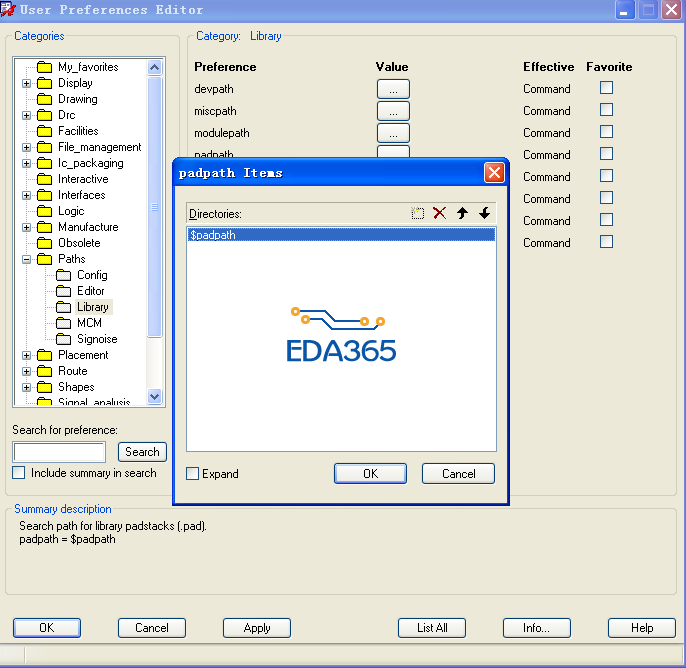

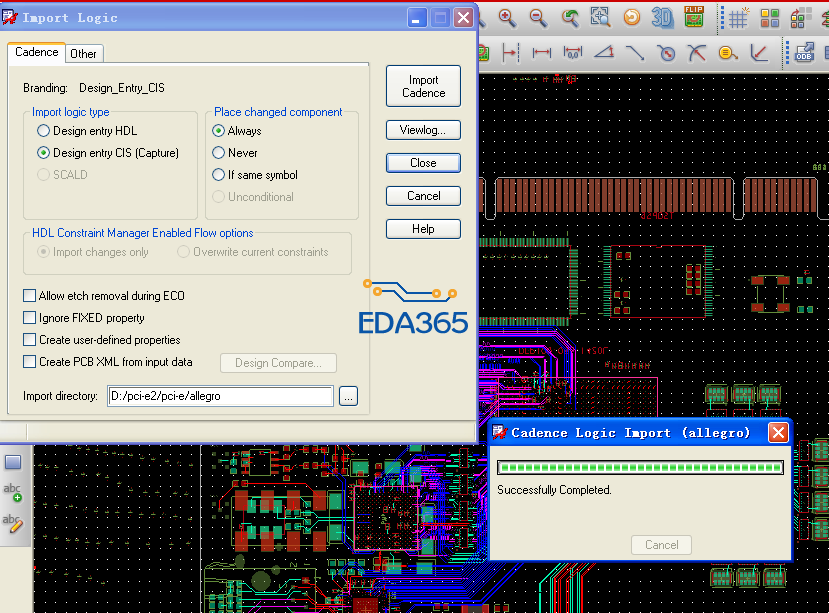

第一张图片是我最近画的pcb板,当中我觉得一个电源器件LTM6414的PLACE_BOUND_TOP太大了,决定把它改小点。从第二张图片你可以看到它有多大。然后我自己重新做了一个。将制作的封装和焊盘,psm与dra文件放入封装库中。重新导入网表,发现LTM6414的place_bound_top并没有改变,还是原来那么大,注意一看,整个封装还是以前的样子,整个都没改变。后来更加诡异的事情发生了,我在ALLEGRO中将库目录清空,如图,再次导入网表(一般这种情况肯定会出错的,因为没有库的支持啊),发现导入网表成功了,很是令我费解啊,丈二的和尚摸不着头脑,不知道怎么回事,希望大家帮我指点指点。

大家帮忙看看吧

o(╯□╰)o你得搞清楚你的目的,是更新元件封装,OK?不是导入网表。而且,当你第一次PCB封装齐全后,封装就会存在于.brd文件中,你下次可以更新网表,它用的是brd文件中的封装讯息。所以,你改封装后,要做的是place->update sybols

二樓說的明白 .

樓主您沒把這個關係給搞清楚 , 導致一直在那裡轉圈圈.

LZ没搞清自已要干吗,也没弄清这个软件的特性!

1.PLACE_BOUND_TOP作为一种铜皮也是可以在板子里面修的。

2.如果通过修改封装,指定库后,在板子里面更新封装也ok的。

非常感谢!

是啊 呵呵 这个关系我还真没弄明白 谢谢你们的热心解答 非常感谢

嗯嗯 说的是

再次谢谢大家,你们帮我解决了很长时间困扰我的问题 Thank you !

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:ALLEGRO16.3导入网表还没布线就有一部分网络已经布好了是什么原因?

下一篇:求教allegro制作不规则形状外形?