- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

allegro导入网表错误 大侠们帮分析分析

(---------------------------------------------------------------------)

( )

( Allegro Netrev Import Logic )

( )

( Drawing : JC0047EKT2132.brd )

( Software Version : 16.5P002 )

( Date/Time : Wed Sep 19 10:30:51 2012 )

( )

(---------------------------------------------------------------------)

------ Directives ------

RIPUP_ETCH FALSE;

RIPUP_DELETE_FIRST_SEGMENT FALSE;

RIPUP_RETAIN_BONDWIRE FALSE;

RIPUP_SYMBOLS ALWAYS;

Missing symbol has error FALSE;

SCHEMATIC_DIRECTORY 'F:\SPB16.5EKT2132\SCH\ALLEGRO';

BOARD_DIRECTORY 'F:/spb16.5EKT2132/SCH/allegro';

OLD_BOARD_NAME 'F:/spb16.5EKT2132/SCH/allegro/JC0047EKT2132.brd';

NEW_BOARD_NAME 'F:/spb16.5EKT2132/SCH/allegro/JC0047EKT2132.brd';

CmdLine: netrev.exe -5 -y 1 -n -i

F:\SPB16.5EKT2132\SCH\ALLEGRO

F:\spb16.5EKT2132\SCH\allegro\JC0047EKT2132.brd

F:\spb16.5EKT2132\SCH\allegro\JC0047EKT2132.brd

------

Preparing to read pst files ------

Starting to read

F:/SPB16.5EKT2132/SCH/ALLEGRO/pstchip.dat

Finished reading F:/SPB16.5EKT2132/SCH/ALLEGRO/pstchip.dat (00:00:00.10)

Starting to read F:/SPB16.5EKT2132/SCH/ALLEGRO/pstxprt.dat

Finished reading F:/SPB16.5EKT2132/SCH/ALLEGRO/pstxprt.dat (00:00:00.00)

Starting to read F:/SPB16.5EKT2132/SCH/ALLEGRO/pstxnet.dat

Finished reading F:/SPB16.5EKT2132/SCH/ALLEGRO/pstxnet.dat (00:00:00.00)

------

Oversights/Warnings/Errors ------

ERROR: File "JC0047EKT2132.brd" was locked on date "Wed Sep 19 10:28:39 2012" by

user "toshiba" on system "TOSHIBA-PC".

Resolve lock file and re-run netrev.

#1 ERROR(SPMHNI-175): Netrev error detected.

#2 Run stopped because errors were detected

netrev

run on Sep 19 10:30:51 2012

DESIGN NAME : 'EKT2132'

PACKAGING ON Apr 21 2011 10:02:30

COMPILE 'logic'

CHECK_PIN_NAMES OFF

CROSS_REFERENCE OFF

FEEDBACK OFF

INCREMENTAL OFF

INTERFACE_TYPE PHYSICAL

MAX_ERRORS 500

MERGE_MINIMUM 5

NET_NAME_CHARS '#%&()*+-./:=>?@[]^_`|'

NET_NAME_LENGTH 24

OVERSIGHTS ON

REPLACE_CHECK OFF

SINGLE_NODE_NETS ON

SPLIT_MINIMUM 0

SUPPRESS 20

WARNINGS ON

2 errors detected

No oversight detected

No warning detected

cpu time

0:00:32

elapsed time 0:00:00

大侠们帮看看,先谢过。

自学习allegro以来,还未成功导入到网表,走过路过的各位大侠一定要帮帮忙啊

路径没设置好,还有封装没对应上。

请帮忙看看,封装有问题是跟这个有关系吗?

在pstchip.dat里面,我自己做的一个6PIN的连接器,提示PINUSE=UNSPEC:

primitive 'CONN_6PIN_CONN_6_CONN_6PIN';

pin

'1':

PIN_NUMBER='(1)';

PINUSE='UNSPEC';

'2':

PIN_NUMBER='(2)';

PINUSE='UNSPEC';

'3':

PIN_NUMBER='(3)';

PINUSE='UNSPEC';

'4':

PIN_NUMBER='(4)';

PINUSE='UNSPEC';

'5':

PIN_NUMBER='(5)';

PINUSE='UNSPEC';

'6':

PIN_NUMBER='(6)';

PINUSE='UNSPEC';

end_pin;

body

PART_NAME='CONN_6PIN';

JEDEC_TYPE='CONN_6';

VALUE='CONN_6PIN';

end_body;

如果是,要怎么改?

PIN没有定义名字吧。换个PIN类型试,PASSIVE...

错误提示:

ERROR: File "JC0047EKT2132.brd" was locked on date "Wed Sep 19 10:28:39 2012" by , S2 E0 X4 C0 p5 C5 b

user "toshiba" on system "TOSHIBA-PC".8 v* i0 W& s1 F+ _% d5 Z! m- t

Resolve lock file and re-run netrev.

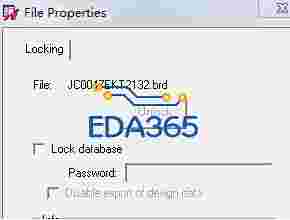

说明"JC0047EKT2132.brd"文件被锁定了,要到File->Properties解锁,如果有密码还需要输入密码才能解。

自己弄了半天,情况变这样了:

直接从Orcad直接传递网表到pcb edit,就会报错中断。如果单从orcad里导出网表,再在pcb edit里面import logic,就可以导入网表和封装。不过IC的引脚方向变了,全部重叠到一起了

错乱了。

错误提示:

ERROR: File "JC0047EKT2132.brd" was locked on date

"Thu Sep 20 13:14:53 2012" by user "toshiba" on system "TOSHIBA-PC".

Resolve lock file and re-run netrev.

按提示,是brd文件被锁定了,进入file--properties. unlock是灰色的,而且我此前没设定过密码锁定。

同问!

WARNING(SPMHNI-192): Device/Symbol check warning detected.

WARNING(SPMHNI-337): Unable to load symbol 'SIP2-4' for device 'CAP POL_SIP2-4_470UF': WARNING(SPMHUT-127): Could not find padstack PAD1_5D1_1.

due to ERROR(SPMHDB-274): Unable to load flash symbol F150_180_070 (Check PSMPATH setting for this symbol).

无法载入,是为什么呢

你做的封封闭是真FLASH或都你填了假FLASH数字,但PCB板上是没有FLASH的模板,你现在的报错是说FLASH不匹配,应该是你的SIP2-4这个封装上的焊盘出了问题,你把封装打开,看下每个焊盘的FLASH是否有问题,

导网表时原理图不能有半点的差错,好好检查原理图吧~~~

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:如何批量修改元件封装

下一篇:关于VIA过孔的问题