- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

利用R/C滤波器实现DAC去干扰电路

在路上似乎到处都有令人讨厌的减速带,在行车道和停车场,随处可见它们的身影。尽管它们的尺寸大小不一,但都一样不讨人喜欢。碰到这些减速带时,您可以选择减速通过以减少对车辆的磨损,也可以退回去,但最好的办法是绕过去。

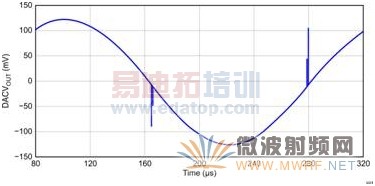

昨天,在我减速通过一条讨厌的减速带时,突然想到了我的那个精密型16 位R-2R DAC。它在中间刻度时存在短时脉冲波形干扰问题(请参见图1)。我想,在选择使用具有较大短时脉冲波形干扰特性的DAC 时,可以在DAC 输出端添加一些去干扰电路,从而减少干扰的影响。两种常见的DAC 去干扰电路是简单的低通滤波器(相当于一种减速方法),以及采样/保持电路(相当于"绕过"干扰)。这两种去干扰电路都可以降低干扰振幅,或者去除干扰能量。

图1 16 位DAC 产生的讨厌干扰

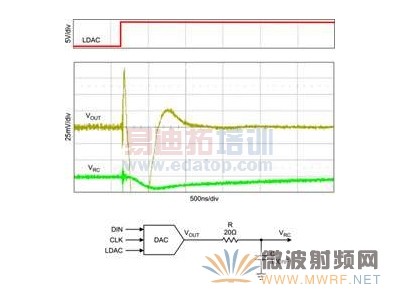

最简单的DAC 去干扰方法是在DAC 放大器输出端(VOUT) 使用一个R/C 滤波器(图2 底部)。这种滤波器可以降低干扰的振幅,但增加了建立时间。

图2顶部的曲线为DAC负载DAC(LDAC)引脚的信号。利用DIN(数据输入)引脚和CLK(时钟引脚),便能够以串行方式将一个数据字载入到DAC 中。一旦DAC 有了全部的数据,LDAC 引脚的升沿便将数据字载入内部DAC 寄存器。这样便改变了DAC 输出电压。中间的曲线表示测得的DAC 输出中间刻度模拟干扰。底部曲线表示使用一个R/C 低通滤波器后测得的模拟信号。

图2 R-2R DAC8881 (Vref = 5V, AVDD = 5V) 中间刻度转码

一般而言,这个过程会比较顺利。在您增加(或者减小)数据码值时,输出电压也随之上升(或者下降)。但在四分之一和四分之三中间刻度处,DAC 会产生干扰。中间刻度干扰最大。

要想确定正确的R/C 比,首先要查看干扰时间,然后给您的滤波器选择一个3dB点,其比干扰频率低10 倍左右。

例如,图2 中干扰时间约为1 μsec,经过转换得到1 MHz 干扰时间。由这种估算,我们知道图2 中的R/C 值构建了一个80 kHz 低通滤波器。在选择您的R/C 值时,请确定R 足够的低,以避免出现载入误差。

这种R/C 滤波器解决了R-2R DAC 干扰问题,但它也并非是一顿"免费的午餐"。正如您在图2底部曲线所看到的那样,R/C 滤波器延长了DAC 的建立时间输出信号。

根据您不同的应用要求,简单的R/C滤波器都可以奏效。如果系统要求一个有干扰问题的R-2R DAC,则开关电容解决方案结合R/C 滤波器可能会是一种解决方案。

参考文献

《把短时脉冲波形干扰这个小捣蛋鬼找出来》,作者:Baker,Bonnie

《一个DAC 便可完成所有精密工作》,作者:Baker,Bonnie

作者:Bonnie Baker,德州仪器(TI) 高级应用工程师

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:PIN射频开关与PIN限幅器基础知识

下一篇:宽带镜频抑制混频器设计及实现