- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

航天测控:系统级BIT设计及BIT验证技术

系统级BIT是监控系统关键功能、检测隔离系统级故障的主要手段和方法,也是可测试性设计的关键部分。而系统级BIT相对于板级BIT来说,信息分析工作更加繁杂,需要考虑的因素更加广泛,因此,单纯的采用一种技术和一种结构是远远不能达到要求的,必须采用多种关键技术相结合使用的方法来进行。

系统级BIT设计技术的主要内容是系统级BIT体系结构技术、智能BIT设计技术,以及降虚警技术。此外,BIT设计技术一个非常重要的环节-BIT验证环节也不容忽视。BIT验证就是在研制的产品中注入一定数量的故障,用BIT设计规定的测试方法进行故障检测与隔离,按其结果来估计产品的测试性水平,并判断是否达到了规定要求,决定接收或拒收。

一、系统级BIT体系结构

分散、独立式的常规BIT结构已经不能适用系统级BIT发展的需要了,因此大型复杂系统中的智能BIT越来越多的采用分布式、集中式和分布集成式的BIT结构。这即是BIT技术长期探索的结果,也是电子系统固有的层次化特点的要求,体现了系统开发的“并行设计”思想。

1、分布式BIT

分布式结构的BIT 是在每个分系统中都具有自己的微程序和微诊断,每个分系统的 微处理器 只为本系统负责,与其他系统没有任何关系,各自分系统的微 处理器 能够对本分系统的状态做出判断和决策最后通过系统故障 显示器 显示系统的状态。

2、集中式BIT

集中式BIT在每个分系统级均不设置自己的微程序和微诊断,整个系统的控制、诊断、和决策功能都依靠一个微处理器来实现,各个分系统只是将采集上来的信息通过数据总线上传到这个主微处理器。此微处理器通过分析接收到的数据信息,以及储存的历史信息,综合诊断整个系统的功能状态,对监测系统进行分析评价,并做出决策,同时将此状态信息输出到各显示装置并储存此状态信息。

3、分布集成式BIT(HIBIT)

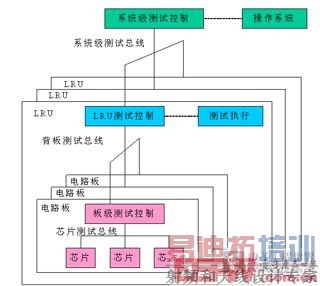

所谓HIBIT设计是指所设计的可测试性机制具有同系统一样的递阶层次结构,即具备包括系统级、子系统级、电路板级、多芯片模块级和芯片级的层次结构,不同层次的可测试性机制之间通过测试总线相连。实质上,HIBIT技术是边界扫描技术的一种延伸,在HIBIT中,板级测试利用IEEE 1149.1边界扫描标准进行,而设备级、系统级的测试则通过IEEE 1149.5 MTM总线进行。

递阶集成BIT

二、智能BIT技术

近20年来,智能BIT技术有了迅速发展.目前已出现了综合、信息增强、改进决策、维修历史、自适应和暂存监控等多种智能的BIT 技术。

上述六种智能BIT技术分别针对BIT问题的某个特定方面,运用ES(专家系统)、神经网络、有限态自动机等AI技术,试图从根本上改善常规BIT中由于故障诊断算法落后、不能利用人的经验和维修历史数据,不能识别设计时未考虑的新的失效模式等造成的虚警、CND和RTOK问题。在实际应用中,可以将它们以各种不同的方式综合起来,构成范围更广的BIT改进方法。比如,一方面,可以在单个分系统中采用信息增强BIT或改进决策BIT来改进BIT效能;另一方面,全部六种方法可以综合形成一个覆盖整个系统的智能BIT系统。

三、抗虚警技术

由于BIT诊断模糊性和诊断能力不足造成了BIT虚警率(FAR)高、不能隔离间歇故障等问题,严重降低了BIT诊断检测结果可信度,影响了使用和维修人员对BIT的信任。因此对BIT的虚警问题为重点进行分析和研究,提出一些解决BIT虚警问题的方法和措施,也是目前一个研究重点和热点。

1、BIT虚警产生原因

导致BIT虚警主要原因可归纳为以下几个方面:BIT设计上的缺陷、门限值(或测试容差)选择不当、故障诊断算法不合适、BIT工作可靠性不高。

2、BIT虚警控制

针对BIT上述各种产生虚警原因,进行BIT虚警控制、降低BIT虚警率时,可在BIT的各个阶段采取多种方法来实现。

从BIT设计方案中减少虚警 在报警前经过多次判断或延时报警,以滤除掉瞬间影响;为了减少容差查生的虚警,必须进行合理的可靠性容差设计。利用BIT检测冗余技术对检测结构进行故障表决,以减小虚警率;最后还要制订完善的测试验证计划。BIT设计是否满足要求,必须经过各种测试和验证等。

进行完善的数字 仿真 工作 要降低BIT的虚警问题,必须建立完善的系统性能模型,进行故障模式影响分析,以便及时发现设计中的不可靠环节,并采取一定的方法进行故障的消除和隔离。

从硬件上降低BIT虚警问题 通常规定BIT的可靠性比测试系统及设备的故障率要提高一个数量级,一种方法是构成BIT的元件的故障率比系统及设备所彩云的元件的故障率第一个数量级;另一种方法是规定系统中BIT的元件数不多于整个系统电气元件总数的10%;此外BIT系统自诊断、系统重构级冗余BIT都可提高BIT自身可靠性。另一方面,采取各种 滤波 措施,进行抗干扰设计。随着光纤技术的发展,可以采用光纤数据总线,进一步提高系统的可靠性,降低虚警;此外还可提高元器件的可靠性,采用高精度的测试器件,提高装配质量,完善生产工艺,进行抵抗恶劣环境应力的设计等。 [p]

软件中融入智能化BIT诊断 常规的BIT诊断算法是以瞬时的输入信号作为故障与否的判断依据,而且不考虑被测对象的动态历史数据,而瞬时值又不足以说明系统的故障情况,因此,应采取更为有效的智能化故障诊断算法等算法来减小这种错误判断,更好的识别系统中的间歇性故障。智能BIT技术是当前BIT领域内研究的重点,美国已经把该技术列入21世纪的重点发展项目之中。智能BIT技术的研究内容包括智能设计、智能检测、智能诊断和智能决策。智能化的BIT不仅仅依靠内部测试信息进行决策,而是结合了专家系统、神经网络等人工智能技术,综合系统所处的环境因素、BIT的历史数据等信息进行综合分析和诊断,增强了BIT决策能力,大大降低了虚警产生的概率。

四、故障注入技术

故障注入技术是BIT验证研究的重要方面,是验证工作得以实现的基础。故障注入就是将系统的有效故障模式样本注入到系统的实物中,以此评价系统的测试性设计水平。通过故障注入可以早暴露、早发现系统测试性设计的不足,进而采取有效措施,提高测试诊断能力。

基于原型的故障注入方法通常按照故障注入的实现方法再进一步划分,可分为硬件实现、软件实现、物理实现的故障注入技术。

硬件故障注入技术主要是适用额外的硬件设备向目标系统注入故障。附加硬件设备与目标系统之间通过探头、芯片插座等相连。由于对目标原型访问点的限制,目前对硬件实现的故障注入研究大多集中在芯片管脚级。

软件故障注入技术是通过特定的程序对系统软件、硬件错误状态进行 仿真 。这种方法容易扩展新的故障类型。故障注入原来就是通过修改程序执行语句,增加、修改、删除数据或直接修改寄存器或存储器的内容来 模拟 硬件或软件故障的发生。

一般来说,故障注入的过程可分为四个步骤:选择故障模型、进行故障注入、监控系统行为、分析故障结果。其中选择故障模型和分析故障结果是与用户交互的过程,是在用户的控制下进行,而进行故障注入和监控系统行为是用户选择好故障模型进行故障注入后系统自动进行的,是与目标系统的直接接口。

航天测控 公司目前已经对系统级BIT的各项关键技术进行了深入研究,并将这些技术转化到了多个项目的设计和研制过程中。同时,开发构建了一套系统级BIT的辅助设计工具,通过该平台可以对被测系统进行一系列的可测试性分析,根据分析结果给出进行BIT设计的多项工作建议,并能在设计完成后通过故障注入的方式来检验BIT设计的有效性。航天测控公司在系统级BIT设计的研究成果以及开发的软件平台能够规范系统级的BIT设计工作并极大的提高BIT设计的效率。

上一篇:基于虚拟仪器的家庭

下一篇:基于INTERNET的远程数据采集测量