- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于过零点检测的高分辨率DAC静态测试方法研究

摘要:受到现有测试设备的限制,高精度的D/A转换器(数模转换器)测试一直是混合信号测试中的难点,本文探讨了高精度数模转换器(DA C)测试的一种新方法。该方法通过在微弱被测电平上叠加参考正弦波,测试叠加后波形的过零点在时域上的分布情况,以了解DAC的静态特性参数。该方法的优点在于充分利用了现有ADC(模数转换器)的速度优势,原理简单,且易于实现。

关键词:数模转换器;积分非线性;差分非线性;过零点

0 引言

随着科技的日益发展,DAC转换精度越来越高,为了测试高精度DAC的性能,需要辅以分辨率更高的数字化ADC。然而,高精度的显示设备在一般实验条件下很难获得。因此,如何利用低分辨率的ADC有效评估高精度的DAC,成为测试行业亟待解决的问题。一些文献中提出过采样技术、抖动技术等方法,探讨减小ADC的量化误差来提高ADC的分辨率进而测试高精度DAC,但是这些方法都存在着一定的局限性。比如,当微弱信号的幅值低于最小ADC步长即LSB时,过采样技术无效;采用抖动技术也需要外加模拟电路,增加了测试成本和复杂程度。

D.L.Carni等在文献中提出了一个切实可行的方案,采用一个“纯”的正弦波作为参考信号,将其与待测DAC的输出电平叠加,通过分析结果信号在时域上的过零点分布情况,得出静态参数DNL(差分非线性)、INL(积分非线性)的值。这个方法从一定程度上解决了低精度测试高精度的问题,但是不足之处在于该方法的时间成本较高,对于很高精度的DAC,测试耗费的时间可能很长。

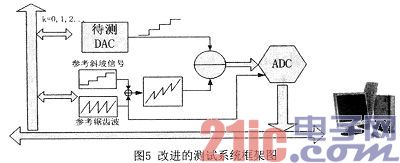

本文在过零检测的基础上提出了一种改进的测试方法,得到n位DAC的静态参数INL、DNL值。这种方法通过改进参考信号来比较DAC的输出和参考信号的输出,不但使低精度ADC可以有效测试高精度DAC,更重要的是缩短了测试时间,降低了测试成本。

1 基于过零检测的DAC静态测试

1.1 低精度ADC不能直接用来测试高精度DAC的原因

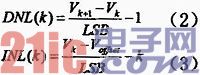

对于DAC的静态测试,通常测试DNL、INL这两个参数值,方法是输入代码k,k=0,1,2…2n-1。得到DAC输出的电平值Vk。计算DNL、INL的公式如下:

![]()

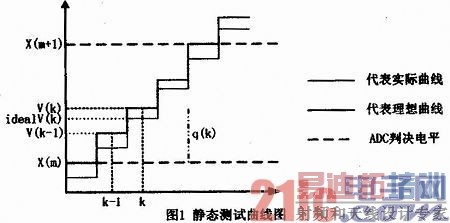

假如用精度低于DAC的ADC对其直接测试,如图1所示,由于低精度ADC引入的量化误差q(k),我们无法分辨输入代码k和k-1对应的确切电压值。这种情况下的静态参数测试就失去了意义。

1.2 过零检测

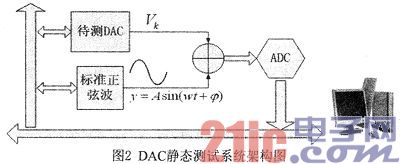

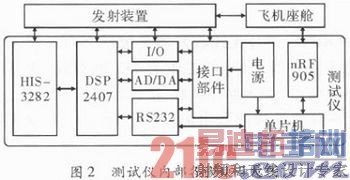

过零点检测法是一种经典的调制域分析方法,它通过记录过零点的时间得到过零点的时间间隔,可以用于识别精度低于ADC步长的微弱信号。图2简要地描述了测试系统框图:待测DAC输出的电压Vk,校准仪提供一个标准的参考正弦波f(t)=Asin(ωt+φ),将直流电压Vk加在参考正弦波上,将结果信号输入高速ADC。即:

![]()

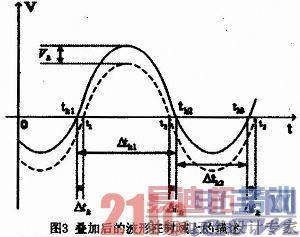

式(4)在时域图上的表现如图3所示。

图中,虚线表示标准参考信号f(t)=Asin(ωt+φ),实线为叠加之后的信号,可以看出,tk1、tk2、tk3时刻为过零点,Vk的大小由△tk决定。△tk的值可以通过测量过零点tk1、tk2、tk3得到,Vk的表达式可以推导如下:

![]()

其中,Nc为在时间间隔△tk内的采样点数,fs为设置的ADC的采样率。

1.3 测试方法的弊端

利用以上方法,可以得到DAC输出电压的值Vk,进而求出静态参数DNL、INL的大小。需要关注的是:为了得到过零点序列,参考正弦波的幅值A必须大于DAC的满量程电压范围;同样由式(5)得到ADC的最低采样率:

△V幅值分辨率,通过式(6)可以看出:为了确保测试的准确性,△V应该尽可能地小,并且在其他条件不变的情况下Nc的值越大越好。因为这种方法的本质在于将幅度上的高精度测试转移到时间上来。因此采样率越高,测量结果越准确,但是采样率与测试设备息息相关,不可能无限制提高。这种情况下,如果没有设备能够提供足够高的采样率,那么只能降低信号频率f。但是降低信号频率f将带来另一个问题,就是测试时间的成倍增加。

在文献中作者曾对16位且幅值为±10V的DAC进行了实测,采用泰克TDS7404B数字示波器作为采集信号用的ADC。其主要参数为:8位分辨率、20GS/s的最高采样率。设置△V=LSB/40,Nc=5,正弦波频率f=100Hz,幅值A=11V。通过式(6)得到的采样率高达5GS/s。每次测10个Vk对其做平均,这样每测一个Vk花费的时间是0.1s,即便拥有这样的超高采样率的设备,完整地测一个16位的DAC所需要的时间也至少需要两个小时。

2 提出的方法

从降低测试时间的角度考虑:首先,从图3中可以看到,利用正弦波作为参考波形至少需要3个过零点才能得到DAC的输出电压值,其次,为了降低检测每个过零点所需要的时间,最直接的方法就是提高参考信号的频率f,但是由于设备条件的限制,采样率fs不能再提高。从式(6)中可以看出,Nc、△V都是约定值,不可变动,唯一能改变的就是参考正弦波幅值A,但A的最小值也受到限制,因为一旦A小于被测DAC的量程范围,DAC中大于A的输出电压将无法测得。实际上,A的限制是因为我们需要测试每一个代码对应的输出电压值。

但事实上,我们并不需要测试每一个Vk。对静态测试而言,主要是了解被测DAC的线性度,如图4所示。影响DNL的主要是相邻两个输入代码的输出电平幅值之差与理想步长之间的偏差,即Vk+1-Vk与LSB之差。将DNL、INL的计算公式适当变化如下:

由图4和式(7)、(9)可以看出,只要知道输入代码的实际电压与理想电压的差值,一样能计算出DAC的静态参数。

基于以上认识,设计了如下的测试系统架构模型。

设参考锯齿波的信号f(x)*δT(x),其中:

参考斜坡的信号可以表示为:![]() ,[]为取整函数。

,[]为取整函数。

令DUT产生的信号为g'(x),经过叠加的均匀抖动上升的锯齿信号为f(x)*δT(x)+g(x),ADC采集的信号就是f(x)*δT(x)+g(x)-g'(x)。显然,g(x)-g'(x)的值代表了△Vk的大小,而△Vk很小,低精度的ADC是无法将其反映出来的。通过借助参考锯齿波形在时域上的过零点分布却能够表达出来。

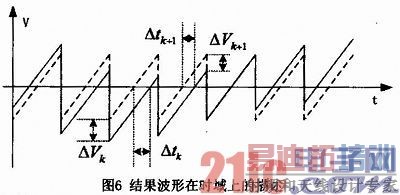

如果被测DAC表现出完美的静态特性,那么ADC会恢复出参考锯齿波信号,如果一旦被测DAC的输出电压Vk与理想值存在偏差(如图4),则会在时域图上明显地反映出来,如图6所示。

图中△Vk代表了在输入代码为k时,实际测量电平与这一点的理想电平的差值,虚线代表参考锯齿波信号,实线表示被测DAC与参考信号的差分信号。用一个双通道的ADC同时对两种信号进行采集,通过检测过零点,得到△tk、△tk+1的值,不难看出:

![]()

N代表锯齿波一个周期内的采样点,A表示锯齿波的幅值,然后有:

![]()

结果证明,在上述方法中,知道锯齿波的幅值以及△tk内的采样点数Nc,便可得到△tk的值,在这种方法中,并不需要知道每一个Vk的值,也可以轻松地获得DNL和INL的值。

3 仿真实验

为了验证此方法的可靠性,本文采用Labview虚拟仪器进行仿真测试。仿真中采用8位DAC产生标准的斜坡波形和锯齿波形,将两种信号的加法形式作为参考波形,设置随机白噪声点逐点加到标准斜坡波形上,使得LSB的范围限制为,以便用程序计算出实际仿真的DNL和INL的大小。程序的最终目的在于,将提出方法测试所得的结果和真实计算结果的偏差做一个比较。

通过编写测试程序,可以得到以下规律:

(1)ADC的采样率越高,实际测试得到的DNL和INL会更加接近真实的计算结果;

(2)参考锯齿波的幅值越小,测试的结果会越精确;

(3)ADC位数与测试精度几乎没有关系。

需要注意的是,增加采样点数会使测试时间增加,因此ADC的采样率不可以无限制提高,但是可以根据测试的实际情况对其作最佳评估。关于幅值的设定,其最低值必须使得每个差分锯齿波都有过零点。然后设置程序来比较标准锯齿波的过零点和差分锯齿波的过零点数,当两者不同时,程序中的指示灯报警。

在仿真测试中,设置DAC范围为10V,幅值为80mV;产生的斜坡中,每个输入代码重复100次,设置采样率为1k,采集256000个点。设置ADC的分辨率为2位。得到结果如图6所示。

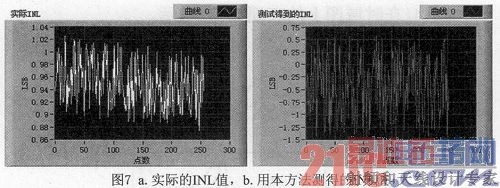

通过比较图6中两个波形的过零点之间的采样数,比较最终得到的INL值与计算所得INL值:图7 a.实际的INL值,b.用本方法测得的INL值。

4 结束语

本文对高精度DAC的动态测试提出了新的评估方法,这个方法通过比较参考锯齿波与实际得到的锯齿波在时域上的过零点,精确地获得了DAC的静态参数INT、DNL的值。并且在Labview仿真测试系统中进行了验证,结果证明了此方法的有效性和实用性。

上一篇:基于PCI总线的数据采集卡的设计与实现

下一篇:油田计量数据采集及监控系统设计