- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

如何应对GaN测量挑战

功耗是当今电子设计以及测试中最热门也是竞争最激烈的领域之一。这是因为人们对高能效有强烈需求,希望能充分利用电池能量,帮助消减能源帐单,或者支持空间敏感或热量敏感型应用。

在经过30年的发展之后,硅MOSFET发展已经接近其理论极限。硅技术的进步如今非常缓慢,很少量的进步都需要付出巨大的开发成本。而像碳化硅(SiC)和氮化镓(GaN)等替代性半导体材料正在逐渐成为首选材料。特别是GaN在许多领域都得到了人们的青睐,因为它能将硅片用作基板,从而带来与硅MOSFET相当接近的价格。由于GaN还处于生命周期的早期阶段,因此在未来几年内人们将见证到它显著的改进。

这些新材料不仅通过更快的开关速度还通过降低导通电压(Rds On)来提高效率。当然,任何一种新技术带来的不仅是独特的设计挑战,还有测试与测量方面的挑战。从测试角度看,这些材料所需的测试设备不仅要有更高的带宽,还要有更高的灵敏度。使用现成的电压探针并期望很小的信号失真和加载的日子已经成为过去。本文将简要介绍GaN,然后重点讨论测试方面的挑战。

功耗突破

据IMS Research公司最新报告预测,2021年GaN功率半导体市场将从2011年的几乎为零增长到超过10亿美元。这家市场研究公司分析了这些产品的所有关键终端市场,最后发现电源、太阳能逆变器和工业电机驱动将是三个主要的增长点。

上述报告指出,在过去两年中GaN晶体管开发不断在提速。国际整流器公司(IR)的“GaNpowIR”和宜普公司(EPC)的“eGaN FET”器件的发布开启了2010年的低压市场。而Transphorm公司的600V GaN晶体管则带来了GaN与高压MOSFET和IGBT竞争的可能性。

预测GaN飞速增长的一个关键理由是新工艺能够充分利用现有的生产基础设施。这些制造工艺将GaN半导体成本从约10倍于传统硅降低到了一个极具竞争力的水平,特别是对于要求提升性能的应用来说。其基本方法是在带有氮化铝缓冲层的硅基板顶部生长GaN。

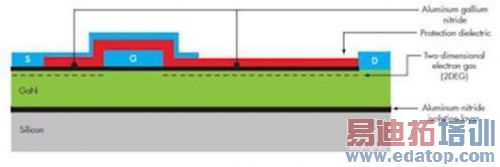

举例来说,宜普工艺开始于并不昂贵的硅晶圆。首先在硅片上生长一薄层的氮化铝(AIN),用于隔离器件结构与基板。对于200V及200V以下器件来说隔离层是300V的。在此基础上再生长一层厚的阻性GaN层。这样就为构建GaN晶体管提供了基础。接着要在GaN层上涂覆电子发生材料。这一层将创建一个具有丰富自由电子的量子应力场。进一步处理将在栅极底部形成一个耗尽区。为了增强晶体管性能,使用与导通N沟道增强型功率MOSFET相同的方式在栅极上施加一个正电压,如图1所示。这种结构再被重复许多次就能形成一个实际的功率器件了。最终结果是一个适合功率开关的、极具成本效益的优秀解决方案。

图1:宜普GaN可以利用现有生产基础设施实现极高的成本效益。

在应用方面,IMS报告预测GaN首先会在电源领域取得较大吸引力,因为其总体系统成本的节省超过了器件的单位价格上升。这些应用包括PC和笔记本电源适配器、服务器等,而诸如室内空调等国内电器设备、微型光伏逆变器、电动汽车电池充电和其它新应用有可能在不久的将来也会用上GaN功率器件。

凭借其较宽的带隙,GaN器件对高温应用来说非常有吸引力。比如,汽车制造商就对在混合动力汽车中的电源转换部分使用GaN器件非常感兴趣。过去,发动机设计师都是在这些应用中使用硅功率MOSFET,但由于温度方面的考量一般都要使电子器件远离于发动机模块。理想情况下,功率半导体应该邻近发动机,以便缩短走线、减轻重量并降低压降损失。GaN器件据报道可以承受高达300℃的温度,在此温度下仍能高效工作。

在信息处理和存储系统,整个电源架构可以重新评估,以便充分发挥GaN材料的突出开关性能优势。当交直流转换器的输出电压上升时,效率将随之提高。当总线电压增加时,传输效率随之提高。当频率提高时,产品体积将变小。据宜普公司称,GaN用作同步整流器时可以使能最后一级,再由最后一级使能前两级,同时提高交直流转换效率。GaN还能允许删除中间级转换器,实现单级转换,从而省却中间级转换器的体积和成本。

GaN测试挑战

与硅器件相比,GaN更加接近理想功率开关的特性,即阻塞无限幅度电压、承载无限大电流、瞬时开关以及要求零驱动功耗。当然,GaN也无法达到完美境界,但比硅要更加接近完美。总之,GaN可以提供更高的阻塞电压、更低的导通电阻和更快的速度。

通过比较测试表明,GaN FET通道能以纳秒速度开关,甚至在承载高达10A电流、开关频率约为80MHz的时候。GaN开关的缺点是电流峰值更快,压降相应也更快。不仅GaN器件开关速度更快,而且其导通阈值在漏极至源极电阻不变的情况下也更低。

为了充分发挥新材料的优势,需要使用示波器来表征GaN器件的行为,并测量开关过程中的损耗。当电压摆幅为600V或更高时,GaN器件要求快速仪器才能跟得上。示波器需要具有足够的带宽来跟踪开关过程,还需要具有足够高的分辨率来捕获低电压时的开关过程。

探针是限制因素之一。目前最好的高压差分探针提供约200MHz的带宽,测量信号电压高至1.5kV。一些单端高压探针可以提供800MHz的带宽,因此可以用来测量600V摆幅的信号。展望未来,可能需要kV测量范围和GHz以上带宽的探针,这样的探针目前还没有。

使用高压探针的另外一个挑战是确保探针之间有足够的绝缘和间隙,并且不影响测量性能。举例来说,长引线可能导致来自电路加载和振铃的感应现象,从而使得判断问题真正根源变得困难。测试设备制造商正在使用多种技术提高保真度,比如增加探针的阻尼电阻。

更高分辨率

高带宽和高电压通常是互相排斥的,因此为了测量600V的源极-漏极电压以及毫伏级的栅极电压,需要使用高分辨率的示波器。绝大多数示波器都是采用8位分辨率的ADC,但通过使用平均和高分辨率模式分辨率可以得到显著提高。

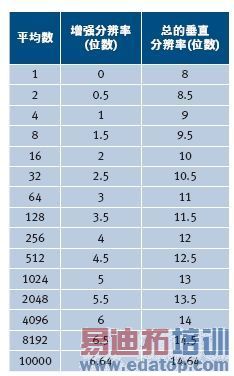

对于具有自然重复特性的信号来说,平均法提供了大幅度提高信号垂直分辨率的有效途径。这种以位数为测量单位的性能增强是总平均数的一个函数:

增强分辨率=0.5 log2(N)

其中:N代表要求的总的平均数

在许多示波器中,平均算法是用定点数学方法实现的。这意味着最大平均数是10,000,因此将总的分辨率位数限制在了理想的最大值14.64,见表1。这种平均方法可以保持完整的信号模拟带宽。

表1:通过平均法得到的示波器垂直增强分辨率。

虽然对许多应用来说平均是一种很有用的技术,但这种方法不适合单次采集。此时的解决方案是使用积分平均技术计算和显示在每次采样间隔中所有连续采样值的平均值。这种模式为过采样有关波形的额外信息提供了一种折衷方法。在这种情况下,额外的水平采样信息被代之以更高的垂直分辨率以及带宽与噪声的减少。

带宽限制和使用这种平均技术得到的垂直分辨率提高幅度与仪器的最大采样率和当前所选采样率有关。表2显示了使用最大采样率为10GS/s的示波器能带来的性能提升。垂直分辨率的位数增加量为0.5 log2*(D)(其中:D是抽取比率,或最大采样率/实际采样率),

最终的-3dB带宽(除非受测量系统的模拟带宽进一步限制)是:0.44*SR(其中:SR代表实际采样率)。

表2:使用积分平均方法实现的垂直增强分辨率。

本文小结

随着对提高功效要求的持续推进,具有30年发展历史的硅MOSFET已经达到了实用性能极限。现在业界专家已经预见到替代产品的快速增长,最著名的要数GaN了,因为在硅基板上生长GaN的新制造工艺可以使用标准化的低成本CMOS工艺,这为GaN功率器件打开了一个广阔的新型商业与工业应用大门。

由于具有高带宽和高电压的有效组合,GaN在测试与测量前沿面临艰巨的挑战,特别是在示波器的高电压探针和高分辨率方面。目前可用的2.5kV和800MHz探针足够600V器件使用,而平均技术还可以用来提升分辨率。在GaN这个重要领域,与GaN有关的产品和技术必将得到持续发展和改进。

上一篇:鼎阳科技示波表SHS800与SHS1000的区别

下一篇:检测仪器智能电池设计方案