- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于DMA的大批量数据快速传输模块设计

DMA控制器作为SOPC设计中使用频率较高的IP核,可用于存储器或外设间进行批量数据传输,以提高系统数据吞吐量。然而,由于DMA控制器只支持对基于Avalon总线流传输模式的外设进行数据传输操作,对用户自定义外设不予支持。文中提出了一种基于Avalon总线流传输模式的通用DMA接口控制器设计,实现了NiosⅡ与FPGA的大批量数据快速传输,显著提高了系统的数据吞吐量。

1 Avalon—MM总线规范

Avalon总线规范是为开发SOPC环境下外设而设计的,为SOPC设计者描述这些外设的端口提供了基础。Avalon总线有多种传输模式,其中,流传输模式为从端口提供了一种机制,用于控制来自主端口的传输,流传输模式的这些特点使其特别适合于DMA传输。

流模式从端口传输模式的信号,除了在从端口传输中使用的信号之外,又引入了3个信号:readyfordata、dataavailable和endofpack et。其中,从端口通过设置Readyfordata有效来表示它已经准备好接收来自Avalon总线模块的写传输,使readyfordata无效表示写操作将引起数据上溢,从端口通过设置dataavailable有效来表示它已经能够为来自Avalon总线模块的读传输提供数据,dataavailable无效时读操作将引起数据下溢,在任何传输期间,流模式从端口都可以设置endofpacket信号有效,并通过Avalon总线模式传输给主端口。对于endofpack et信号的解释取决于用户设计,必须明确外设如何响应endofpacket信号的变化。

2 系统结构

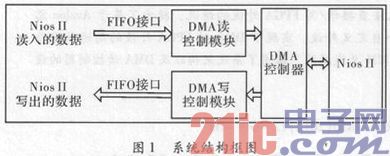

提出的NiosⅡ与外设进行大批量数据传输的结构如图1所示,当NiosⅡ需要从外设读入数据时,外设通过FIFO接口将数据写入DMA读控制模块,然后数据经DMA传输至NiosⅡ,反之,当NiosⅡ输出数据时,数据通过DMA传输至DMA写控制模块,FPGA逻辑通过FIFO接口从这个模块读取数据。DMA读/写控制模块的设计,是为了解决SOPC中DMA模块与FPGA片上FIFO不同接口间的数据传输问题,而在SOPC中,DMA模块使用的是支持流传输模式的Avalon—MM总线。DMA读/写控制模块主要完成两个功能:一是FIFO与DMA主端口之间的数据交互,二是作为一个NiosⅡ的外设,NiosⅡ处理器能够对此外设进行控制并能随时获取该外设的状态信息。

3 DMA读/写控制模块的设计

DMA读/写控制模块作为系统结构的核心,其结构框图如图2所示。此模块包括两个Avalon—MM从端口:一个作为DMA从端口,用于处理DMA对此模块的数据读操作,另一个Avalon—MM从端口是NiosⅡ的控制从端口,用于NiosⅡ处理器对这个模块进行控制并且随时获取此模块的状态信息。模块还包括一个中断请求信号(IRQ),当外设有数据需要读取时,可以使这个信号有效,从而通知NiosⅡ发起DMA读传输。另外,DMA读控制模块中还例化了一片FPGA片上FIFO作为数据上传FIFO,用于系统待上传数据的暂存。使用FIFO可以提高数据传输的吞吐量,同时简化FPGA硬件逻辑的操作,图2中的管道(Conduit)端口就是FPGA硬件逻辑操作FIFO的接口。

对于与NiosⅡ处理器交互的Avalon—MM从端口,从NiosⅡ处理器的角度看,这个端口是一些寄存器的映射,即NiosⅡ对该模块的操作,是通过对模块内部的寄存器的操作完成的。根据功能需隶,DMA读控制模块中设计了3个寄存器,即状态寄存器status,控制字寄存器control和FIFO中已有数据个数寄存器usedw。

DMA读控制模块的中断请求应当在两种情况下产生:一是此模块的数据源端将FIFO写满且外设中断使能有效,二是此模块的数据源端置数据包结束标志且外设中断使能有效。

对于DMA从端口,使用的是带流控制信号的Avalon总线,DMA使用流控制信号中的dataavailable以及endofpacket两个总线信号。其中dataavailable表示外设是否准备好读操作,即FIFO是否非空,对于endofpacket信号,设计中使用这个信号来表示模块中数据包的结束,endofpacket信号与最后一个数据同时出现并持续1个时钟周期,DMA检测到endofpacket信号有效后将停止DMA传输。对于管道端口,这是最新的Avalon总线规范定义的接口形式,主要用于外设和外部逻辑进行交互。

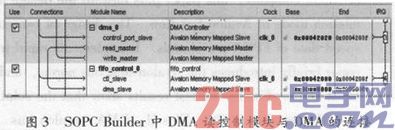

DMA读控制模块作为一个用户自定义外设,在将其添加到SOPC Builder外设库后,就可以在SOPCBuilder中调用此外设,图3表示了SOPC Builder中该外设与DMA的连接,图中fifo_control_0即为DMA读控制模块,可以看出,这个外设包含了两个Avalon—MM端口,其中一个连接至DMA控制器模块dma_0,而且SOPC Builder为这个外设分配了基地址和中断优先级。

4 测试验证

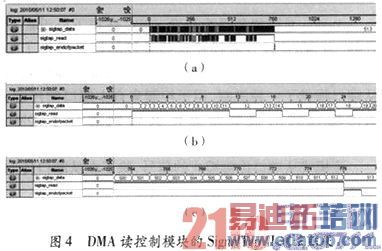

DMA读控制模块测试时,FPGA内部产生数据源并通过外设管道接口把数据写入FIFO,外设中断时,DMA读取外设中的数据。测试时使用QuartusⅡ自带的SignalTapⅡ嵌入式逻辑分析仪进行测试,观察相应信号的波形。本测试的触发条件为signaltap_read上升沿触发,FIFO深度为1 024,FIFO数据宽度为16位,数据源为2~513共512个计数值,在Nios II的软件中读取600个数据,测试结果如图4所示。

图4对应3幅图像,图4(a)表示DMA读取外设的测试数据的全局视图,后面两幅为局部放大结果,其中图4(b)是测试数据的开始段,图4(c)是测试数据的结束段。如图4(b)所示,在第一个时钟周期,DMA的读信号有效,在之后的第二个时钟周期,FIFO的数据总线出现数据2,之后是3,4,…,从图4(c)可以看出,最后一个数据是513,且DMA读取外设512个数据,只花费了约776个时钟周期,这充分显示了DMA高速的数据传输能力。

对于调试模式下Nios II IDE的输出结果,如图5所示。由于测试数据太长,这里只给出测试数据的首部及尾部。图5(a)为测试数据的首部,使用printf()函数输出,第一个数据为2,接着是2,3,…,从图5(b)可看出最后一个有效数据是513,从512起的数据为0,这是数组的初始值,这与图4相对应。

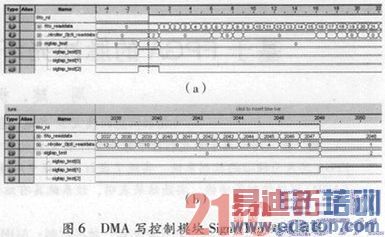

DMA写控制模块测试时,置FIFO数据宽度为16,NiosⅡ控制端口数据总线宽度为16,FIFO深度为2 048,在NiosⅡ软件中设置一个长度为2 048的数组,数组数据宽度为16位,初始化时把数据赋值为1~2 048的计数值,然后发起DMA写传输,把数据写入到DMA写控制模块中,在FPGA再用硬件语言读此外设中FIFO数据并在SignalTapⅡ中显示,其测试结果如图6所示。

图6中,fifo_rd表示FPGA中硬件逻辑读取DMA写控制模块的读信号,fifo_readdata是外设中FIFO的数据总线信号,sigtap_test信号连接至外设中FIFO满、FIFO空以及waitrequest信号(LSB),图6(a)表示了外部逻辑读取外设中FIFO的数据起始段,在读信号有效之前,sigtap_ test[2]信号是高电平,表示FIFO满,sigtap_test[0]为高,表示外设此刻不能响应DMA写入的数据,然后FPGA外部逻辑在检测到FIFO满后开始读取数据,在下一个时钟周期,FIFO数据总线上出现有效数据。图6(b)是读取FIFO时数据的结束段,最后一个数据为2 048,读取后,sig tap_test[1]为高电平,表示数据读空,这与NiesⅡ中软件写入DMA从而写入DMA写控制模块的数据是一致的,由此验证了模块设计的正确性。

5 结束语

设计方案稳定可靠、传输速度高,具有一定的通用性,能满足NiosⅡ与外设之间的大批量数据传输,具有广泛的应用前景,同时,使用了FIFO作为缓存,进一步提高了数据吞吐量,具有较强的实用价值。