- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速数字设计及仿真概述

高速数字总线标准近年来层出不穷,数据速率不断提升,基于NRZ编码的10Gbps~25Gbps高速数字串行接口已经实现商用,25Gbps~56Gbps速率等级各主流芯片厂商已经逐步推出demo性质评估平台,在各大设计展会上时有报道。

本文对高速数字设计及仿真方法做一概述性介绍,技术不断发展更新,文中如有不对之处,还望共同探讨。

1. 高速数字设计及仿真总体流程

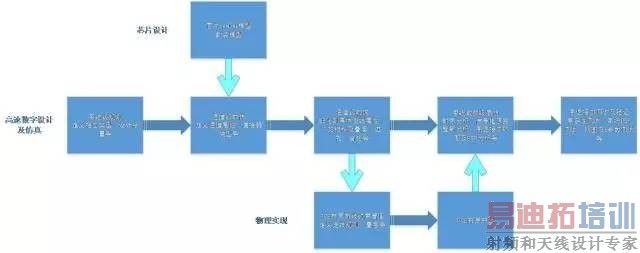

如图1所示,它从总体流程上描述如何进行高速数字设计及仿真,包括前期系统级规划、通道级前仿、系统或板级后仿、高速接口测试及验证、PCB布局布线物理实现等。接下来的章节将围绕各具体步骤进行详细论述。

图1 高速数字设计及仿真总体流程

2. 系统级规划

这个阶段最为关键,设计人员和系统工程师需要相互配合将产品需求映射到具体的产品设计中。根据产品需求将关键芯片选定后就可以设计产品硬件总体框图,根据框图我们可以将高速数字链路部分单独筛选出来,大体上可以分为两类,一类为板外的高速接口,比如到外部SFP模块、外设接口USB、HDMI、SATA等,另一类为板内芯片间的高速接口,比如XFI、SRIO、10GE等。针对每一类高速接口,我们需要在这个阶段指定接口最高工作速率、链路的插损等物理参数裕量(这些参数来自对应接口的标准文档)、收集关键芯片的IBIS-AMI模型。同时可以根据以往的项目经验,大体指定PCB层叠、PCB材料等息息相关的设计约束条件。这个阶段的输出将为下一个阶段通道前仿提供必要的条件。接下来介绍通道前仿。

3. 通道前仿

这个阶段是对系统级规划阶段要求的初步确认,具体分析需要设计人员和仿真工程师紧密配合。根据前面提供的约束条件,我们会为每一类高速接口构造具体的通道,同时需要详细的定义通道走线的属性(比如线宽、线间距、过孔数量、是否进行背钻处理等)、PCB板的层叠结构(每层用到的PCB材料属性Dk/Df等、PCB板厂的工艺能力参数等)、芯片封装及中间连接器的模型(大部分厂商都会提供此类模型)、芯片IBIS-AMI模型。仿真工程师可以根据这些确定下来的条件进行前仿工作,主要的变量是走线的线长、PCB板材等。走线线长的计算要根据各种标准提供的插损上限值进行推断,这个阶段最为关键一点是PCB板材Dk和Df要尽量精确,不能直接使用PCB材料厂商提供的数据,如果有条件的话自己做一些类似层叠的PCB样板进行实测,方法有SPP、SET2DIL等,再不济可以使用PCB板厂实测的数据(问题是他们实测的数据是根据他们设计的样板做的,与我们实际设计的PCB板存在一些差异)。得到最差情况下PCB走线长度后,我们也可以启动PCB预布局布线活动,在PCB工具中我们很容易得到这段走线的实际长度,这样我们可以将这个长度与仿真得到的长度进行比较,如果这个长度比仿真得到的要长,这个时候说明设计不满足要求,我们需要对设计进行调整(具体操作是将芯片进行重新布局以减小走线长度)或者选用拥有更小Df值的PCB板材(这种做法会带来产品成本上升)又或者在通道上加上一级中继器等芯片(这种情况也会增加成本,一般在长度超出比较多时考虑使用)。这个阶段的输出将为PCB布局和布线提供详细的约束条件,PCB工程师将根据这些约束对高速通道进行具体走线实现。

4. 系统级或板级后仿

这个阶段的仿真更加接近实际产品情况。我们会根据情况使用不同精度的仿真工具对实际走线、过孔等进行模型提取,三维仿真工具比如ADS、CST、Hyperlynx等提取精度高,但是带来负面效应是仿真时间特别长,有时候还会出现仿真设置不合理时仿真不收敛,为此具体应用时必须考虑这些因素,对某些通道中的结构比如过孔等我们会使用三维电磁仿真工具,对通道中的走线采用二维电磁仿真工具,这种折中在保证一定仿真精度的前提下大幅提高了仿真效率,不至于使项目进度拖延。后仿形态上有时候需要做几块PCB的级联形成一个系统,他们之间通过连接器或线缆进行连接,这种系统级的仿真可以大幅降低设计风险,尤其是产品中如果出现多种不同的模块组合,我们只要仿真一种最坏情况就可以保证其他组合也能正常工作。后仿采用的设置需要根据后期测试得到的数据做一些优化和微调,保证仿真和测试之间的偏差尽量小。具体仿真时我们首先会将无源通道的S参数文件提取出来,利用这个文件我们可以做一些标准兼容性分析,比如10GBase-KR等标准中就定义了各种参数指标如插损、回损、串扰等。这个分析可能会出现一些通不过的项,之后我们就需要结合芯片进行有源仿真分析,其中眼图和BER分析是其中两个重要的指标。眼图我们直接观查片上CDR之后的表现,这可以使我们定性的知道某个通道的性能表现。最直接的指标当属BER分析,它结合了发送器、通道、接收器,对其进行系统级仿真,并可以外延推导不同发送比特数(一般标准要求是10e12,有些标准要求是10e15)下的逐级表现,如果没有出现误码,我们可以判定设计从仿真角度来看是满足要求的。

5. 高速数字接口测试及验证

当前面所有设计及仿真阶段都结束后,我们已经心中有底,只待原型机回来开始此阶段的测试及验证。测试分为无源测试和有源测试,其中无源测试主要使用网络分析仪、TDR等设备对通道的物理性能参数比如插损、阻抗、回损、串扰等进行测试,有源测试包含PRBS、BER、发送幅度裕量测试等。无源测试可以给我们提供很多关于通道本身的信息,比如阻抗控制是否在要求范围内,插损是否满足标准要求,实测与通道仿真间的差距。有源测试的最终目的是得到一组最优的芯片SerDes参数,这组参数可以保证产品在不同工作环境下不会出现误码,同时具有一定的裕量从而保证不同批次产品都可以正常工作。

6. 结论

本文从大的流程角度对高速数字设计及仿真进行了阐述,具体实施时每家公司可以根据自己的实际项目情况进行不同安排,总之一句话,高速数字设计及仿真在硬件产品设计中成为最为关键的环节之一,不合理的设计将给产品上市带来严重的后果,为此我们要将高速数字设计及仿真普及到每个硬件产品的研发过程中。

Agilent ADS 教学培训课程套装,专家讲解,视频教学,助您用最短的时间学会ADS

上一篇:如何在ADS中使用Angelov GaN模型

下一篇:高速高频电路电磁场仿真:FDTD和FEM算法各有什么优缺点

国内最全面、最专业的Agilent ADS培训课程,可以帮助您从零开始,全面系统学习ADS设计应用【More..】

国内最全面、最专业的Agilent ADS培训课程,可以帮助您从零开始,全面系统学习ADS设计应用【More..】

- Agilent ADS教学培训课程套装

- 两周学会ADS2011、ADS2013视频教程

- ADS2012、ADS2013射频电路设计详解

- ADS高低阻抗线微带滤波器设计培训教程

- ADS混频器仿真分析实例视频培训课程

- ADS Momentum电磁仿真设计视频课程

- ADS射频电路与通信系统设计高级培训

- ADS Layout和电磁仿真设计培训视频

- ADS Workspace and Simulators Training Course

- ADS Circuit Simulation Training Course

- ADS Layout and EM Simulation Training Course

- Agilent ADS 内部原版培训教材合集