- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

布线工程师如何充分掌控时钟信号?

在数字电路设计中,时钟信号是一种在高态与低态之间振荡的信号,决定着电路的性能。在应用中,逻辑可能在上升沿、下降沿触发,或同时在上升沿和下降 沿触发。由于溢出给定时钟域的案例极多,故有必要插入缓冲器树来充足地驱动逻辑。时钟树通常带有布线工程师必须满足的延迟、歪曲率、最小功率及信号完整性 要求。

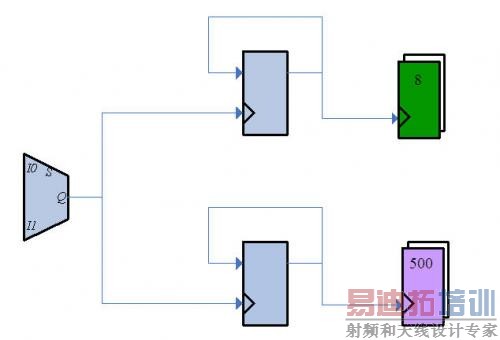

当电路从前工序设计人员转移到后工序布线工程师时,可以认为时钟概述与图表是必须沟通的最关键信息。多年以来,由于沟通失误,数以小时、天甚至是星期计的设计工作沦为白费,需要包括时钟树在内的全套重新合成。 在布线之前,采用极佳的时钟来用于合成及时序约束。约束的时钟定义可能出现在模块的顶层焊盘或引脚;可能出现在宏的输出,如锁延迟环(DLL) 或锁相环(PLL);或者作为产生的时钟出现在除法寄存器上。这些时钟定义可能是也可能不是布线工程师需要定义时钟树根以在不同工作模式之间获得最优延迟 及平衡歪曲率的领域。前工序及布线工程师之间围绕这些信息的高级别信息沟通以及理解布线工程师怎样运用这些信息,将大幅优化物理设计流程的CTS过程。 有效CTS的设计技巧 下面的某些技巧在业界已经使用多年,但基于过去几年的经验,仍然值得重复运用。 为时钟树根使用中到大强度的驱动器。这就使时钟树能有恰当的起点。但不要使用库中最大的驱动强度,如果信号完整性(SI)分析或片上变化(VOC)分析未出现问题,能够在随后的设计中用到。 如果时钟除法寄存器及其同步寄存器要在单独测试模式中工作,确保它们被复用逻辑有针对性地驱动。这就能够在测试模式下在输入端增加延迟,而不会影响此功能模式下所产生的时钟驱动的其他所有寄存器。 (divide-by)寄存器不会与任何下行寄存器平衡。绿色域的寄存器数量越少,越会使时钟速度比紫色域中的时钟速度快得多。 图1 寄存器时钟除法寄存器 图2显示了可能使每簇下行寄存器及除法寄存器能够通过复用的一种输入拥有极小时钟及通过复用的另一路输入拥有平衡时钟的复用机制。

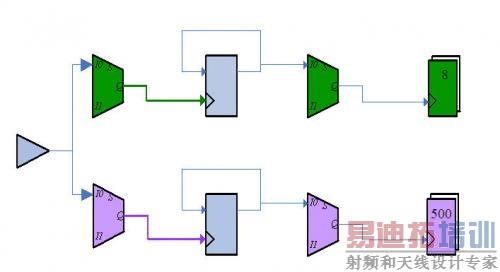

图1 寄存器时钟除法寄存器 图2显示了可能使每簇下行寄存器及除法寄存器能够通过复用的一种输入拥有极小时钟及通过复用的另一路输入拥有平衡时钟的复用机制。  图2 下行寄存器及除法寄存器复用机制 若有需要,则插入专用复位驱动器。某些情况下将使用几个寄存器来同步复位。那些寄存器可能并不需要由相同的寄存器来平衡。在图3中,由于未采用集中策略,软件将尝试平衡门控逻辑后的蓝色寄存器,而每个粉红色寄存器包含在复位同步逻辑中。

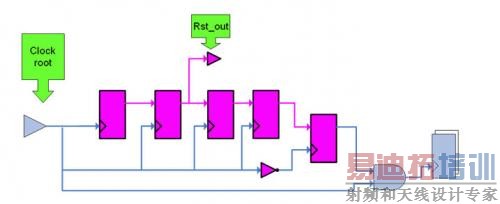

图2 下行寄存器及除法寄存器复用机制 若有需要,则插入专用复位驱动器。某些情况下将使用几个寄存器来同步复位。那些寄存器可能并不需要由相同的寄存器来平衡。在图3中,由于未采用集中策略,软件将尝试平衡门控逻辑后的蓝色寄存器,而每个粉红色寄存器包含在复位同步逻辑中。  图3 平衡门控逻辑后的寄存器 如果它们在各自专用驱动器中与其他寄存器分开了的话,在布线过程中这种情况就很容易处理。图4显示了可以怎样在设计交递(hand-off)沟通过程中插入及轻易识别占位符(place-holder)或排除缓冲器,使布线工程师知道哪里可能会出现平衡问题。

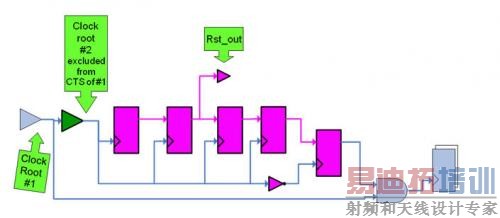

图3 平衡门控逻辑后的寄存器 如果它们在各自专用驱动器中与其他寄存器分开了的话,在布线过程中这种情况就很容易处理。图4显示了可以怎样在设计交递(hand-off)沟通过程中插入及轻易识别占位符(place-holder)或排除缓冲器,使布线工程师知道哪里可能会出现平衡问题。  图4 插入及轻易识别占位符或排除缓冲器 提供超出预期的时钟图表及大量时钟简介。当前工序设计准备好提供网表进行布线时,他们已经非常熟悉设计及时钟要求。某些情况下,初始CTS设计 会提示预布线时序约束中使用的理想值在实际物理设计中不能实现的情况。如果提供了精确的时钟图以及带有时钟原理相关信息的网表交递,就能够更快地弄清导致 此状况的问题。 总体图或是代表设计中所有时钟(含门控逻辑)的图非常有用。这要么是采用画图软件,要么是使用电路图捕获工具等使用软件产生的图,甚至还可以是手绘并存储为PDF文档或发送传真给布线工程师的图。此图抵得上尝试直接获得时钟格式的多次通话或电子邮件沟通过程中的千言万语。 由于图表可能会很复杂繁琐,就需要提供相应的简介文档,包括产生的时钟、任何时钟门控或复用图案的详情以及歪曲率平衡和延迟要求等方面的阐释。 每种工作模式都需要这些详细信息,因为在插入时钟树期间必须应对每种模式。寄存器可能最后会提供用于功能模式的平衡,但如果我们不仔细的话,测试模式下可 能极不平衡。 如果时钟使用DLL或其他宏或它通过门控逻辑,这些详细信息就在所必需了。如果有需要的话,有可能通过那些类型的宏来合成及平衡。对于门控逻辑 而言,如果存在一个引脚通过一种模式来连接、但同单元的其他引脚采用另一种模式来连接的情况,走线工具将把这种情况识别为"重汇聚时钟"。虽然布线工具可 以解决这些问题,但更好的解决办法可能是迫使工具在时间插入期间查看这个引脚而非其他引脚。 业界软件工具中的CTS 业界软件遵循设计人员的规格及指引,以强大的工具推动时钟树合成。源自前工序的跟时钟树根插入点、延迟、歪曲率及过渡目标相关的信息以及用于门 控逻辑、通过寄存器和跨域关系的详细信息能够直接移植到CTS工具中。然后布线工程师将自已判断要使用的缓冲器类型、优化迭代及间距、屏幕和金属层等布线 要求。 在插入时钟树之前,能够使用走线来确保存在旨在用于平衡的端点。还能够提示及评估门控逻辑、时钟树根排除的分支、IO端点以及重汇聚实例。 时钟树可能仅包含缓冲单元或是系列反相器。如今的大多数技术拥有特别的时钟缓冲及时钟反相单元,这些单元提供平衡的上升及下降时间,以帮助确保占空比不被损及。还可以整合其他要求,如时钟树中等级或各个时钟单元的最大扇出。 结论 除了上文探讨的所有因素,布线工程师很可能还会尝试有时钟门控意识的布局、时钟布线指引及平面布局调整。CTS替代通常在极少调整歪曲率、延迟 及过渡目标的情况下运行。试错法帮助提供极佳的协调。如果前工序理解CTS如何工作且在最开始就沟通时钟结构,那么布线工程师将能够更加得心应手地接手任 务。日程中原本计划用于CTS的时间就可以用于微调及改善"你的时钟",而非简单地尝试将其插入到"我的布线"。

图4 插入及轻易识别占位符或排除缓冲器 提供超出预期的时钟图表及大量时钟简介。当前工序设计准备好提供网表进行布线时,他们已经非常熟悉设计及时钟要求。某些情况下,初始CTS设计 会提示预布线时序约束中使用的理想值在实际物理设计中不能实现的情况。如果提供了精确的时钟图以及带有时钟原理相关信息的网表交递,就能够更快地弄清导致 此状况的问题。 总体图或是代表设计中所有时钟(含门控逻辑)的图非常有用。这要么是采用画图软件,要么是使用电路图捕获工具等使用软件产生的图,甚至还可以是手绘并存储为PDF文档或发送传真给布线工程师的图。此图抵得上尝试直接获得时钟格式的多次通话或电子邮件沟通过程中的千言万语。 由于图表可能会很复杂繁琐,就需要提供相应的简介文档,包括产生的时钟、任何时钟门控或复用图案的详情以及歪曲率平衡和延迟要求等方面的阐释。 每种工作模式都需要这些详细信息,因为在插入时钟树期间必须应对每种模式。寄存器可能最后会提供用于功能模式的平衡,但如果我们不仔细的话,测试模式下可 能极不平衡。 如果时钟使用DLL或其他宏或它通过门控逻辑,这些详细信息就在所必需了。如果有需要的话,有可能通过那些类型的宏来合成及平衡。对于门控逻辑 而言,如果存在一个引脚通过一种模式来连接、但同单元的其他引脚采用另一种模式来连接的情况,走线工具将把这种情况识别为"重汇聚时钟"。虽然布线工具可 以解决这些问题,但更好的解决办法可能是迫使工具在时间插入期间查看这个引脚而非其他引脚。 业界软件工具中的CTS 业界软件遵循设计人员的规格及指引,以强大的工具推动时钟树合成。源自前工序的跟时钟树根插入点、延迟、歪曲率及过渡目标相关的信息以及用于门 控逻辑、通过寄存器和跨域关系的详细信息能够直接移植到CTS工具中。然后布线工程师将自已判断要使用的缓冲器类型、优化迭代及间距、屏幕和金属层等布线 要求。 在插入时钟树之前,能够使用走线来确保存在旨在用于平衡的端点。还能够提示及评估门控逻辑、时钟树根排除的分支、IO端点以及重汇聚实例。 时钟树可能仅包含缓冲单元或是系列反相器。如今的大多数技术拥有特别的时钟缓冲及时钟反相单元,这些单元提供平衡的上升及下降时间,以帮助确保占空比不被损及。还可以整合其他要求,如时钟树中等级或各个时钟单元的最大扇出。 结论 除了上文探讨的所有因素,布线工程师很可能还会尝试有时钟门控意识的布局、时钟布线指引及平面布局调整。CTS替代通常在极少调整歪曲率、延迟 及过渡目标的情况下运行。试错法帮助提供极佳的协调。如果前工序理解CTS如何工作且在最开始就沟通时钟结构,那么布线工程师将能够更加得心应手地接手任 务。日程中原本计划用于CTS的时间就可以用于微调及改善"你的时钟",而非简单地尝试将其插入到"我的布线"。 ...........................................................

与非深度解读系列:

半导体公司"大学计划"的追问和真相

大环境的不景气是就业环境恶化的元凶,但是也让我们不禁追问半导体公司的大学计划对于学子们的真正意义。厂商们的大学计划都在做些什么?那么多的联合实验室有得到充分利用吗?大学计划的直接体验者--老师和学生们是否真正从中受益…….【专栏作者:高扬】

本土IC公司调查笔记

全球经济不景气的大环境下一些本土IC公司的创新能力、管理能力、抗风险能力、盈利能力,甚至公司创立的动机都受到一些质疑。一方面官方的消息总是告诉我们中国的半导体产业得到了长足的进步;而街巷小道中又不绝流传多少本土IC公司倒闭,多少公司靠欺骗,根本没有核心竞争力….真相只有一个,也许会随《本土IC公司调查笔记》慢慢开启…【专栏作者:岳浩】

电子屌丝的技术人生系列

在这个系列里,每个故事都会向你展示一个普通工程师的经历,他们的青葱岁月和技术年华,和我们每个人的的生活都有交集。对自己、对公司、对产业、对现在、对未来、对技术、对市场、对产品、对管理的看法,以及他们的经历或正在经历的事情,我们可以看到自己的影子,也看清未来的样子……【专栏作者:任亚运】

细说电子分销江湖的那些事

对于从事电子分销行业的同仁们来说这是一个最坏的年代,也是一个最好的年代,我们即面临国际分销巨头在管理、资金、货源等方面对我们造成的冲击,又迎来本土集成电路的崛起,个性化服务盛行的机遇,通过这个系列,我想以"第一现场"的经历带大家一起了解国内集成电路分销的那些年、那些事,以及哪些感慨…..【专栏作者:张立恒】

专栏作者申请

联系人:高扬

邮箱:gaoyang@eefocus.com

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:第一页

下一篇:PCB覆铜箔层压板的制作方法