- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用于倒装芯片设计的高效的重新布线层布线技术

工程师在倒装芯片设计中经常使用重新布线层(RDL)将I/O焊盘重新分配到凸点焊盘,整个过程不会改变I/O焊盘布局。然而,传统布线能力可能不足以处理大规模的设计,因为在这些设计中重新布线层可能非常拥挤,特别是在使用不是最优化的I/O凸点分配方法情况下。这种情况下即使采用人工布线,在一个层内也不可能完成所有布线。

随着对更多输入/输出(I/O)要求的提高,传统线绑定封装将不能有效支持上千的I/O。倒装芯片装配技术被广泛用于代替线绑定技术,因为它不仅能减小芯片面积,而且支持多得多的I/O。倒装芯片还能极大地减小电感,从而支持高速信号,并拥有更好的热传导性能。倒装芯片球栅阵列(FCBGA)也被越来越多地用于高I/O数量的芯片。

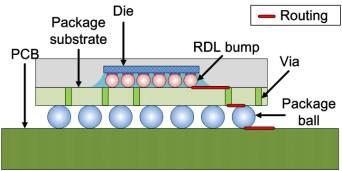

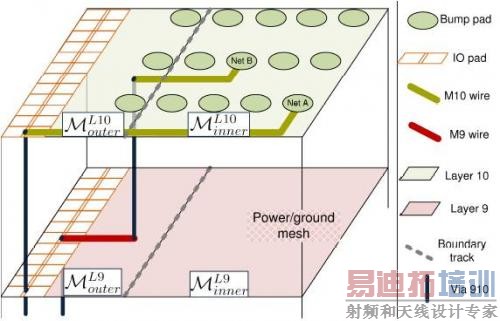

图1:倒装芯片横截面:信号线经过包括重新布线层在内的三个面。

重新布线层(RDL)是倒装芯片组件中芯片与封装之间的接口界面(图1)。重新布线层是一个额外的金属层,由核心金属顶部走线组成,用于将裸片的I/O焊盘向外绑定到诸如凸点焊盘等其它位置。凸点通常以栅格图案布置,每个凸点都浇铸有两个焊盘(一个在顶部,一个在底部),它们分别连接重新布线层和封装基板。因此重新布线层被用作连接I/O焊盘和凸点焊盘的层。

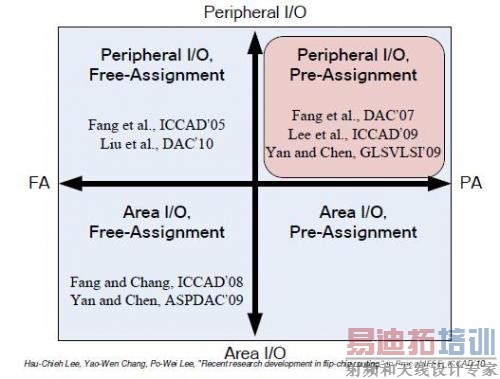

图2:自由分配(FA)和预分配(PA)是两种焊盘分配方法。外围I/O(PI/O)和区域I/O(AI/O)是两种倒装芯片结构。

倒装芯片结构与焊盘分配

以往研究已经明确了两种倒装芯片结构和两种焊盘分配方法,如图2所示。自由分配(FA)和预分配(PA)是两种焊盘分配方法,而外围I/O(PI/O)和区域I/O(AI/O)是两种倒装芯片结构。

两种焊盘分配方法的区别在于凸点焊盘和I/O焊盘之间的映射是否定义为输入。自由分配的问题是,每个I/O焊盘都可以自由分配到任意凸点焊盘,因此分配与布线需要一起考虑。而对预分配来说,每个I/O焊盘必须连接指定的凸点焊盘,因此需要解决复杂的交叉连接问题。预分配问题的解决比自动分配要难,但对设计师来说则更加方便。

两种倒装芯片结构分别代表不同的I/O布局图案。AI/O和PI/O的挑战分别在于将I/O放在中心区域和将I/O放在裸片外围。目前PI/O更加流行,因为它简单,设计成本低,虽然AI/O理论上可以提供更好的性能。

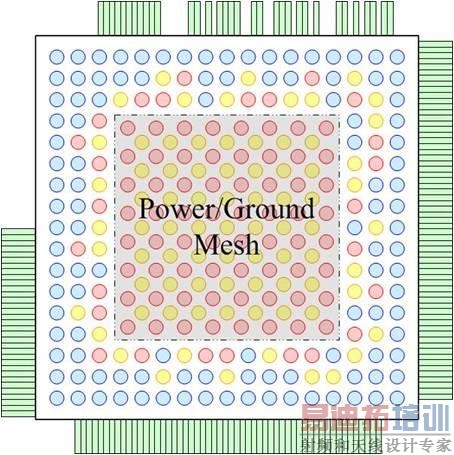

图3给出了一个PI/O例子。外围一圈绿色矩形代表I/O焊盘。红色和黄色圆圈代表电源和地凸点,而蓝色圆圈代表信号凸点。位于裸片中央的那些电源/地凸点被分类为网状类型,信号凸点被分类为栅格类型。

图3:重新布线层顶视图,图中显示了栅格图案的凸点焊盘和外围的I/O焊盘。

上述所有工作都集中在单层布线。它们将布线限制在一个金属层,每个网络都必须在这个层完成布线。一般的目标是尽可能地减少走线长度。优化算法需要在布通率为100%的前提下完成。这种方法被证明可以很好地解决每种重新布线层的布线问题,前提是存在单层解决方案。

实用的重新布线层布线方案

重新布线层布线和凸点分配都是额外的实现任务,它们有助于设计从线绑定过渡到倒装芯片。凸点分配的意思是将每个凸点分配到指定的I/O焊盘。由于对大多数设计来说I/O焊盘位于裸片外围,因此飞线和信号走线看起来像是从芯片中心到四周边界的网状图案。

图3显示的是一个使用两层重新布线层的真实比例设计例子。金属层10(M10)和金属层9(M9)完成所有信号网络布线,并分别实现电源/地(PG)网格和电源布线。通常有数量众多的信号网络需要布线。凸点焊盘的占用面积比较大,在布线阶段常被认为是影响布线的障碍。

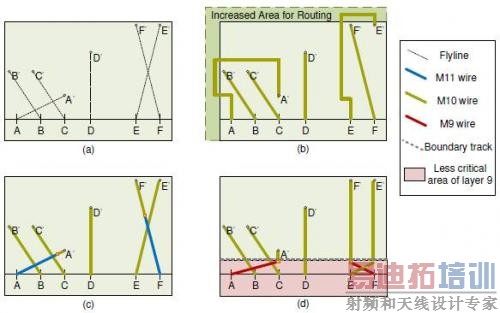

图4:拥挤的重新布线层的布线解决方案。

[p]图4(a)显示了一个拥挤的重新布线层例子,其中netA、netB……netF这6条网络显示为飞线。这种设计如此拥塞,以致于在单个层(如M10)上根本不可能达到100%的布通率。一种解决方案是增加重新布线层(如M10)的面积。这相当于增加裸片尺寸,如图4(b)所示。另外一种解决方案是再增加一层重新布线层(如M11),如图4(c)所示。虽然从工程角度看具有实际可操作性,但从成本角度看两种解决方案都是不可接受的。

替代性框架

一种更实用的选项是被称为伪单层布线的概念,它要占用已有金属层(如M9)上的一小块区域。如果所占用的区域用于非性能关键功能,这种方法就具有可操作性,并且极具成本效益。

在图4(d)中,M9的一些区域(粉色区域)被用来完成布线。这里我们假设边界线(打点的灰线)和裸片边界之间的区域用于辅助布线。伪单层布线方法规避了成本问题,而且降低了拥挤布线的难度。虽然前述工作集中于单层布线,但伪单层布线在小块区域内使用了两层布线。

这种方法适用于重新布线层,因为M9通常用于连接电源地和I/O焊盘,而且最重要的M9功能是将电源平均分配到内核中的每个逻辑门。结果M9外围区域的重要性就没有中心区域高,使得信号网络能够与电源地网络共享M9外围区域。

图5:分别位于第9层和第10层的第一和第二个重新布线层。电源地网放置在M_inner^L9。可布线的区域是M_outer^L10 ∪ M_inner^L10 ∪ M_outer^L9。

重新布线层布线的问题表现在连接凸点焊盘Bi和输入/输出焊盘Oi之间的网络Ni。第一和第二个重新布线层分别是M9和M10,见图5。我们根据边界线将这个区域命名为内部/外部区域。整个重新布线层被划分为4个区:M_inner^L9、M_outer^L9、M_inner^L10和M_outer^L10。

术语定义

● 可布线区(伪单层):M_outer^L10 ∪ M_inner^L10 ∪ M_outer^L9

● 外部区:M_outer^L10 ∪ M_outer^L9

● 内部区:M_inner^L9 ∪ M_inner^L10

伪单层重新布线层的布线问题是在可布线区内完成网络Ni的Bi和Oi的实际连线,并最大限度地减小内部区的面积。这也意味着边界线不是固定的。解决方案就是要确定边界线的位置。

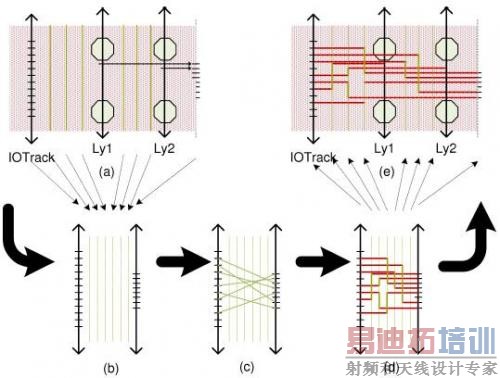

我们的伪单层布线算法共有4步:第一步是区域性层分配、可移动的引脚分配和版图抽取。第二步是完成从一个凸点焊盘到一个引脚的网络布线。第三步是确定使用哪根线。第四步是完成从I/O焊盘到引脚的布线。图6显示了完成可移动引脚分配流程的简单例子。第一步最重要。好的可移动引脚分配能最大限度地减少重新布线层走线。

图6:这个简单例子解释了布线流程:(a)区域性层分配,可移动引脚的分配以及版图抽取。步骤(b)和(d)描述了使用哪根线以及使用通道布线完成从I/O焊盘到引脚的布线。(e)展示了重新映射进原始版图的布线结果。

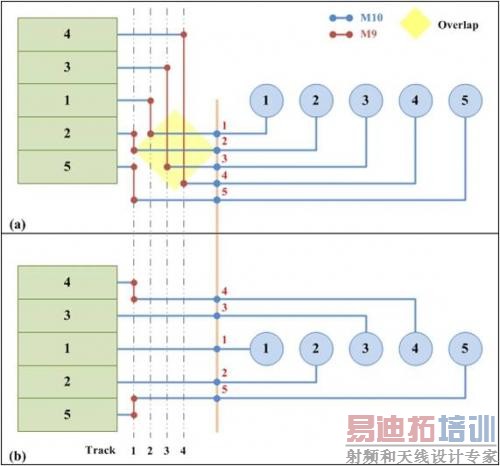

图7:可移动引脚分配的两个版本:(a)从单边排序的可移动引脚分配。(b)使用凸点引脚选择算法的可移动引脚分配。凸点引脚选择算法可以实现更少走线的布线结果。

图7显示了两种可移动引脚分配方法。第一个版本从同一边完成每排凸点的可移动引脚分配,因此引脚顺序和凸点顺序是相同的。这种方法可以快速完成可移动引脚分配,但缺点是顺序被凸点排固定了。如果凸点顺序不理想,就会产生大量的走线。

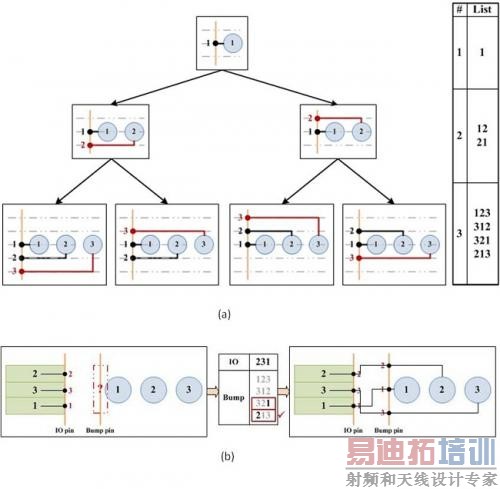

第二个也是推荐的方法是引脚选择算法,如图8所示。第一步产生所有可能的可移动引脚顺序,并在没有任何交叉网络的情况下完成从凸点到引脚的布线。第二步是按照最少交叉数量的原则从第一步选择可移动引脚顺序。凸点选择算法确保凸点到引脚连接没有任何交叉,引脚到焊盘的交叉数量最少。在使用凸点选择算法后,再由通道布线算法完成从引脚到I/O焊盘的布线,并确定走线数量,分配走线资源。最后将布线结果重新映射到原始版图,完成伪单层的重新布线层布线。

图8:凸点选择算法。(a)产生可移动的引脚顺序。(b)选择可尽量减少可移动引脚和I/O焊盘间交叉连接的引脚顺序。

验证有效性

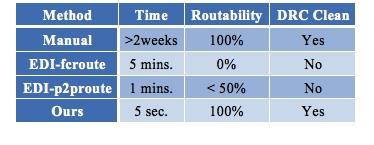

上述框架结构已经在一个大规模的商业项目中实现。首先,芯片被分为4个区:W、N、E和S。每个区包含100个以上的信号凸点。针对每个区,我们的布线器可以在不到5秒的时间内产生结果并完成命令脚本的下载。通过在Encounter Digital Implementation (EDI)中提交这些脚本就完成了物理布线。这个结果也可以用任何引脚至引脚布线器实现,因为所有引脚位置都分配好了。设计规则检查(DRC)判断所有结果都是好的。布线结果见图6和图7,同时总结在表I中,其中fcroute是在所定义的EDI中的倒装芯片布线器,p2proute是点到点布线器。由于没有签署披露协议,因此只显示了部分结果。

表I:布线结果小结。

本文小结

本文介绍了在伪单层上完成重新布线层布线的一种方法,这种方法可以用于太过拥塞以至于人工布线都无法实现单层解决方案的场合。伪单层布线方法提供了替代增加额外金属层或增加裸片尺寸的可行方法。成功的关键是区域性层分配、可移动的引脚分配和版图抽取。这些技术将重新布线层的布线问题转变成为典型的通道布线问题。利用这种方法可以做到百分之百的布通率,并且最大限度地减小了两层布线的面积。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:不可不知的几种真实设计环境中的系统设计

下一篇:saber仿真中的问题处理方法