- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

模拟/数模混合电路加速仿真技术

录入:edatop.com 点击:

如今,涉及模拟和数模混合电路的SoC设计日益增多。由于电路规模增大和复杂度提高,传统的SPICE仿真器已不能满足设计需求。而采用电路分割、多速率仿真、改进的器件模型等技术的Fast SPICE仿真器突破了传统SPICE工具的容量和速度限制。此文主要讨论目前复杂模拟和数模混合电路仿真面临的主要挑战,以及如何用新一代Fast SPICE仿真器加以解决。

对今天的混合信号SoC设计,往往包括模拟、射频、数字、定制数字和来自不同IP提供商的IP。为实现完整意义上的芯片级验证,需要采用SPICE、射频仿真器、混合信号仿真器和Fast SPICE等多重仿真器的组合。设计者在不同设计阶段往往需要采用来自不同公司的仿真器,而这些仿真器由于不同的环境支持和不同的语法格式存在兼容性问题,往往导致误差和不稳定性,并增加额外工作量和设计风险。

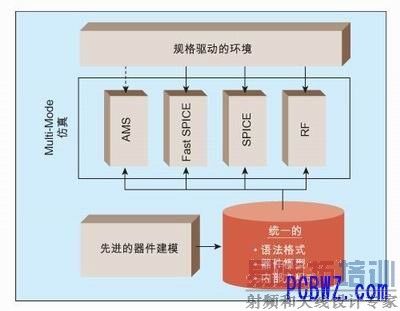

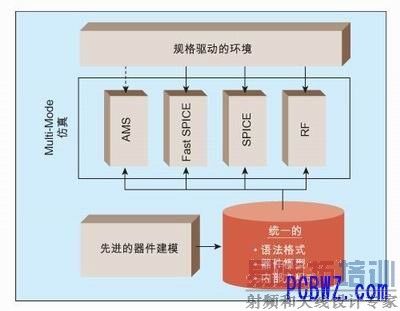

图1:Multi-Mode仿真(MMSIM)解决方案。

为降低用户在设计工具方面的使用难度和工具转换风险,Cadence推出Multi-Mode仿真(MMSIM)解决方案,通过使用统一的用户接口、器件模型、语法格式、内部方程式,极大地提高了数据兼容性和仿真结果可信度。Multi-Mode技术使设计者可在统一的设计环境中,在模拟、射频、混合信号、芯片级电路验证的不同设计阶段,自由切换Spectre、SpectreRF、AMS Designer和Ultrasim等仿真器,如图1所示。

本文将着重讨论如何应用分层的全芯片晶体管级验证工具—UltraSim,解决目前模拟/混合信号电路设计中面临的挑战。

模拟/混合信号电路仿真面临的挑战

随着工艺技术的发展和竞争的压力,主流芯片已经从10年前的0.5微米发展到今天的0.13微米乃至90纳米。先进的工艺可以让设计者把更多、更复杂的电路模块集成在同一硅片上,但同时也对电路仿真提出了新的挑战。目前模拟/混合信号电路仿真面临的挑战主要有以下几个方面。

1. 急剧增长的设计复杂度,对仿真器的容量和速度提出更高的要求;

2. 激烈的市场竞争和不断爬升的流片费用,使如何缩短设计周期、提高流片成功率成为芯片设计中的主要问题之一;

3. 深亚微米小尺寸效应的影响变得更为显著,如短/窄沟效应对阈值电压影响、亚阈值电流、体效应导致的衬底电流等;

4. 低信号摆幅设计中电路噪声和交叉耦合效应、低电源电压下信号线和电源网格的电压降和电迁移问题等;

5.

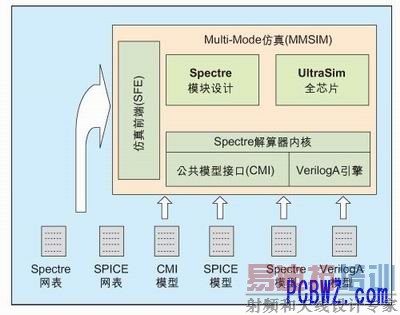

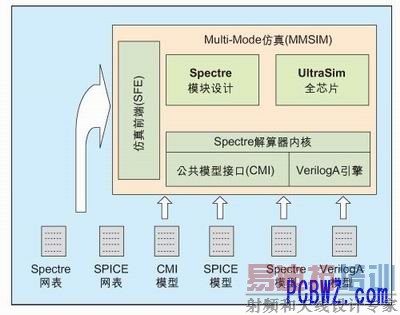

图2:MMSIM中的共享组件。

SoC芯片中电源调节器导致电路各模块间电源耦合增强。混合信号仿真由于数字模块和模拟模块分开仿真,不能反映此类问题;

6. 对互连线延迟、信号串扰、衬底效应、接地噪音(Ground bounce)等物理效应的考虑,依赖于精确的后仿真结果。

上述问题的解决越来越依赖于全芯片晶体管级电路仿真及后仿真,而传统晶体管级SPICE仿真器由于容量和速度的限制,通常只适用于模块级电路设计,因此Fast SPICE技术的引入不可避免。

Fast SPICE技术介绍

为了克服第一代SPICE仿真工具(如Spectre、PSPICE)在仿真容量(约50K)和速度上的缺陷,第二代SPICE技术即Fast SPICE仿真器采用电路分块、多速率、简化模型等加速仿真技术。

传统SPICE仿真器将电路作为一个矩阵,随着电路规模的增加,矩阵的求解速度显著下降。Fast SPICE把相关的电路模块放在一起,将大矩阵分成许多小矩阵,减小计算量。此外,事件驱动技术可忽略不活动的电路,进一步降低运算量。

电路分块的另一个优点是可采用多速率仿真。各个电路模块往往存在不同的工作频率,因此仿真中不同的电路块可以采用不同的仿真步长。这样,既可以保证高频率的电路得到精确结果,又让低频率的模块避免重复计算,降低CPU负荷。

简化模型技术是Fast SPICE加速的另一项重要技术。在传统电路仿真中,MOSFET或BJT需要一组复杂的公式进行计算,常常耗费大量的CPU时间。而Fast SPICE在仿真开始时先产生模型表格,然后进行查表,从而节省大量的时间。Fast SPICE通过多层次简化的模型,可以满足不同的精度和速度要求。

使用UltraSim进行模拟/数模混合电路仿真

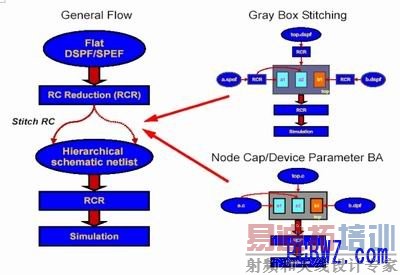

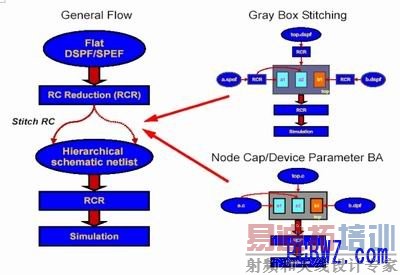

图3:布局后仿真流程和RC缝合技术。

Virtuoso UltraSim Simulator作为新一代Fast SPICE仿真器,引入了分层化同型仿真、动态电路分割等技术,对电路中的相同子模块只需计算其中一个,避免重复计算,从而进一步提升仿真容量和速度;提供与传统SPICE的完全兼容以及和SPICE类似的仿真精度;简洁的选项使设计者可以方便地定制电路仿真;改进的RC减小技术使之可以进行精确、快速的后仿真。此外,UltraSim已完全集成于Cadence标准模拟设计流程之中。这些优点使UltraSim成为目前业内应用最广泛的Fast SPICE工具之一。

1. 精确模型支持

硅精确的器件模型从来都是得到准确的电路仿真和物理效应分析的关键。通过与业内公认的先进器件模型提取工具BSIMPro+共享所有的模型和公式,UltraSim不仅拥有强大的器件模型支持能力,而且还可确保获得硅精确的仿真结果。

2. 本征兼容性

Cadence MMSIM中的各种仿真器(包含Spectre、SpectreRF、AMS Designer和UltraSim)都通过CMI读入器件模型,并使用相同的VerilogA引擎,消除了因为仿真器不兼容带来的不准确性和不稳定性(如图2所示)。此外,作为混合信号仿真器,UltraSim支持Spectre、结构化Verilog和多种SPICE网表;支持所有标准模型和描述特定电路的模型单元(如闪存宏模型)、行为描述语言VerilogA和SpectreHDL;支持VCD/EVCD/VEC;支持传统SPICE的后处理方式(如.measure,多种波形文件格式等)。

3. 强大的后仿真能力

因为引入大量寄生电阻电容(RC),后仿真更富有挑战性。UltraSim采用专用的RC减小技术可有效减小RC数目(可达90%),且将精度损失控制在1%~3%以内。与传统的RC减少技术相比,UltraSim专利算法在保证精度的同时能更显著地减小仿真时间和内存消耗。UltraSim采用的RC减小技术并不是简单过滤小电容或小电阻,而是用简化的等效RC网络代替原来复杂的RC网络,并可根据信号频率自动调整RC的简化程度。

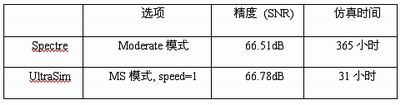

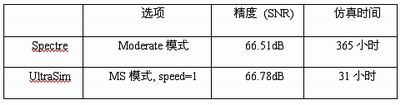

表1:Spectre和UltraSim的∑-Δ ADC仿真结果对比。

UltraSim支持所有标准的后版图网表格式,如SPICE网表、Extracted View、扁平或分层化的DSPF或SPEF网表、DPF以及节点电容网表等;并支持目前业内多种后仿真流程。此外,UltraSim的RC缝合技术可以选择性地把寄生RC加到指定的电路模块上(如图3),使设计者可以灵活地定制其电路仿真流程,例如对某些数字模块采用行为级模型,某些重要的模拟模块采用带寄生参数的网表。UltraSim提供postl选项设置RC减小的简化程度,它可以自动调整所有相关RC压缩参数。有经验的设计者也可以根据需要自由调整各个参数。

4. 仿真易用性

模拟/数模混合电路的仿真精度取决于模型精度和仿真器容差。设计者在使用UltraSim时,一般只需设置仿真模式和速度来优化仿真,到达良好的精度和速度匹配。当然,有经验的设计者可以依据对其设计本身和Fast SPICE技术的了解来调整各个选项,进一步提高仿真性能。

UltraSim已完全集成于Cadence标准的全定制设计流程中。用户可以在ADE中方便地切换Spectre、UltraSim和AMS Designer等不同的仿真器,完成从模块级电路到全芯片的仿真与调试。在ADE界面下,设计者可以根据需要产生Spectre或标准SPICE网表,并以图形化方式快速设置仿真模式和速度等选项,获得良好的精度和速度匹配。此外,ADE也为UltraSim的时序、功耗、可靠性分析提供友好界面。

5. 电源网络分析、设计检查及其它

对于包含电源网络的电路,电阻网络的存在会降低仿真速度。为此,UltraSim推出了UPS方案,通过把电源电阻网络和其它电路分离,由UPS和UltraSim协同仿真。因此,在得到3-5倍加速仿真的同时,仍能得到精确的IR压降分析报告。

为了发现和修改设计中的错误,UltraSim提供多种设计检查功能,包括过载电流检查、电压越界检查、高阻结点检查、DC漏电流路径检查等。Ultrasim的时序分析工具可以帮助设计者来检测转换时间、建立时间、保持时间或者脉冲宽度上的错误,而功耗分析工具可以报告指定时间、指定子电路端口上的电流和功耗。

对于高频电路,Ultrasim提供了Fast Envelope仿真等。

仿真实例

下面部分通过两个典型实例说明如何用UltraSim仿真模拟/数模混合电路。

1. ∑-Δ ADC

相对于Nyquist采样ADC,过采样ADC包含的模拟器件数目较少,但由于过采样率很高,往往需要较长的瞬态仿真时间。本实例为某∑-ΔADC的后仿真。该电路内部最高时钟频率为450MHz,包含1个VerilogA模块、瞬态分析时间为20us,FFT分析采样点4,751。表1为Spectre和UltraSim的仿真结果对比。

表2 :RC减小前后器件统计。

这里仿真选项设为sim_mode=MS(模拟/数模混合电路的全局模式一般采用默认的MS模式)、speed=1(定义仿真器的容差,相当于Spectre的Moderate模式)。

为保证仿真精度,后仿真使用了默认值(postl=1),即较保守的RC减小技术。从表2中可以看到,RC减小后,电容的数量从60.7K减小到1.3K,其中耦合电容数仅为529。由于采用层次化和同构技术,juncap的数量从27K减小到2.11K。最终,UltraSim获得11倍的速度提高。

2. RF PLL

本实例为一用于无线通讯的PLL,其前仿真网表包含31K MOSFET、600BJT、75K二极管和大约1.5K R/C。参考时钟频率为33MHz,LC型VCO频率为3.9GHz。UltraSim参考设置为:

.usim_opt sim_mode=ms speed=5 analog=3

.usim_opt speed=4 method=gear2 IPLL.VCO

.usim_opt sim_mode=df IPLL.LOGIC

这里,我们采用了MS仿真模式,其中analog=3使UltraSim在电路划分时考虑更大的反馈回路以保证精度;speed=4, method=gear2局部地加于VCO模块(通常RF VCO需要使用gear或trap收敛算法以及更小的容差)。数字模块采用了df模式,即用简化的数字表格模型来进一步提高速度。UltraSim仅用了19小时就完成25us瞬态仿真,甚至超过设计者的期望值。

对今天的混合信号SoC设计,往往包括模拟、射频、数字、定制数字和来自不同IP提供商的IP。为实现完整意义上的芯片级验证,需要采用SPICE、射频仿真器、混合信号仿真器和Fast SPICE等多重仿真器的组合。设计者在不同设计阶段往往需要采用来自不同公司的仿真器,而这些仿真器由于不同的环境支持和不同的语法格式存在兼容性问题,往往导致误差和不稳定性,并增加额外工作量和设计风险。

图1:Multi-Mode仿真(MMSIM)解决方案。

为降低用户在设计工具方面的使用难度和工具转换风险,Cadence推出Multi-Mode仿真(MMSIM)解决方案,通过使用统一的用户接口、器件模型、语法格式、内部方程式,极大地提高了数据兼容性和仿真结果可信度。Multi-Mode技术使设计者可在统一的设计环境中,在模拟、射频、混合信号、芯片级电路验证的不同设计阶段,自由切换Spectre、SpectreRF、AMS Designer和Ultrasim等仿真器,如图1所示。

本文将着重讨论如何应用分层的全芯片晶体管级验证工具—UltraSim,解决目前模拟/混合信号电路设计中面临的挑战。

模拟/混合信号电路仿真面临的挑战

随着工艺技术的发展和竞争的压力,主流芯片已经从10年前的0.5微米发展到今天的0.13微米乃至90纳米。先进的工艺可以让设计者把更多、更复杂的电路模块集成在同一硅片上,但同时也对电路仿真提出了新的挑战。目前模拟/混合信号电路仿真面临的挑战主要有以下几个方面。

1. 急剧增长的设计复杂度,对仿真器的容量和速度提出更高的要求;

2. 激烈的市场竞争和不断爬升的流片费用,使如何缩短设计周期、提高流片成功率成为芯片设计中的主要问题之一;

3. 深亚微米小尺寸效应的影响变得更为显著,如短/窄沟效应对阈值电压影响、亚阈值电流、体效应导致的衬底电流等;

4. 低信号摆幅设计中电路噪声和交叉耦合效应、低电源电压下信号线和电源网格的电压降和电迁移问题等;

5.

图2:MMSIM中的共享组件。

SoC芯片中电源调节器导致电路各模块间电源耦合增强。混合信号仿真由于数字模块和模拟模块分开仿真,不能反映此类问题;

6. 对互连线延迟、信号串扰、衬底效应、接地噪音(Ground bounce)等物理效应的考虑,依赖于精确的后仿真结果。

上述问题的解决越来越依赖于全芯片晶体管级电路仿真及后仿真,而传统晶体管级SPICE仿真器由于容量和速度的限制,通常只适用于模块级电路设计,因此Fast SPICE技术的引入不可避免。

Fast SPICE技术介绍

为了克服第一代SPICE仿真工具(如Spectre、PSPICE)在仿真容量(约50K)和速度上的缺陷,第二代SPICE技术即Fast SPICE仿真器采用电路分块、多速率、简化模型等加速仿真技术。

传统SPICE仿真器将电路作为一个矩阵,随着电路规模的增加,矩阵的求解速度显著下降。Fast SPICE把相关的电路模块放在一起,将大矩阵分成许多小矩阵,减小计算量。此外,事件驱动技术可忽略不活动的电路,进一步降低运算量。

电路分块的另一个优点是可采用多速率仿真。各个电路模块往往存在不同的工作频率,因此仿真中不同的电路块可以采用不同的仿真步长。这样,既可以保证高频率的电路得到精确结果,又让低频率的模块避免重复计算,降低CPU负荷。

简化模型技术是Fast SPICE加速的另一项重要技术。在传统电路仿真中,MOSFET或BJT需要一组复杂的公式进行计算,常常耗费大量的CPU时间。而Fast SPICE在仿真开始时先产生模型表格,然后进行查表,从而节省大量的时间。Fast SPICE通过多层次简化的模型,可以满足不同的精度和速度要求。

使用UltraSim进行模拟/数模混合电路仿真

图3:布局后仿真流程和RC缝合技术。

Virtuoso UltraSim Simulator作为新一代Fast SPICE仿真器,引入了分层化同型仿真、动态电路分割等技术,对电路中的相同子模块只需计算其中一个,避免重复计算,从而进一步提升仿真容量和速度;提供与传统SPICE的完全兼容以及和SPICE类似的仿真精度;简洁的选项使设计者可以方便地定制电路仿真;改进的RC减小技术使之可以进行精确、快速的后仿真。此外,UltraSim已完全集成于Cadence标准模拟设计流程之中。这些优点使UltraSim成为目前业内应用最广泛的Fast SPICE工具之一。

1. 精确模型支持

硅精确的器件模型从来都是得到准确的电路仿真和物理效应分析的关键。通过与业内公认的先进器件模型提取工具BSIMPro+共享所有的模型和公式,UltraSim不仅拥有强大的器件模型支持能力,而且还可确保获得硅精确的仿真结果。

2. 本征兼容性

Cadence MMSIM中的各种仿真器(包含Spectre、SpectreRF、AMS Designer和UltraSim)都通过CMI读入器件模型,并使用相同的VerilogA引擎,消除了因为仿真器不兼容带来的不准确性和不稳定性(如图2所示)。此外,作为混合信号仿真器,UltraSim支持Spectre、结构化Verilog和多种SPICE网表;支持所有标准模型和描述特定电路的模型单元(如闪存宏模型)、行为描述语言VerilogA和SpectreHDL;支持VCD/EVCD/VEC;支持传统SPICE的后处理方式(如.measure,多种波形文件格式等)。

3. 强大的后仿真能力

因为引入大量寄生电阻电容(RC),后仿真更富有挑战性。UltraSim采用专用的RC减小技术可有效减小RC数目(可达90%),且将精度损失控制在1%~3%以内。与传统的RC减少技术相比,UltraSim专利算法在保证精度的同时能更显著地减小仿真时间和内存消耗。UltraSim采用的RC减小技术并不是简单过滤小电容或小电阻,而是用简化的等效RC网络代替原来复杂的RC网络,并可根据信号频率自动调整RC的简化程度。

表1:Spectre和UltraSim的∑-Δ ADC仿真结果对比。

UltraSim支持所有标准的后版图网表格式,如SPICE网表、Extracted View、扁平或分层化的DSPF或SPEF网表、DPF以及节点电容网表等;并支持目前业内多种后仿真流程。此外,UltraSim的RC缝合技术可以选择性地把寄生RC加到指定的电路模块上(如图3),使设计者可以灵活地定制其电路仿真流程,例如对某些数字模块采用行为级模型,某些重要的模拟模块采用带寄生参数的网表。UltraSim提供postl选项设置RC减小的简化程度,它可以自动调整所有相关RC压缩参数。有经验的设计者也可以根据需要自由调整各个参数。

4. 仿真易用性

模拟/数模混合电路的仿真精度取决于模型精度和仿真器容差。设计者在使用UltraSim时,一般只需设置仿真模式和速度来优化仿真,到达良好的精度和速度匹配。当然,有经验的设计者可以依据对其设计本身和Fast SPICE技术的了解来调整各个选项,进一步提高仿真性能。

UltraSim已完全集成于Cadence标准的全定制设计流程中。用户可以在ADE中方便地切换Spectre、UltraSim和AMS Designer等不同的仿真器,完成从模块级电路到全芯片的仿真与调试。在ADE界面下,设计者可以根据需要产生Spectre或标准SPICE网表,并以图形化方式快速设置仿真模式和速度等选项,获得良好的精度和速度匹配。此外,ADE也为UltraSim的时序、功耗、可靠性分析提供友好界面。

5. 电源网络分析、设计检查及其它

对于包含电源网络的电路,电阻网络的存在会降低仿真速度。为此,UltraSim推出了UPS方案,通过把电源电阻网络和其它电路分离,由UPS和UltraSim协同仿真。因此,在得到3-5倍加速仿真的同时,仍能得到精确的IR压降分析报告。

为了发现和修改设计中的错误,UltraSim提供多种设计检查功能,包括过载电流检查、电压越界检查、高阻结点检查、DC漏电流路径检查等。Ultrasim的时序分析工具可以帮助设计者来检测转换时间、建立时间、保持时间或者脉冲宽度上的错误,而功耗分析工具可以报告指定时间、指定子电路端口上的电流和功耗。

对于高频电路,Ultrasim提供了Fast Envelope仿真等。

仿真实例

下面部分通过两个典型实例说明如何用UltraSim仿真模拟/数模混合电路。

1. ∑-Δ ADC

相对于Nyquist采样ADC,过采样ADC包含的模拟器件数目较少,但由于过采样率很高,往往需要较长的瞬态仿真时间。本实例为某∑-ΔADC的后仿真。该电路内部最高时钟频率为450MHz,包含1个VerilogA模块、瞬态分析时间为20us,FFT分析采样点4,751。表1为Spectre和UltraSim的仿真结果对比。

表2 :RC减小前后器件统计。

这里仿真选项设为sim_mode=MS(模拟/数模混合电路的全局模式一般采用默认的MS模式)、speed=1(定义仿真器的容差,相当于Spectre的Moderate模式)。

为保证仿真精度,后仿真使用了默认值(postl=1),即较保守的RC减小技术。从表2中可以看到,RC减小后,电容的数量从60.7K减小到1.3K,其中耦合电容数仅为529。由于采用层次化和同构技术,juncap的数量从27K减小到2.11K。最终,UltraSim获得11倍的速度提高。

2. RF PLL

本实例为一用于无线通讯的PLL,其前仿真网表包含31K MOSFET、600BJT、75K二极管和大约1.5K R/C。参考时钟频率为33MHz,LC型VCO频率为3.9GHz。UltraSim参考设置为:

.usim_opt sim_mode=ms speed=5 analog=3

.usim_opt speed=4 method=gear2 IPLL.VCO

.usim_opt sim_mode=df IPLL.LOGIC

这里,我们采用了MS仿真模式,其中analog=3使UltraSim在电路划分时考虑更大的反馈回路以保证精度;speed=4, method=gear2局部地加于VCO模块(通常RF VCO需要使用gear或trap收敛算法以及更小的容差)。数字模块采用了df模式,即用简化的数字表格模型来进一步提高速度。UltraSim仅用了19小时就完成25us瞬态仿真,甚至超过设计者的期望值。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>