- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

浅析ISSP结构化ASIC解决方案

结构化专用集成电路(structured ASIC)对设计工程师而言还是一个新名词,然而目前已经有多家公司正计划涉足这一领域。快速硅解决方案平台(ISSP)是一种结构化ASIC解决方案,该技术适合于高速ASIC设计,这是因为ISSP可以解决设计人员的很多问题:ISSP器件为多达七层金属化设计,其中最上两层可以由客户定制以符合不同的设计要求,下面几层由IP、可测试性设计(DFT)模块以及为减少深亚微米(DSM)效应和时钟畸变问题的电路。这些设计模块和电路有助于提高测试覆盖率,并减少可测试性设计需求,包括SCAN、BIST、BSCAN及TestBus的所有的测试技术都嵌入在基本阵列中。采用现有的ISSP技术可以实现工作频率高达300MHz的系统性能。

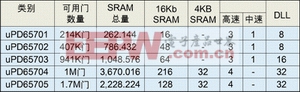

表1所示的ISSP-STD器件是当前用户设计中可以采用的五种,从表中可以看出这些器件最高可以达到170万个逻辑门密度,以及307Mb嵌入式可配置内存。

ISSP-HIS系列

在网络和通讯这些高速应用系统中都会有一些高速接口,这些接口可以是以单独的芯片或集成在专用标准产品(ASSP)或ASIC中的内核形式实现。用单独的芯片作为接口的解决方案需要更大面积、更高功耗,还需要提供高速时钟信号,此外其成本也更高。相对而言,ASIC高速接口内核的方法是一种更可取方案,NEC电子根据该方案推出了ISSP技术的子系列 - ISSP高速接口(ISSP-HIS)系列。

将具有ISSP-HIS基本阵列的ISSP系列扩大,这意味着通过工艺认证的串并/并串转换器(SERDES)内核已经可以适用于这种技术。该内核的工作速率可以从622Mbps到1.25Gbps以及2.5Gbps到3.125Gbps,完全能满足不同实际应用要求。此外,该内核还可以支持Infiniband、XAUI、千兆以太网以及PCI-Express接口。设计中我们同时还考虑到了功耗问题,在3.125Gbps时每个信道为220mW,完全满足客户的低功耗ASIC设计要求。

ISSP-HSI的发展过程中包含三种不同密度的基本阵列。最小的基本阵列有四个SERDES通道,最大的基本阵列有16个SERDES通道,可以将高达2Mb的嵌入式可配置内存与一百万可用门集成。除SERDES内核外,预先还集成了四个模拟锁相环(APLL)和16个延迟线环路(DLL)。器件的内部供电电压为1.5V,输入/输出电压为1.5V、2.5 V和3.3V。

高性能的设计同时还需要先进的封装技术。因此,我们对ISSP采用两种新封装形式,即先进的球栅阵列(ABGA)和倒装芯片球栅阵列(FCBGA)。ABGA是采用线邦定的倒装芯片封装形式。

成熟的设计流程

上面所述的技术将独特的ISSP技术与ASIC的性能和功能优点以及传统门阵列的低成本和短设计周期优势相结合。此外,设计工程师还可以访问NEC的OpenCAD设计环境,它包含物理底层规划、时钟驱动设计、分层设计以及其它先进的设计技术。

此外,NEC电子还与Synplicity和Tera Systems公司合作。Synplicity利用定制映射技术对Synplify ASIC综合软件进行了优化以支持ISSP架构,并开发一个FPGA和ASIC设计工程师都可理解的综合设计流程。Tera Systems公司与NEC电子合作开发出一种优化ISSP寄存器传输级(RTL)规则检查和规划工具,保证了在RTL设计阶段的时序收敛和物理实现。

ISSP2 - 90nm结构化ASIC解决方案

新结构化ASIC的ISSP2系列可以提供多达四百万个可用的ASIC门、10Mb嵌入式可配置内存,以及实现500MHz的工作频率。ISSP2的性能和集成度超过最先进的FPGA,但设计周期与ISSP一样,非重复的工程成本低。

ISSP2器件集成了10Gbps单端口SERDES接口和下一代3Gbps串行ATA接口,使之成为高端计算和高带宽网络应用的理想器件。ISSP2系列基于NEC公司的90纳米技术(UX6),UX6技术是用在ASIC和ISSP上的先进技术,该技术适用于宽带通讯、高端计算和存储系统以及移动计算等低功耗、高性能应用。ISSP2器件的结构采用五到七层的金属化布线设计,其中上面两层可根据客户需要定制,以满足不同的设计需要,下面的几层是根据NEC电子IP和DFT模块预先设计好的,包括降低信号完整性和时钟畸变等问题的电路。基于这些IP和功能模块可以极大地减少ASIC的开发成本,不需要客户为解决深亚微米时钟和信号完整性问题而投入大量设计人员成本和高昂的工具成本。

ISSP开放式联盟计划

ISSP的开放式联盟计划是使ISSP成为广泛应用的结构化ASIC设计平台的推广策略一部分。在该计划中将成立ISSP认证设计室、ISSP认证第三方IP内核及EDA供应商联盟。计划中的认证设计室、认证第三方IP和EDA供应商联盟三部分使客户能够很快开发出以ISSP为基础的解决方案。在这个计划中,NEC电子将把客户推荐给已通过认证具有ISSP设计能力的设计公司。所有通过认证的公司在需要的情况下都可以得到便利的技术培训和技术支持,并可以不断更新ISSP库和设计手册。必要时这些公司还可以使用NEC电子的设计工具,加入他们自己的或从其它渠道获得的IP。通过ISSP认证的设计公司将发送一份签收(sign off)网表或GDSII给NEC制造原型芯片。

为进一步增加更多的ISSP IP,第三方IP供应商也可以将他们的IP内核加入到ISSP平台中。经认证后,处理器和接口这一类IP内核将被增加到IP库中。总之,ISSP技术的目标是使用户跟上市场需求的步伐,具体体现在采用90nm技术、用易用的设计流程得出优化的设计结果,以及与第三方合作为用户提高他们的关键竞争力等方面。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...