- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

CMOS低噪声放大器中的输入匹配研究与设计

录入:edatop.com 点击:

1 引言

作为接收机的第一级,LNA的性能对整个接收机系统的性能起着至关重要的作用,因为整个系统的信噪比(SNR)很大程度上取决于LNA的噪声系数(NF)和增益。因此,设计性能良好的LNA成为射频前端设计的重要目标。由于低噪声放大器的各个指标常常会发生矛盾,彼此不能兼顾,因此设计是在噪声系数、增益、稳定性、阻抗匹配以及线性范围等指标之间采取折中考虑。最近很多射频集成电路都是采用CMOS工艺来实现的,尤其是0.18μm的CMOS工艺很适于集成的SOC设计[1-2]。

目前最常见的输入匹配结构是源极电感负反馈结构,该结构有利于获得高增益和低噪声系数,但是存在较大的缺陷,即需要提供一个大感值的栅极电感(Lg)。在实际标准的CMOS工艺下集成实现一个大感值的片上螺旋电感往往比较困难,而采用片外电感又不利于实现电路的集成及小型化,并且由于大感值栅极电感的寄生阻抗比较大,相应地产生热噪声也会比较大。该文采用改进型输入匹配结构,用一个并联的小值LC网络来代替电感值比较大的栅极电感,并从进一步降低噪声系数和简化电路的角度考虑,移除源极负反馈电感(Ls)[3]。

2 理论分析

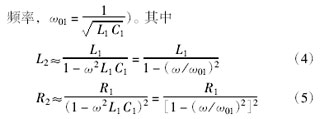

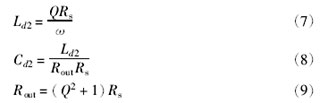

传统的输入阻抗匹配结构是源极电感负反馈结构,其输入阻抗表达式为[4]

Zin=(jωL2-jωCgs)+(R2+Rg+Ri) (6)

式中: Ri, Rg, Cgs的具体定义见文献[3]。

由于电阻R2并不是一个实际的物理阻抗,而是由R1等效而来,因此其产生的热噪声比相同阻抗值的实际物理电阻产生的热噪声要小。这样,通过移除Ls并利用LC网络小值寄生阻抗来进行阻抗匹配,可以进一步降低LNA的噪声系数。

3 电路设计

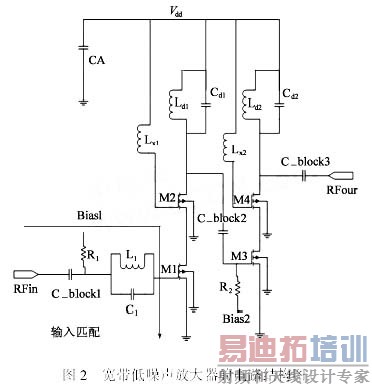

采用改进的输入匹配,基于BSIM30.18μm模型,设计出了适用于无线接收机用CMOS宽带(5.1~5.8GHz)低噪声放大器的电路结构。

宽带低噪声放大器设计的关键是提供足够的增益来克服接收机以下几级引入的噪声干扰,而其自身的噪声系数则要尽量低,同时还要具备好的输入输出阻抗匹配及良好的线性动态范围。该设计采用两级放大并采纳改进的输入阻抗匹配结构。L1的电感值为1nH,C1的电容值为0.57pF,根据式(1),(2),该LC并联网络会产生3nH的等效电感L2和25Ω的等效电阻R2,MOS管M1和M2的栅宽为120μm,根据式(3),总的输入阻抗约为35Ω。

C_block1,C_block2和C_block3均为隔直电容,它们的容值均选择为10pF。综合考虑足够的增益、足够大的线性范围和较低的功耗,该设计中LNA工作电压1.5V,偏置直流电流0.6mA,功耗9mW。

4 结果及讨论

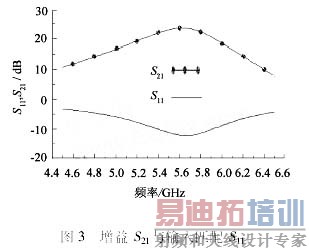

基于改进型输入匹配结构设计的工作频段为5.1~5.8GHz的宽带,CMOS低噪声放大器的各项性能参数由ADS(advanceddesignsystem)仿真给出。

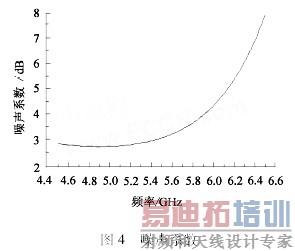

在5.1~5.8GHz频段内,LNA的噪声系数为2.75~3.65dB(图4)。这样低的噪声系数在WLAN宽带应用中是可以被接受的。

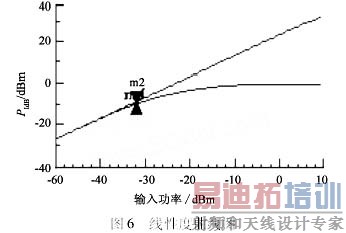

LNA还有一个重要的性能参数,即线性度。图6为仿真结果1dB压缩点P1dB曲线图,由图可看出,P1dB约为-10dBm,线性度良好,有利于不失真地对大信号进行放大。

作为接收机的第一级,LNA的性能对整个接收机系统的性能起着至关重要的作用,因为整个系统的信噪比(SNR)很大程度上取决于LNA的噪声系数(NF)和增益。因此,设计性能良好的LNA成为射频前端设计的重要目标。由于低噪声放大器的各个指标常常会发生矛盾,彼此不能兼顾,因此设计是在噪声系数、增益、稳定性、阻抗匹配以及线性范围等指标之间采取折中考虑。最近很多射频集成电路都是采用CMOS工艺来实现的,尤其是0.18μm的CMOS工艺很适于集成的SOC设计[1-2]。

目前最常见的输入匹配结构是源极电感负反馈结构,该结构有利于获得高增益和低噪声系数,但是存在较大的缺陷,即需要提供一个大感值的栅极电感(Lg)。在实际标准的CMOS工艺下集成实现一个大感值的片上螺旋电感往往比较困难,而采用片外电感又不利于实现电路的集成及小型化,并且由于大感值栅极电感的寄生阻抗比较大,相应地产生热噪声也会比较大。该文采用改进型输入匹配结构,用一个并联的小值LC网络来代替电感值比较大的栅极电感,并从进一步降低噪声系数和简化电路的角度考虑,移除源极负反馈电感(Ls)[3]。

2 理论分析

传统的输入阻抗匹配结构是源极电感负反馈结构,其输入阻抗表达式为[4]

Zin=(jωL2-jωCgs)+(R2+Rg+Ri) (6)

式中: Ri, Rg, Cgs的具体定义见文献[3]。

由于电阻R2并不是一个实际的物理阻抗,而是由R1等效而来,因此其产生的热噪声比相同阻抗值的实际物理电阻产生的热噪声要小。这样,通过移除Ls并利用LC网络小值寄生阻抗来进行阻抗匹配,可以进一步降低LNA的噪声系数。

3 电路设计

采用改进的输入匹配,基于BSIM30.18μm模型,设计出了适用于无线接收机用CMOS宽带(5.1~5.8GHz)低噪声放大器的电路结构。

宽带低噪声放大器设计的关键是提供足够的增益来克服接收机以下几级引入的噪声干扰,而其自身的噪声系数则要尽量低,同时还要具备好的输入输出阻抗匹配及良好的线性动态范围。该设计采用两级放大并采纳改进的输入阻抗匹配结构。L1的电感值为1nH,C1的电容值为0.57pF,根据式(1),(2),该LC并联网络会产生3nH的等效电感L2和25Ω的等效电阻R2,MOS管M1和M2的栅宽为120μm,根据式(3),总的输入阻抗约为35Ω。

C_block1,C_block2和C_block3均为隔直电容,它们的容值均选择为10pF。综合考虑足够的增益、足够大的线性范围和较低的功耗,该设计中LNA工作电压1.5V,偏置直流电流0.6mA,功耗9mW。

4 结果及讨论

基于改进型输入匹配结构设计的工作频段为5.1~5.8GHz的宽带,CMOS低噪声放大器的各项性能参数由ADS(advanceddesignsystem)仿真给出。

在5.1~5.8GHz频段内,LNA的噪声系数为2.75~3.65dB(图4)。这样低的噪声系数在WLAN宽带应用中是可以被接受的。

LNA还有一个重要的性能参数,即线性度。图6为仿真结果1dB压缩点P1dB曲线图,由图可看出,P1dB约为-10dBm,线性度良好,有利于不失真地对大信号进行放大。

4 结语

在对传统源极电感负反馈输入结构分析的基础上加以改进,利用一个小值LC并联网络代替大感值的栅极电感,并从简化电路和进一步降低噪声的角度考虑,移除源极负反馈电感。将改进的输入匹配应用到适用于无线接收机用的宽带低噪声放大器的设计中,结果表明,虽然输入匹配性能稍稍有点恶化,但是仍然可以满足实际的应用需要,并且工艺上电感值小的片上螺旋电感更易实现,电路的整体噪声性能也得到改善,可以应用到工作频率在5.1~5.8GHz的无线接收机中。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:实现液晶显示器低温显示的方法

下一篇:新型雷达发射机控制台显示控制技术的研究

射频和天线工程师培训课程详情>>