- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

深圳某公司高级layout工程师面试题目,看看你会几题.

是拉线工人,还是布线工程师,还是pcb高级工程师,看看你们平时的积累如何。

(回复超过100页公布标准答案)

1,PCB上的阻抗怎么控制?

2,信号线的传输速率是多少?

3,CMOS器件输入管脚在电路中要如何处理?为什么?

4,TTL电路不能直接驱动CMOS电路的原因是什么?

5,较长的时钟信号要走带状线的原因是什么?

6,四片DDR2顶底对贴布局需要注意哪些方面?试讲出其中六点。

7,ODT信号有什么作用?layout应如何处理?

8,VTT和VREF是否能共用?为什么?

9,DDR3的最高工作频率是多少?

10,多片DDR3为什么优先走fly-by拓扑?

***********************************************

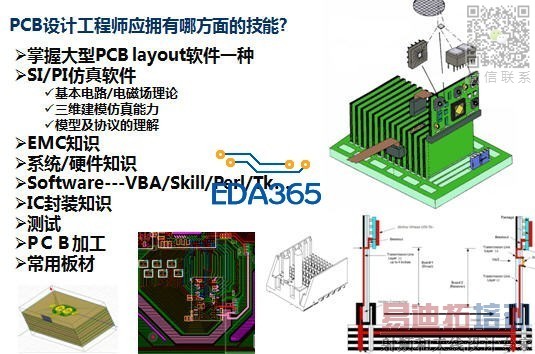

“PCB设计师职业规划与思考”

***********************************************

关于答案,敬请关注5月31日的EDA365培训活动系列

或回复超过100页将公布标准答案!

***********************************************

我就根据自己的认识来做一下

1 PCB的阻抗怎么控制

跟阻抗有关的参数有:铜箔的厚度,走线的宽度,板子的介电参数,参考层的高度,如果是共面波模型还跟参考面的间距有关系。控制阻抗就要确保这些精度。另外在制造或者其他的因素下造成的阻抗不连续,可以使用串接电阻来吸收反射。

2 信号线的传输速率是多少?

这个不知道考的啥?我知道信号的传输速度是接近光速。不同的信号,传输的速率是不一样的。

3 CMOS器件输入管脚在电路中要如何处理?为什么?

需要在输入管脚串电阻或者并联电容,因为CMOS的输入端阻抗很高,对静电很敏感

4 TTL电路不能直接驱动CMOS电路的原因是什么?

电压不匹配,TTL的H>=2.4V,L==0.8*VCC,L<=0.1*VCC

5 较长的时钟信号要走带状线的原因是什么?

带状线指两边都有参考平面的传输线,这个是定义。周期性的时钟线具有很强的辐射能力,当走线长了之后,更容易辐射。所以走成带状线那么可以减少辐射。

6四片DDR2顶底对贴布局需要注意哪些方面?试讲出其中六点。

没有弄过,不敢发表意见。

7ODT信号有什么作用?layout应如何处理?

ODT信号用来开启ODT功能,主IC的是输出,DDR2的是输入。由于是控制线,跟其他的控制线等长。

8VTT和VREF是否能共用?为什么?

不能,电流大小不一样。两个电压都是一样,但是VTT是给终结电阻供电的,电流比较大,干扰也比较大。而VREF是给参考电压用的,电流很小,电压的精度要求高。最好分开。

剩下两个都不知道。

尝试着答一答。

1,pcb上的阻抗怎么控制?

阻抗受很多因素影响,单端线受线宽、介电参数、叠层厚度影响(我们一般给制版厂算,然后我们遵守),差分还受线距影响。

2,信号线的传输速率是多少?

我们一般估计是6inch/ns 。但是不同介电常数的速度不一样、微带线比带状线快。

3,CMOS器件输入管脚在电路中要如何处理?为什么?

我印象中好像没有专门因为是CMOS器件而作处理。输入处理主要考虑电平标准和信号边缘。

4,TTL电路不能直接驱动CMOS电路的原因是什么?

基本没用过TTL电平的器件。8楼说电平标准不一样,但是CMOS也有不同的电平标准。接信号前还是得确认输入电压电流是否正确。

5,较长的时钟信号要走带状线的原因是什么?

除8楼的原因外,我觉得应该还有时钟是重要敏感信号,怕外部干扰。另外近期刚看到,带状线的远端串扰近似为0(《信号完整性揭秘-于博士SI设计手记》于争)。我想这也是个优势。

6,四片DDR2顶底对贴布局需要注意哪些方面?试讲出其中六点。

没有布过。只布过单层的。

7,ODT信号有什么作用?layout应如何处理?)

片上端接选择。在双向数据线中用(个人理解因为是双向,所以有时候需要端接有时候不需要)。

layout要求如8楼。

8,VTT和VREF是否能共用?为什么?

不能共用,VREF是参考电压,VTT是端接电压。VTT电压在内存操作的过程中会有很大噪声。

9,DDR3的最高工作频率是多少?

2000MHz(百度百科)

10,多片DDR3为什么优先走fly-by拓扑?

fly-by如菊花链,减少分叉长度。个人理解分支很短的话类似集总线了。前面的芯片对后面的芯片影响小(肯定还是有影响的),后面的芯片对前面的影响大。

有不对的话请版主赐教。

看了以后就知道自己该做啥了

顶一下先,还真没一道题会。看来路途遥远啊

坐等大师讲解

坐等讲解

都有那么点印象,学过,只有两三题解释得下来。面墙查答案去。

坐等正确答案

哎,楼上的能答得这样感觉都好厉害了。

顶8楼的,添加一下,

2,信号速率V=11.8/Er^0.5 inch/ns,Er是板材相对介电常数,11.8inch/ns是电磁波在真空中传输速率

3.补充就是CMOS输入管脚阻抗高,管脚对外界干扰信号敏感,一般上拉接电源或下拉接地。

9 .DDR3最高工作频率1600Mhz

10,还是等大师来精确解答

对于第8题,一般电路中即使两个不同电源电压相同,但是也不直接共用的,相互之间易干扰,对系统稳定性也容易造成影响

论坛里果然高手如云

学习了

学习了,不错

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PADS LOGIC 做part decal时SWAP的作用

下一篇:两片DDR3,但有两组 差分时钟该怎么等长