HFSS 2015 3D Layout界面介绍

-

概述:

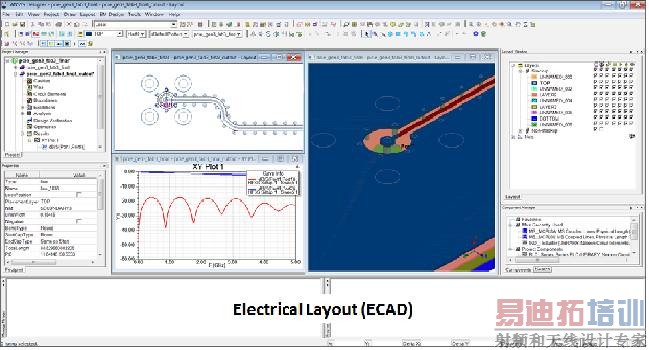

HFSS 3D Layout界面对于从事分层几何结构或高速组件(包括片上嵌入式无源组件、IC封装和PCB互联等)版图工作的电子设计人员来说是一个理想选择。从HFSS2014开始,这类设计可方便地在HFSS电气版图环境中进行建模,与此同时还可对所有3D特性进行参数化仿真,如走线厚度和蚀刻以及接合线、焊料凸块和焊球等。在HFSS 3D Layout版图界面中使用集成的ANSYS Optimetrics工具可方便地将走线宽度等几何结构参数进行参数化和优化,大幅提升HFSS在信号完整性方面的应用效率。

-

HFSS 3D Layout界面的特点:

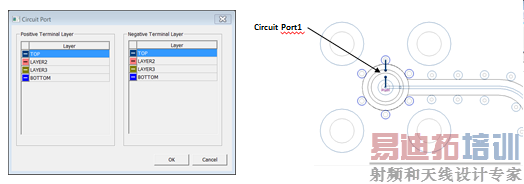

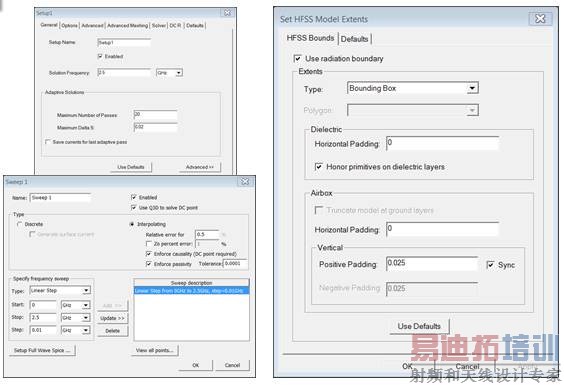

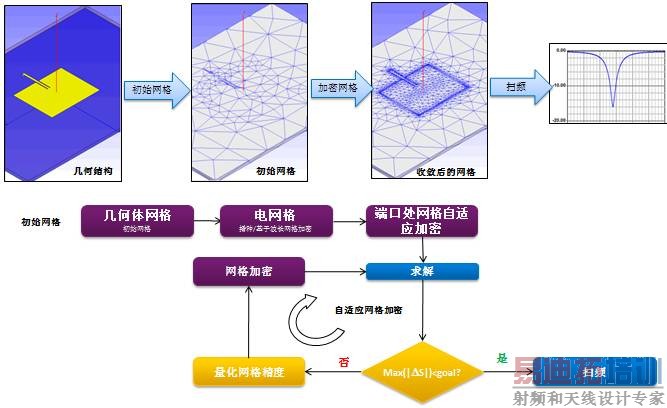

1.仿真设置高度自动化:借助HFSS 3D Layout版图建模,材料属性、端口设置和边界条件都可在版图界面中自动设置。高级phi网格划分技术已包含在3D电气CAD/版图中。这种专用的网格划分技术为网格划分硅衬底、再分配层、电子封装和印刷电路板进行了优化,可提供难以置信的高速度,同时兼具高可靠性和大容量,能够满足复杂结构网格划分过程的需求。

-

层叠编辑器:

-

端口设置:

-

边界尺寸和求解设置

2.第三方EDA接口更加顺畅:在Cadence Design Systems、Mentor Graphics和Zuken中创建的模型可直接导入HFSS,无需额外设置。封装版图可以参数化,以进行调校和敏感度计算,从而了解工艺对阻抗变化的影响。界面支持传统的ECAD基元,如焊盘、迹线、接合线和焊球,为数字和RF工程师提供了新型的尖端解决方案。

3.设计流程上与主流Cadence软件的高度集成:Cadence软件的用户通过HFSS 3-D版图技术,可直接从Allegro? Package Designer、Allegro PCB Designer、SiP Digital Layout或Virtuoso? Analog Design Environment中设置可在HFSS中进行分析的直接求解型芯片、封装和PCB仿真。所有必要的HFSS设置步骤(几何结构和网络选择、材料属性、激励和边界条件)都在Cadence软件中完成,并一键传送到HFSS中求解电磁场和S参数。用户无需离开Cadence界面。

-

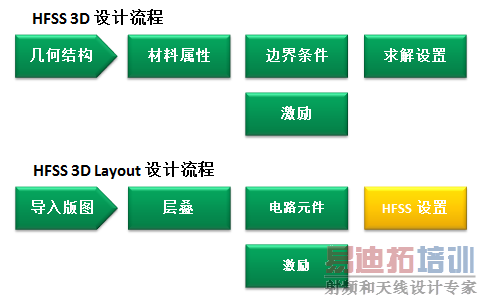

HFSS 3D Layout设计仿真流程:

新的HFSS 3D Layout界面在设计流程和仿真流程上与原有的HFSS 3D操作流程保持了一致,在算法和网格技术上采用的都是HFSS经典的FEM频域求解器。

-

HFSS 3D Layout的主要特点总结:

-

全自动HFSS端口创建和设置;

-

版图、层叠和焊盘编辑器;

-

参数化设计环境;

-

保留版图中的迹线特性和网络信息;

-

层级化设计:芯片–封装–板;

-

Pin to Pin自动化工具:提供端到端的全通道自动化建模和仿真。