- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

直流偏移校正功能与ADS58H40 PCB布局优化

ADS58H40 是一款由德州仪器(TI)推出的四通道、11/14 比特、采样 250MSPS、接收 90MHz带宽的高性能高速模数转换器。它同时具有用于反馈的 125MHz 带宽的 Burst Mode 与用于接收的 90MHz 带宽的 SNRBoost Mode,适用于基站收发信机的反馈与接收通道。

目前用于基站收发信机的高速模数转换器(ADC)大多都具有直流偏移校正功能(DC offset correction function)。它用于校正 ADC 接收到的直流,以免其降低接收机的性能。但是此功能同时也会引起 ADC 的码域翻转(code toggle),如果 PCB 布局不当,会造成 ADC 采集小信号功率不准确。本文以 ADS58H40 为例,分析了码域翻转干扰所带来的问题,并提供了PCB 优化解决方案。

直流偏移(DC offset)是由外界的直流信号分量与原信号的直流叠加形成。在基站收发信机中,它主要是由本振泄露与混频器或IQ 解调器的非线性产生。直流偏移会对有用信号形成干扰,通常需要使用ADC 的直流偏移校正功能来抑制它。

从码域上来看对于一个理想的11 bit ADC,其中间码应该是2^(11-1)=1024。用二进制补码来表示就是0x000。由于二进制补码的最高位表示符号位,所以对应的11 bit 数据范围是从0x000 到0x7FF。0x7FF 表示-1,对应为1023。在无有用信号输入时,理想状态下,11 bit ADC采集出来的信号在码域就应该为0x000。但是事实上外界还有热噪声(thermal noise)与直流偏移会被ADC 采集到。直流偏移在码域上会使ADC 空采所获得的码相对0x000 向上偏移一些,而热噪声信号的自然波动也会叠加到直流偏移所表示的码上面。ADC 的DC offset correction function 会修正直流偏移引起的码域误差,将其重新校正到0x000。

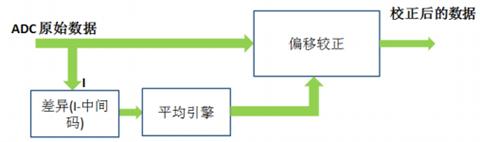

ADC 的DC offset correction function 的工作流程如下:

图1、DC offset correction

下面用两张图示来对比说明ADC 未使能与使能DC offset correction function 在码域上的区别。

在未使用ADC 的DC offset correction function 时,11 bit ADC 空采所得到的热噪声与直流偏移在码域图示如下:

图2、DC Offset Correction Disabled for an idle 11bit ADC channel

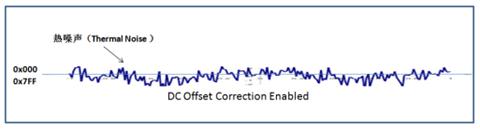

在使用ADC 的DC offset correction function 时,11 bit ADC 空采所得到的热噪声与直流偏移在码域图示如下:

图3、DC Offset Correction Enabled for an idle 11bit ADC channel

通过对比发现使能ADC 的DC offset correction function 后,直流偏移引起的码域误差被修正,热噪声在码域上也从基本在0x000 码以上围绕着直流偏移波动,变成了围绕着0x000码波动。因此在使能DC offset correction function 时,热噪声的自然波动会引起码域从0x000 到0x7FF 的随机翻转。体现在ADC 的11 bit 数据线上就是ADC 空采时,所有数据线的电平都同时在逻辑0 与逻辑1 之间切换。此时数据线对外的干扰是最大的。如果在PCB 布局上不够谨慎,就会使这个干扰信号耦合到ADC 的模拟输入端。虽然这个耦合的干扰信号幅度并不大,但是它对ADC 的输入信号,尤其是输入的小信号在频域上会形成波浪型干扰,在ADC 空采时,则体现为纹波底噪(ripple noise floor)。

2、码域翻转干扰所带来的问题

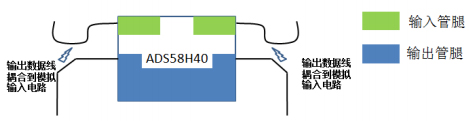

以ADS58H40 为例,图示说明码域翻转干扰信号耦合到ADC 模拟输入端的后果。

图4、Digital output coupling to input

在PCB 布局不理想时,如上图所示输出数据端直接或间接的通过时钟或ADC 的VCM 耦合到了ADC 的模拟输入端。

受此干扰信号影响,将ADS58H40 通道空采得到的数据做FFT 变换得到的频域图如下:

图5、Ripple noise floor caused by code toggle interference coupling

从图中可以清晰的看到 ADC 采集到的是波浪型底噪,它略微的恶化了 ADC 的信噪比(SNR),并且会导致小信号的幅度测量不准确,影响接收机灵敏度的测试。

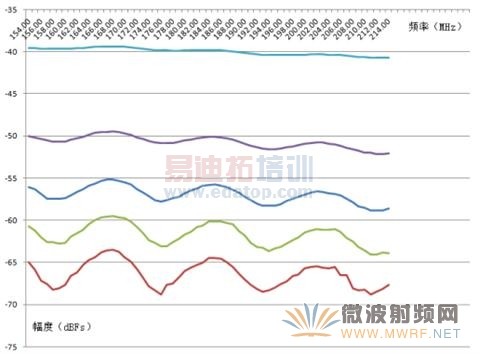

为了进一步说明码域翻转干扰的影响。用不同幅度的信号输入给 ADS58H40 进行扫频测试, 将采集到的数据制图如下:

图6、Frequency scan for different input signal level with interference

ADS58H40 的采样时钟为 245.76MHz,针对其第二奈奎斯特域的中心 60M 范围,使用 5 个功率等级进行扫频。在功率大于-40dBFs 时,由于 PCB 布局不当所引入的码域翻转干扰对输入信号影响很小(由于 ADC 前端有滤波器的关系,所以输入信号不是完全平整的)。但是随着输入信号功率的减小此干扰对输入信号的影响越来越大,在输入信号幅度低于-60dBFs 时,去除模拟输入端滤波器的影响后其引起的功率误差依然可以达到 3dB 以上。

3、针对码域翻转干扰的 ADS58H40 PCB 布局优化

为了避免码域翻转干扰耦合到 ADC 的模拟输入端,需要针对性的避免一些不当的 PCB 布局。码域翻转干扰可以通过三个途径耦合:(1)数据输出线与模拟输入电路布局很近且平行,直接耦合。(2)数据输出线耦合到 ADC 的时钟信号再间接耦合到模拟输入端。(3)数据输出线耦合到 ADC 的 VCM,再通过 VCM 间接耦合到模拟输入端。

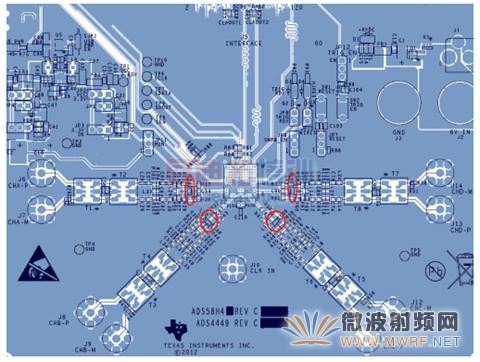

图7、ADS58H40 PCB layout

上图为 ADS58H40EVM 评估板的 PCB 布局,在基站收发信机上不会有这么大的空间来给其布局,一些走线难免会离得很近,所以针对码域翻转干扰的三个耦合途径,建议对 ADS58H40 PCB布局做出以下三个优化:

(1) ADS58H40 的数据输出 LVDS 线与模拟输入电路分开布局,不要平行或交叉。 (2) ADS58H40 的采样时钟线与随路时钟线布局尽可能的远离模拟输入端,不要与其近距离平行。 (3) ADS58H40 的 VCM 线最好通过过孔直接从模拟输入电路的差分端中间接入,如上图四个红色圈的中心。在模拟输入端 VCM 接入口必须加上对地的滤波电容。VCM 信号不要做成 VCM 电源平面,而且布局时使其尽量远离数据输出线。

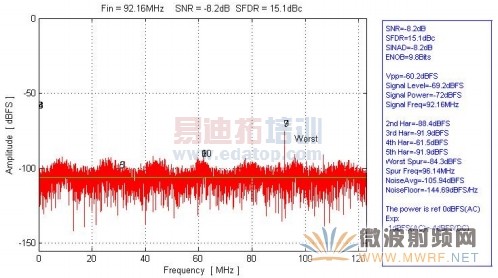

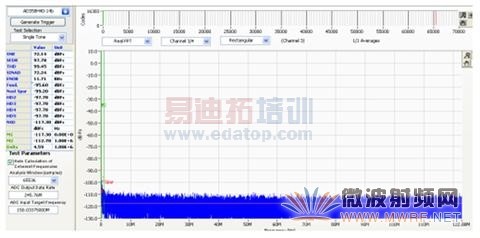

经过 PCB 布局优化的 ADS58H40 使能 DC offset correction function 后不再具有纹波底噪,而且 ADC 底噪更佳(图8)。在-60dBFs 的小信号扫频测试中,去除模拟输入端滤波器的影响后其波动在 0.5dB 以内。

图8、Normal noise floor after PCB layout optimization

4、结论

ADC 的 DC offset correction function 可以有效的抑制直流偏移所带来的误差。不过在PCB 布局不当时,开启此功能所带来的码域翻转干扰会使 ADC 具有纹波底噪并且其采集到的小信号幅度波动会达到 3dB 以上。通过针对性的 PCB 布局优化可以有效的解决这个问题,将-60dBFs的小信号波动控制在 0.5dB 以内。

作者:凃浩异 (Lance Tu),TI

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:薄膜体声波谐振器及其应用

下一篇:超宽带系统中ADC前端匹配网络设计