- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

3.7 GHz宽带CMOS LC VCO的设计

0 引言

用于射频系 统(如无线接收机)的本振电路需要有足够大的调节范围以及良的性能。CMOS VCO由于可用于实现全集成的无线接收机,一直备受关注。然而由于受到MOS管和电感寄生电容的影响,CMOS LCVCO的调节范围相对于采用HBT、SiGe和MESFET等工艺的振荡器来说要小得多。同时VCO的振荡频率受工艺、电源电压以及温度(PVT)的 影响很大,这需要VCO有足够的调节范围以补偿PVT变化所带来的影响。

A.Kral等人第一次提出了采用开关电容来增加调节范围,本文采用类似的方法设计了一款工作在3.7 GHz的VCO,使其工作频率范围达到了600 MHz。片上电感的性能对VCO的性能有着至关重要的影响,针对使用的工艺中电感存在的问题进行了优化设计,提高了电感的Q值。同时也对射频开关进行了分 析和优化,使其对VCO性能的影响减少到最小。

1 LC VCO的电路设计

1.1 VC0结构的选择

常用的VCO结构主要有三种:单nMOS结构、单pMOS结构、nMOS和pMOS电流复用结构。在0.18μm的工艺条件下受到阈值和输出幅度的限制, 电流复用结构已很少被采用。在相同功耗的情况下,单pMOS结构的VCO相噪性能要比单nMOS的VCO好,由于pMOS管具有限压作用,按照对大的输出 幅度的要求,采用了单nMOS结构的VCO,具体电路如图l所示。

为了满足工作频带的带宽需求同时补偿工艺、温度以及电源电压变化的影响,VCO须有很大的带宽。随着CMOS工艺的发展,VCO的工作频率不断提高同时电 源电压随之降低,导致VCO的增益变得很大,进而严重降低整个锁相环的相噪性能以及杂散性能。为了解决这个问题本文采用了离散调节和连续调节相结合的方 式:利用变容管实现VCO的连续调节,同时增加了数字控制的电容阵列实现对VCO的离散调节,这样通过相邻覆盖的子带来实现很大的调节范围。这样VCO的 调节曲线就由单一连续的调节曲线如图2(a)变成多个子带的调节曲线如图2(b)。

1.2 片上电感的设计

设计高性能LCVCO的主要问题在于设计高品质因子的谐振腔,这可以在相噪的表达式中看出来,即

式中:L(△w)是载波频率w0频偏△w处的相位噪声;k为玻尔兹曼常数;T为绝对温度;F为经验因子;A为振荡幅度;Qtank为谐振腔的品质因子。而谐振腔的品质因子可以表示为

![]()

式中:QC为电容的品质因子;QL为电感的品质因子。

电容的QC值远大于电感的QL值,所以谐振腔的Qtank值略小于电感的QL值,谐振腔的Qtank值主要取决于电感的QL值,提高电感的QL值可以明显改善VCO的相噪性能。

本设计所采用的和舰工艺的顶层金属为0.8μm的薄层金属,这对电感的QL值有着非常大的影响。在设计中,将五层金属与六层金属并联以组成两层螺旋电感, 可增加电感线圈的厚度,降低电感的串联直流电阻,进而提高电感的QL值,采用HFSS对电感进行建模得到的三维图如图3所示。

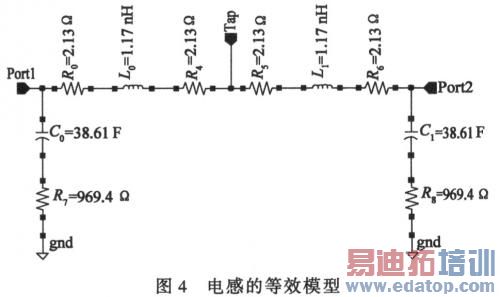

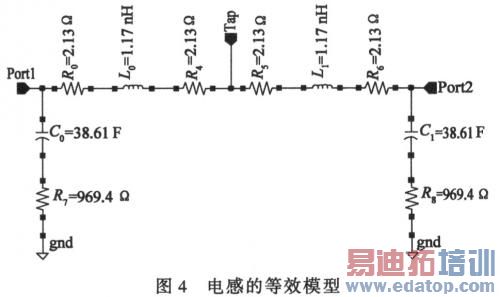

参数提取得到的π模型等效电路如图4所示。仿真得到该电感在3.7 GHz时的Q值为6.5。

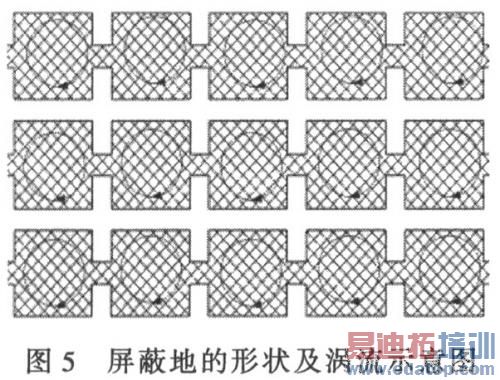

CMOS工艺普遍采用高掺杂的衬底以降低闩锁效应,对于射频无源器件来说是非常不利的,电磁场耦合到衬底产生的衬底涡流损耗和电容耦合损耗会严重降低无源 器件的Q值。在电感的设计中,通常采用地屏蔽层阻止磁场耦合到衬底以提高Q值。本文所采用的结构如图5所示,同文献中的结构相比,涡流半径变小,涡流之间 的互感也变小,进而减少了涡流磁场的强度,对电感的影响这样可以大大降低。

1.3 射频开关的设计

在CMOS工艺中,通常采用NMOS来作为射频开关。由射频开关与MIM电容组成的开关电容是谐振腔的一部分,其性能会影响到整个VCO的性能,一方面开关电容的Q值会影响到谐振腔的Q值,另一方面开关电容的最大电容与最小电容的比值会影响到VCO的调节范围。

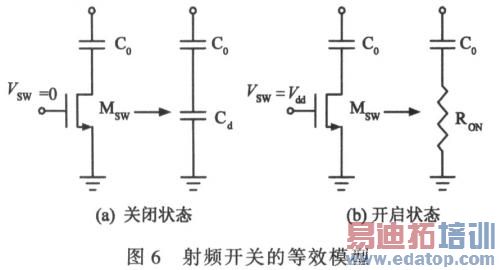

射频开关在开启和关闭时的等效电路如图6所示。

Cd是漏端寄生边缘电容,其值等于WswCdd,其中Wsw是开关管的宽度,Cdd漏端边缘电容,单位为fF/μm。

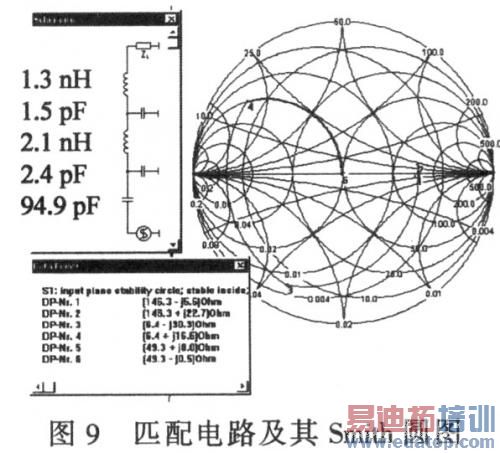

当开关处于OFF状态时,开关电容

振荡频率正比于![]() 因此调节范围取决于最大电容和最小电容的比值,由式(3)、(4)可以得到最大电容和最小电容的比值为

因此调节范围取决于最大电容和最小电容的比值,由式(3)、(4)可以得到最大电容和最小电容的比值为

![]()

从公式(5)、(6)可以看到开关电容最大的Q值与最大的调节比率之间存在冲突。C0由工作频率w0决定,因此Wsw在优化中是最重要的设计参数。

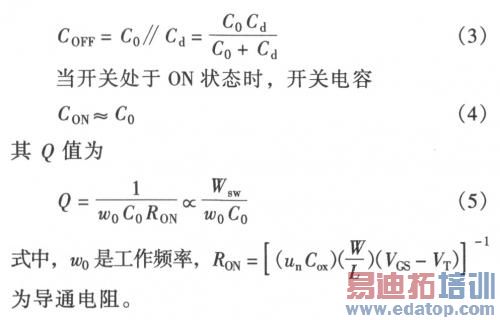

开关电容的Q值可以通过差分电容开关的方式来改善,如图7所示。当开关处于ON状态的时候只有沟道电阻RON的一半与电容串联,相比于单端的结构,Q值可以提高一倍。M2和M3为工作在亚阈值区的有源电阻,可以为MOS开关的源端和漏端提供直流偏置。

当Vsw设为0的时候,VD/S=0,VG=VDD,因此MOS开关管的VGs—VT达到最大,从差分端口看进来,等效电容达到最大,因此电路振荡在较低的频率上;当Vsw设为VDD时,VD/S=VDD,VG=0 V,电路工作在较高的频率上。

1.4 输出缓冲器及匹配电路的设计

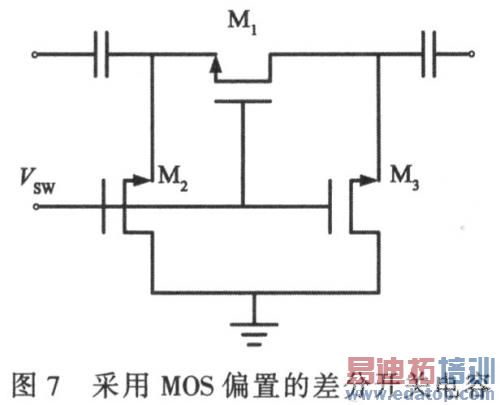

为了将VCO的输出信号送到片外,考虑到外部电容很大,采用了电感负载的缓冲器,通过选择合适的电感和电容使其谐振在3.7 GHz,如图8所示。

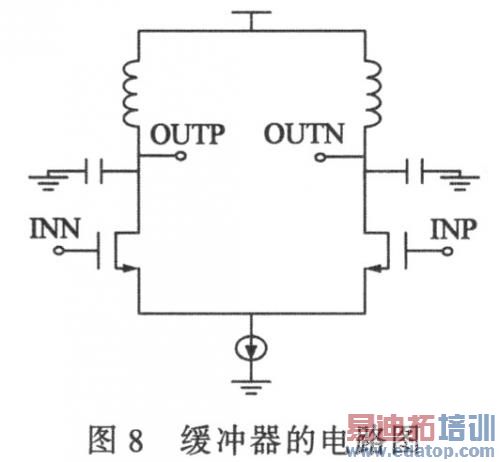

在匹配电路的设计上,选用了π型匹配电路,首先利用spectreRF仿真得到输出缓冲器的S22参数,然后构建匹配电路使其阻抗达到50 Ω。具体的匹配电路(1.3 nH为邦线电感,94.9 pF的电容为隔直电容)及其Smith圆图如图9所示。

2 测试结果

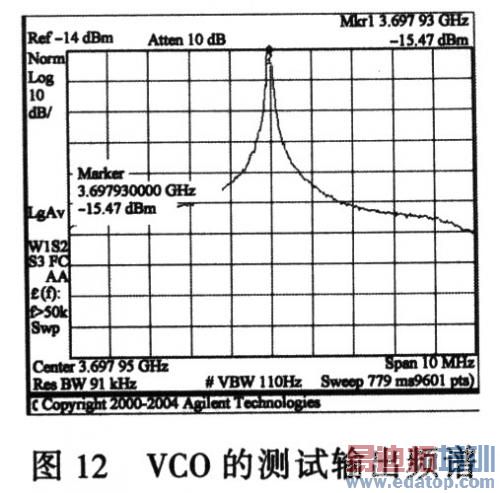

本LCVCO是用于3.7 GHz锁相环的,整个锁相环是在和舰0.18μm混合信号工艺下制造的,整个VCO的面积为0.4 mm×1 mm,芯片照片如图10所示。测试得到的VCO的工作频率为3.4~4 GHz,有16%的调节范围,调节电容阵列开关得到的频率随控制电压的变化曲线如图11所示。在1.8 V电源电压下的功耗为10 mW;在1 MHz频偏处的相位噪声为一100 dBc/Hz。测试得到的VCO输出频谱如图12所示,输出功率相对较低,主要是由于对邦线的寄生电感和寄生电容估计出现偏差导致匹配电路没有实现完全匹 配,但这对VCO性能的测试没有实质的影响。

3 结论

基于和舰0.18μmCMOS混合信号工艺设计了一款工作在3.7 GHz的LCVCO。本文着重论述了电感与射频开关的设计,通过采用电容开关阵列的方式增加了VCO的工作范围以补偿PVT的变化所带来的影响。测试结果表明,该VCO可用于锁相环和频率合成器。

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:射频结环行器的设计流程与仿真

下一篇:利用WiMAX SoC设计多扇区基站