- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

32GHz带宽实时示波器技术揭秘(六)

鹤立白雪,愚者见鹤,聪者见雪,智者见白。磷化铟示波器的出现,我一开始的注意力集中在前端放大器芯片、三维设计封装以及氮化铝散热材料的应用,芯片技术突破16GHz瓶颈,达到32GHz数量级,甚至为更高示波器实时带宽的实现做好了技术储备。但有着丰富研发和客户支持经验的孙灯亮反而认为最重要的突破是采样电路技术,新的采样电路的设计使得样点间的精度由1ps以上提高到50fs,同时克服ADC带宽的限制和未来采样率发展的瓶颈,灯亮认为这才是关键之处,并建议国内从事模数转换器研发的工程师们可留心这点,灯亮敏锐的技术视角和观察深度让我成就了这篇短文。

对于示波器来讲,带宽是第一重要的指标,我们前面讨论的磷化铟技术,主要是用来改进探头带宽、示波器前置放大器带宽、触发带宽、采样头带宽;磷化铟技术对采样系统率的贡献只在采样模块的输入缓冲芯片上,其余部分不再是磷化铟技术,事实上也没有必要使用磷化铟技术,因为其它难度较低的技术完全可以胜任。

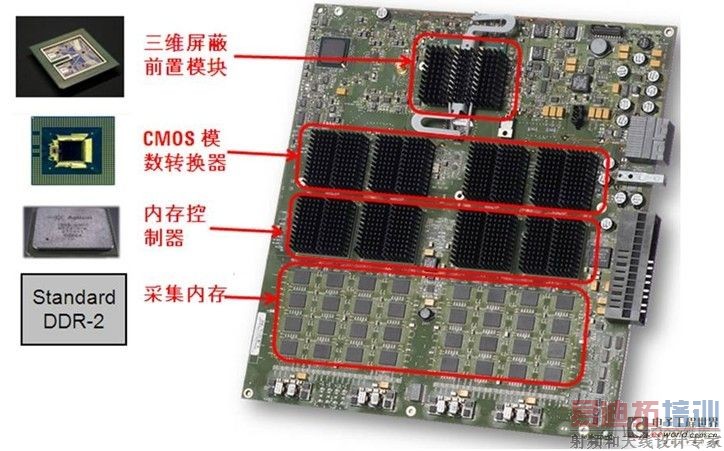

图1 磷化铟示波器内部采集板实物照片,每个通道后面有两个20GSa/s的单晶片(die)模数转换器,实时采样子系统,包括封装到前置模块中的Sampler芯片,封装到模数转换模块中的磷化铟缓冲芯片、CMOS模数转换芯片,封装到内存控制模块中的MegaZoom大数据量硬件加速处理专用芯片、内存控制器以及采集内存

图1是90000 X系列示波器被拆开后的采集板实际照片,每个示波器内部有两个这样的采集板,每个采集板支持两个通道,上有一块磷化铟前置电路多芯片模块,信号经过前置放大器和触发芯片,再进入采样头电路(英文是Sampler或Router),至此所有的信号都还在磷化铟前置模块内部,所有的高频信号在这里均得到调理,该磷化铟前置模块透过BGA波峰焊焊接到PCB上。这个采集板的PCB是20层板设计,材料采用Nelco-13 (放弃使用FR-4),板上有4000多个部件和近5000个网表(netlists)。信号从前置模块出来后,经由BGA焊盘连接到PCB上,首先进入的是模数转换器芯片,每个采集板支持两个通道,每个通道上后面有两个模数转换器,因此在该采集板上将看到4个模数转换器,再后面是内存控制器,最后进入采集内存。一个采集板上的内存是8G点,每个通道4G点,是的,物理上是每通道4G点,但如果你翻查磷化铟示波器的Datasheet,其指标是最高2G点每通道,在分段存储下,最多可达4G点,这意味着,如果有必要,打开每个通道4G的存储深度是可能的。

90000 X 磷化铟示波器的采样电路子系统架构是一项不太引起大家注意的技术创新,其创新体现在以下几个方面:

1. 采样头(Sample)在模数转换器的输入缓冲芯片之前分开,单独设计

2. 顺序延迟采样为模数转换未来发展预留空间

3. 模数转换器的输出接口重新设计,采用串行链路

采样头被封装到三维前置模块中,该采样头主要由开关、存储、滤波功能电路组成,带宽和频响由磷化铟技术解决,采样间隔的精度由延迟线和校准电路解决(所以达到50fs或更低的量级),最后该示波器达到40dB以上的无寄生动态范围,最大的技术贡献部分在于该采样头。其实,如果只看采样头部分,其支持的动态范围可以很大,瓶颈在后面的模数转换器,今天采用的是8位的模数转换器,如果采用12位模数转换器,对业界的影响有可能是震动性的。 灯亮呼吁国内同行,考虑借鉴这样的技术,国内研究磷化铟技术已经很多年了,如果集中精力用磷化铟做采样/开关保持/滤波电路,模数转换部分建议自己研发芯片,在芯片内部用低速的传统ADC(不要用多个 商用ADC在PCB电路板上拼接),这样有机会可以达到:高带宽、高采样率、高位数的高精度模数转换产品。

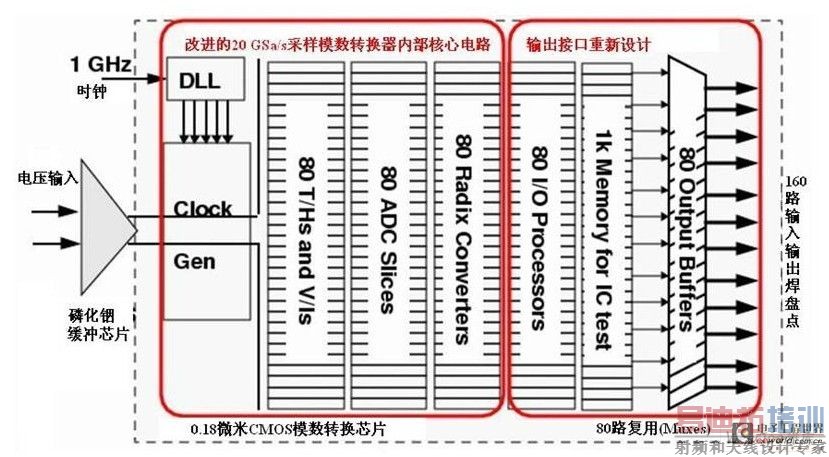

我们来剖析一下图1所示的四个模数转换器的内部机构原理,如图2所示,实际的电路封装里面有两个片子,一个片子是磷化铟缓冲芯片,功耗是1瓦,另一个是CMOS模数转换器芯片,功耗是9瓦。模数转换器结构是由安捷伦中央实验室研发的, 0.18 u CMOS工艺,内部有5000万个晶体管,采用顺序延迟采样原理设计,所谓顺序延迟采样是将模数转换器内部细分为80个slices,每个以250 MSa/s速率运作,一次一个 digit 。这里我们用的术语是 “digit”不是“bit”,这是因为转换基数是1.6 不是 2,所以在每个Slice中有12个基数是1.6的数值顺序产生,然后将它们映射成8-bit 二进制值,并传送到输出接口处,也就是80 路串行数据链路处,每个链路的串行数据速率是 2 Gb/s,总的速率就是160 Gb/s ,即 20 GB/s 总的数据速率。 被测信号从示波器输入端经过磷化铟前置电路模块的前置放大器、触发芯片,最后从该模块中的Sampler芯片中输出,信号经由磷化铟缓冲晶片(如图3所示),再直接驱动模数转换器的输入电容,模数转换器的80个Slices,每一个Slice由几部分组成,包括输入跟踪和保持(图2中的T/H)、将电压转换成电流的跨导(transconductor,图2中的V/I),顺序延迟采样模数转换器(基数改良的电流模式)和基数转换器(Radixconverter)。1GHz时钟驱动一个延迟锁相回路、内插器、分频器以生成80路250MHz的时钟,相邻250MHz时钟间的延迟是50ps,延迟锁相回路产生5个差分时钟相位,内插器用来产生20个单端相位。

图2 磷化铟示波器内部每个20GSa/s的结构原理图,除CMOS模数转换芯片外,里面还有一个缓冲芯片

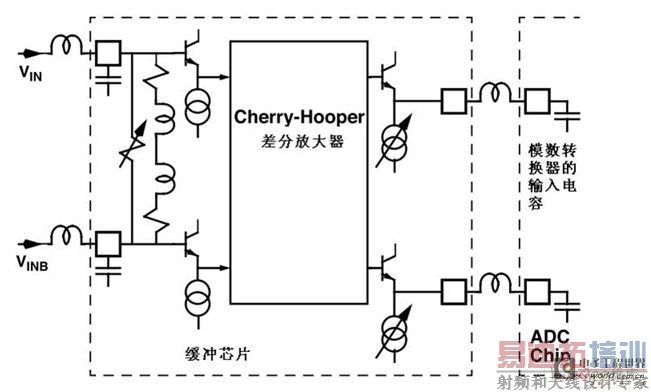

模数转换模块中的磷化铟缓冲芯片的主要作用是在驱动CMOS模数转换器的输入电容时,提供50欧姆匹配终端,缓冲芯片和CMOS模数转换器之间用键合线相连,这样做的关键好处是让增益响应在整个频率范围内保持平坦。 [p]

图3 简化了的磷化铟缓冲芯片电路原理图

图3是简化了的缓冲芯片电路原理图(本文所有原理图都是简化的),差分输入信号的终端电阻有固定电阻和可变电阻组合而成,可变电阻用的是工作在线性区的FET管,其寄生参数效应,被考虑进L-C-L传输线设计中,传输线包括键合线、焊盘、晶体管输入电容和片上电感。

在CMOS模数转换芯片中,80路跟踪/保持电路直接和输入焊盘相连,每个差分跟踪/保持电路是一对NMOS FET pass-gate门电路,后面连接的是驱动电路模式顺序延迟模数转换的跨导多级电路。每个顺序延迟模数转换器,使用基数是1.6的12级跨导以改进对失配误差的容忍度,基数转换器会把12位的基数是1.6数据转换成2进制数据,基数转换器中系数寄存器由校准软件程控,以纠正顺序延迟电路中每一级的误差。

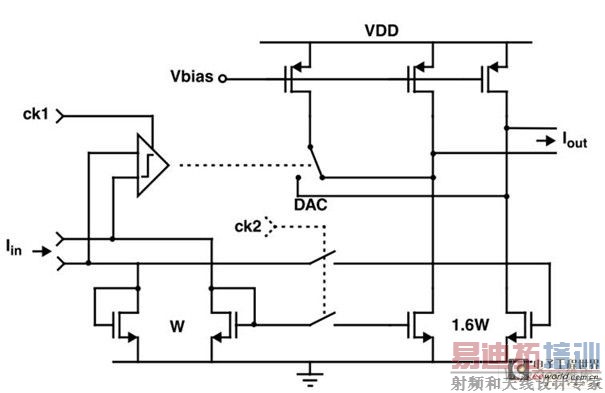

图4 顺序延迟采样模数转换12级电路中的一级

图4是12级跨导电路的其中一级的简化原理图,输入电流进入一对镜像1.6x电流电路,比较器感知输入信号极性并致使一位(1b)DAC电流从输出电流中被加上或减去。这种顺序延迟电路设计有3个优点:

1. 低功耗:每个Slice是57mW,包括跨导、基数转换器

2. 面积小:每个Slice占用0.12mm

3. CMOS兼容:不需要线性电阻或电容来维持并行结构

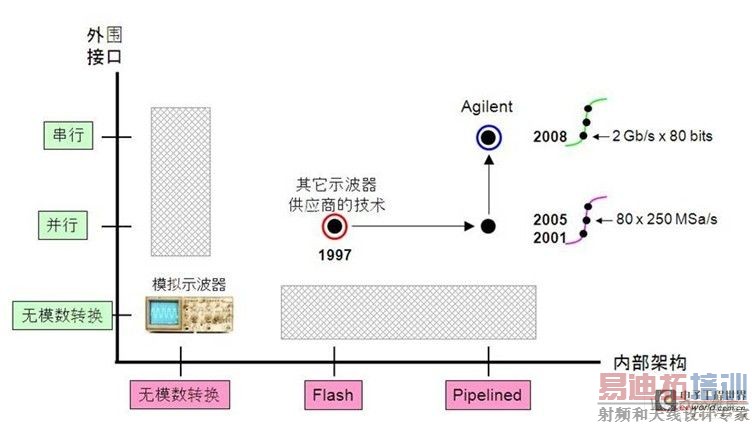

图5给出示波器中使用的模数转换器内部架构发展历史,今天所有示波器厂家采用的模数转换器技术都是基于flash转换,并行输出的技术。如图中红色圆圈所示,安捷伦最后一波使用该技术在当时的高性能示波器上是在1997年,首次采用顺序延迟采样模数转换器是2001年,那时的模数转换器是4GSa/s,内部有32个slices ,每个Slice的采样率是125 MSa/s ,把该 转换器也用到了低端的产品中。到了2005年,安捷伦推出20GSa/s的模数转换器,内部有80个slices ,每个Slice的采样率是250 MSa/s 。2008年,安捷伦重新设计了该模数转换器的外部接口,让其输出80路串行信号,每一路是2 Gb/s。2010年推出的磷化铟示波器,将采样头从剥离出来单独设计并和前置放大器等芯片一起封装到一个三维电路模块中。

图5 示波器中的模数转换器内部架构的发展历史

这里,我想说的其实不是安捷伦科技的模数转换器技术发展曲线,而是强调安捷伦的模数转换器技术采用了完全不同的思路,供国内相关的研发工作者借鉴。实际上,安捷伦科技的模数转换器在Slices这个级别一点都不快,这也意味着,安捷伦可以做出更快的单晶片模数转换器,因为仍有空间增加内部Slices的数量,以及提高每个Slice的采样率,输出串行链路的数量,每个串行输出链路的速度;反过来说,也可以将每个Slice的采样率降低,采样率降低再配合其它技术,就有机会将模数转换器的垂直分辨率提高,比如从8位提高到10位甚至12位,技术和经验储备已经有了,何时推出,主要取决于市场需求和竞争态势。无论是提高模数转换器的垂直分辨率还是采样率,都有机会改变业界游戏规则,这正是安捷伦维持技术领先的策略重点所在。 [p]

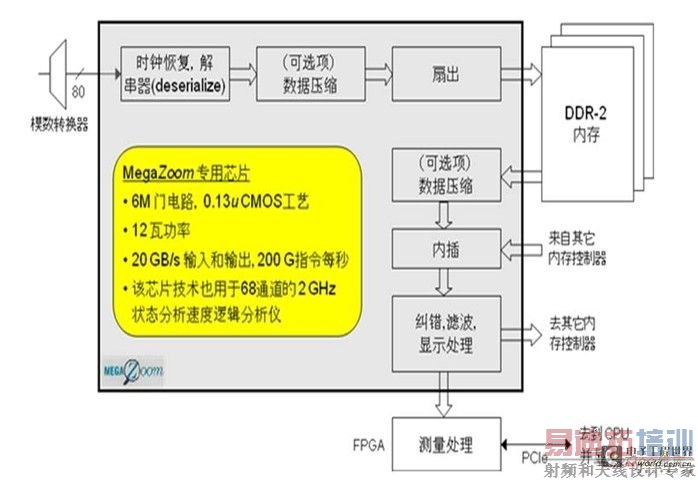

图6 模数转换器采集到数据后的后续数据硬件加速处理电路(MegaZoom芯片)

90000系列示波器的存储深度可以达到每通道2G点(其实可以到4G点),这样大的数据量,要保证仪器的响应速度很快,没有专门的硬件技术是很困难的。图6给出的是专门用来加速大数据量处理的 MegaZoom专用芯片,内部CMOS电路部分由6百万门电路组成,来自模数转换器的80路串行输出信号直接进入该内存控制器的并行内存系统,该专用芯片提供硬件加速支持对深存储数据的快速响应,也就是有名的MegaZoom 快响应深存储技术。在读操作中,每秒钟等效指令数达2000亿,远比一般示波器使用的通用CPU快,该专用芯片也用在安捷伦最快的逻辑分析仪上,同时,该技术稍加改动后也被用到低阶的产品中。

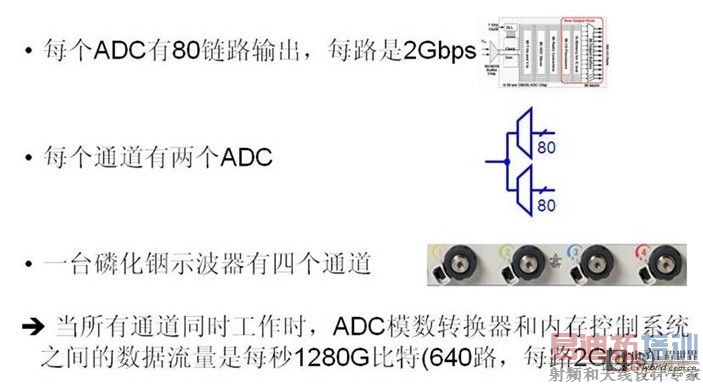

图7 当磷化铟示波器4个通道一起工作时,你每次按下“运行”按钮,每秒1280G比特的数据流就会被处理

我们来看一下示波器内部模数转换器和内存控制专用芯片的串行数据流量,如图7所示,每个模数转换器有80路串行链路输出,每路的速率是2 Gb/s,示波器每个通道后面有2个模数转换器,示波器共4个通道。这意味着当你每次按下示波器上的“Run”按钮时,每秒中的数据流量是1280Gbit(80 x 2 Gb/s x 2 x 4),该图也显示出在芯片中采用串行信号接口的威力,在测量仪器中,大量采样串行链路设计意味着仪器设计者非常熟悉串行设计可能面临的各种设计难题和挑战。

至此,我们通过6篇技术揭秘文章讲解了磷化铟示波器中采用的创新技术,大家可以猜想下一步, 根据安捷伦示波器部门总经理,Jay Alexander的说法,他只是根据已经制定好的策略执行而已,高端技术创新会往更高的实时带宽走,带宽超过32GHz后,模数转换技术会跟着有进一步的改进,同一时间,高端技术会逐步被用到低中端产品中。我们可以耐心等待下一个技术或产品的发布。