- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA控制VGA显示的多通道数字示波器的设计

随着信息技术的发展,对信号的测量技术要求越来越高,示波器的使用越来越广泛。模拟示波器使用前需要进行校正,使用比较麻烦,而数字示波器,由于受核心控制芯片的影响,对输入信号的频率有严格的限制,于FPGA的数字示波器,其核心芯片可达到50万门,配合高速外围电路,可以测量频率为1 MHz的信号,有效地克服了以往示波器的不足。

1 系统方案设计

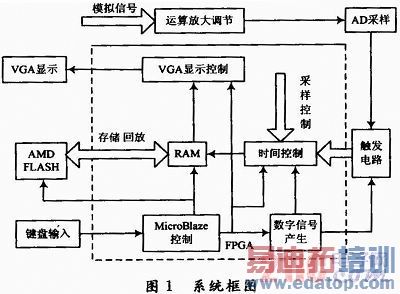

设计的数字示波器系统主要使用了Xilinx系统的开发环境,并在此环境内部建立了AD采样控制模块、键盘控制模块、VGA显示模块等多个模块,从很大程度上减少了硬件电路的搭建,也因此提高了系统的稳定性和可靠性,系统框图如图1所示。

另外,设计使用XPS将32位的MicroBlaze微处理器嵌入到了FPGA中,实现了可编程片的嵌入以及在可编程片上的系统设计。MieroBlaze通过LBM总线访问片上的存储模块BlockRAM,然后通过OPB总线上挂接外设进行接口连接和驱动。

VGA显示部分采用双缓冲机制进行工作,在FPGA内部建立RAM,按照一定时序降RAM内的缓存数据映射到VGA显示屏上。

2 硬件设计

2.1 信号调理电路模块

信号调理电路模块,对输入的模拟信号进行处理,由于输入电压幅度为-2.5~+2.5 V之间,而后一级的AD模块采用了12位的高速A/D转换芯片ADS804,只能对0~2 V的电压进行模/数转换,故需要将输入电压先抬升为0~5 V,在应用运算放大器进行比例缩小,达到0~2 V的模数转换要求。

2.2 A/D转换电路

A/D转换模块采用存储采样数据的并行数据处理方法,这样可以使硬件电路得到最大程度的简化,同时也提高了系统的稳定性。AD部分的采样,选用实时采样技术。能够捕获到单个信号。采样速率为10 MHz,即在最高频率1 MHz时,实时采样可以在每周期采10个点以保证取到一个完整的信号波形。

2.3 触发电路模块

触发电路模块属于外触发,对模拟信号实现任意电平触发,该模块采用电压比较器来实现单次触发。

2.4 存储模块

存储模块包括内存储和外存储两部分,使用外部电路进行搭建的为外存储,内存储在软件部分进行说明。

外部非易失性存储器模块采用存储容量为16 KB的E2PROM芯片24C128,该芯片作为手动存储的存储介质,从而实现掉电不丢失的设计目的。

2.5 VGA显示模块

VGA显示模块是建于FPGA内的双缓冲机制,由嵌入的MicroBlaze软核进行控制,能够进行多个页面间的切换。另外,每个界面,可以实现中文信息、彩色通道和所测输入波形的显示,并可控制显示内容的显示颜色。

2.6 键盘模块

4×4矩阵键盘模块实现人机交互。

通过键盘,可以对示波器的数字通道、模拟通道、混合通道、存储、回放、波形左移、波形右移等功能进行选择。

3 基于FPGA的软件设计

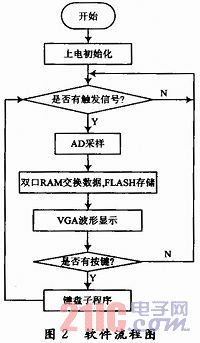

FPGA的硬件主要包括:触发电路模块、数字信号发生模块、存储模块、键盘模块、VGA显示模块等5个部分,软件流程图如图2所示。

3.1 触发电路程序

AD采样启动后,将从AD进来的数据与触发字进行比较,当满足设定条件时,会产生触发信号,此信号送到RAM控制器端。通过对外部触发电路发出触发信号与内部的两路数字信号进行触发的选择后,RAM控制器得到触发后将采样数据写入到RAM中。当RAM在进行写数据过程中触发信号是被抑制的,当RAM达到预触发深度时,释放触发信号,等待下一次触发的到来。

3.2 数竽信号发生程序

利用DDS的原理,在FPGA内部生成一个信号发生器。主要包括频率控制寄存器、高速相位累加器和比较器3部分。具体做法为:使用一个表示信号平均值的数据与AD采样得来的数据进行比较得到同频同相的A路信号,再经由A信号触发计数器,经过合理设置计数脉冲,得到有45°延时,占空比25%的B路信号。最后对该相位值计算数字化正弦波幅度输出。

表示信号平均值的数据由MicroBlaze测量信号提供。

3.3 存储程序

存储模块分RAM存储和FLASH存储RAM存储使用一个双口RAM,写和读分开,波形数据满足触发条件时送进RAM,存储了1 024个点,其中前560组送住VGA显示。

FLASH存储完成掉电不丢失的存储目的。20世纪使用开发板上的一块型号为AM29LV160DB的FLASH存储器,当按下存储健后,FLASH把RAM中的数据写到FLASH中,根据资料中的读写时序图,使用状态机实现这个过程,当按下回显的按键时将FLASH中的数据读回图像显示RAM,再显示出来。

3.4 键盘程序

键盘采用4×4矩阵键盘,使用FPGA进行扫描控制,实现人机交互。

键盘子程序主要包括数字通道、模拟通道、混合通道、存储、回放、波形左移、波形右移、垂直灵敏度档位设置,扫描速度档位设置等功能与按键的对应。

3.4.1 显示分辨率分析

垂直方向划分为10 div,设置3档垂直灵敏度:1 000 mV/div,100 mV/div和10 V/div,即每div可代表1 000 mV,100 mV和10 mV。

A/D转换模块的模拟信号输入端的输入信号电压为0~2 V,当示波器满刻度显示时,被测信号的幅度将分别为:V11=1 V/div×10 div=10 V,V12=0.1 V/div×10 div=1 V,V13=10 mv/div×10 div=100 mV。A/D转换器的满刻度输入值为Vmax=2 V,程控放大器电路的增益AN=Vmax/VIn,其中N=1,2,3,对应于3档不同垂直灵敏度的增益分别为:A1=2/10=0.2,A2=2/1=2,A3=2/0.1=20。

A/D转换器的满刻度输入值为Vmax=5 V<10 V,将AD采样的值和数字信号的值据当前档位进行计数存储,即1μs/div时每10个点保存一个,1 ms,/div时每10 000个点保存一个,1 s/div时每采样10 000 000个点保存一个。

3.4.2 扫描速率分析

A/D的转换速率取决于被测信号的频率范围,或DSO对扫描速度的要求,设计扫描速度含1 ms/div,1μs,/div,1 s/div三档,通过FPGA内部建立分频电路实现了最高采样率16 MS/s,每10倍频步进,共六档,增加了该示波器的实用性。水平显示分辨率为64点/div,以保证显示波形清晰稳定。

3.5 VGA显示部分

VGA显示模块使用双缓冲机制,软核MicroBlaze通过读写显存来控制VGA显示。VGA显示可显示3种颜色,利用了SOPC的优势。GRAM位宽32b,大大提高了FPGA刷屏的速度。vga_dn与GRAM对内嵌的MCU设计成为BlackBox,MCU只需向相应地址发送合适数据即可显示想要的波形。本设计主要实现了的显示为:底色,汉字,示波器的显示框,波形数据。通过取字摸的方式,可在显示屏上显示中文信息。当部分的数据进行综合时,这几部分的数据各自有不同的优先级,当多部分重叠时,根据优先级显示出来。

4 总体效果

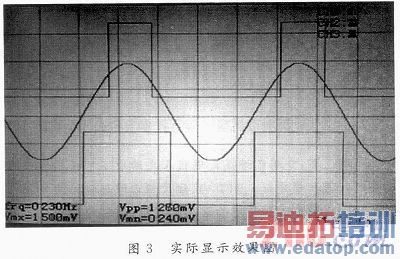

图3为同时显示2个数字通道和1个模拟通道的界面,通道1(CH1)为模拟通道,通道2(CH2)和通道3(CH3)为数字通道,输入信号为一正弦波,峰一峰值为1.2 V,通道2,设定输入信号信号电压大于0为高电平,反之为低电平,故通道2为占空比为50%的矩形波。通道3设定输入信号大于3.3 V为高电平,反之为低电平,故在本图上通道3为占空比约为25%的矩形波。由图可知观察值与计算值相符。

5 结语

设计实现了一款基于FPGA的VGA显示的多通道数字存储示波器。FPGA的高速性比其他控制芯片更适合于高速数据的采集和处理,另外FPGA内部存储模块在完成输入信号的量化存储速度上有着外接RAM无法比拟的优势。通过测试,设计系统比较好地完成了各项设计要求。

上一篇:内置波形发生器的示波器进行元器件测试

下一篇:高性能示波器应对光通信测试