- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

FPGA的通信系统基带验证平台的设计

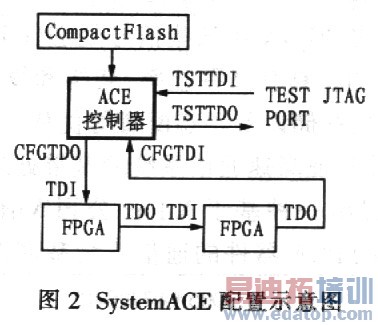

本设计采用JTAG/Boundary Scan配置模式,主要通过四个专用配置信号线完成所有配置任务。提供两种配置方式,一是在线下载配置,通过下载电缆将FPGA的JTAG口与计算机并口相连,使用软件完成在线下载。另一种是采用SystemACE方案,上电后,通过SystemACE控制器读取CF存储器中的配置文件,通过JTAG配置相连的FPGA器件。

SystemACE CompactFlash(CF)使用基于CFACompactFlash标准的存储器,由CompactFlash存储模块和ACE控制器组成。ACE控制器具有内置的控制逻辑,可以通过任何一个ACE控制器接口(CompactFlash接口、CFGJTAG接口、TESTJTAG接口和系统微处理器接口)对目标FPGA链进行配置。其中CompactFlash接口提供对CompactFlash存储卡的支持。单片Virtex-ⅡFPGA所需的配置数据大小为300 Kbit-29.O Mbit,这意味着使用一个Svs-temACE CF方案可以配置超过250片最大容量的Virtex-Ⅱ系列FPGA。设计者可以根据需要灵活地改变ACE Flash的密度。

SystemACE配置示意图如图2所示。完成FP-GA设计后,通过软件生成所设计的下载配置文件,通过CF卡读写器将文件置于CF存储卡中。当平台上电后,ACE控制器读取CF卡中的配置文件,通过JTAG链将数据下载到各FPGA,完成自动配置。也可以通过JTAG下载电缆连接TEST JTAG接口,直接对FPGA进行在线配置。

3.2 时钟电路和复位及电压监视电路

本平台采用两个相互独立的有源晶体振荡器提供20 MHz时钟,分别作为接收机和发射机的时钟源。由于板上多处地方需要20 MHz时钟(如ADC和DAC),而仅靠晶体振荡器供给时钟除导致驱动力较弱外,还可能会产生较大时钟偏移或抖动。选用时钟驱动器IDT74FCT38074为系统提供时钟,这是一款3.3 V供电,CMOS工艺的1驱4时钟驱动器,输入时钟最高为166 MHz,同时提供4路低偏移同相时钟。通过两片IDT74FCT38074,分别为接收机和发射机各个模块提供精确时钟。输入时钟进入FPGA后又可以通过DCM的分频倍频处理,为FP-GA内部各个功能模块提供所需的时钟。

作者:沈梁 蒋一琦 来源:国外电子元器件

上一篇:微波通信新发展与通用发射机技术研究

下一篇:微波通信与应用