- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

ADS PLL相位噪声仿真模型中计算问题

录入:edatop.com 点击:

各位大神好,仿真遇到一棘手问题,希望各位大神百忙之中能够帮忙指导一下!

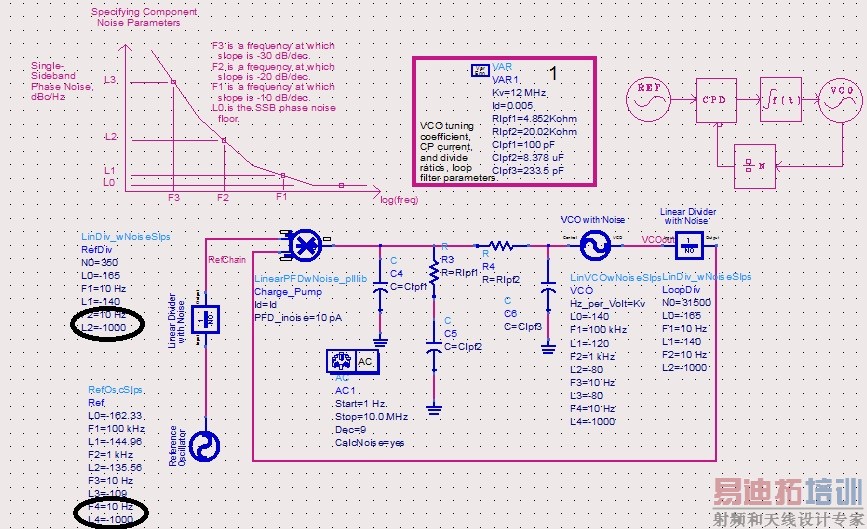

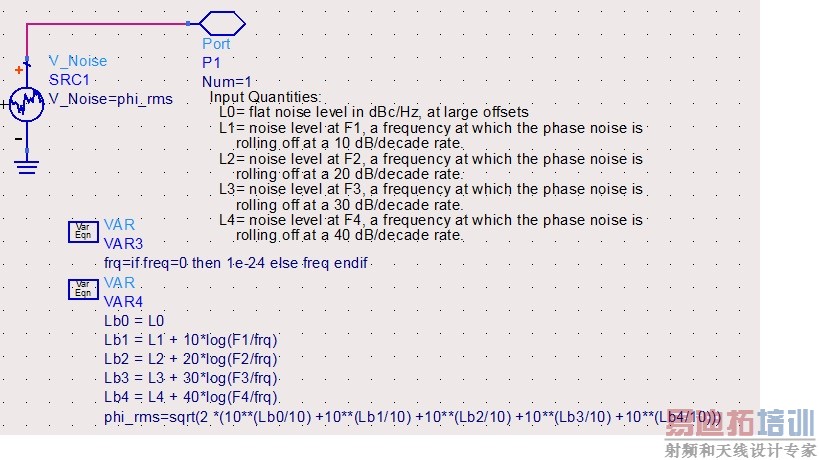

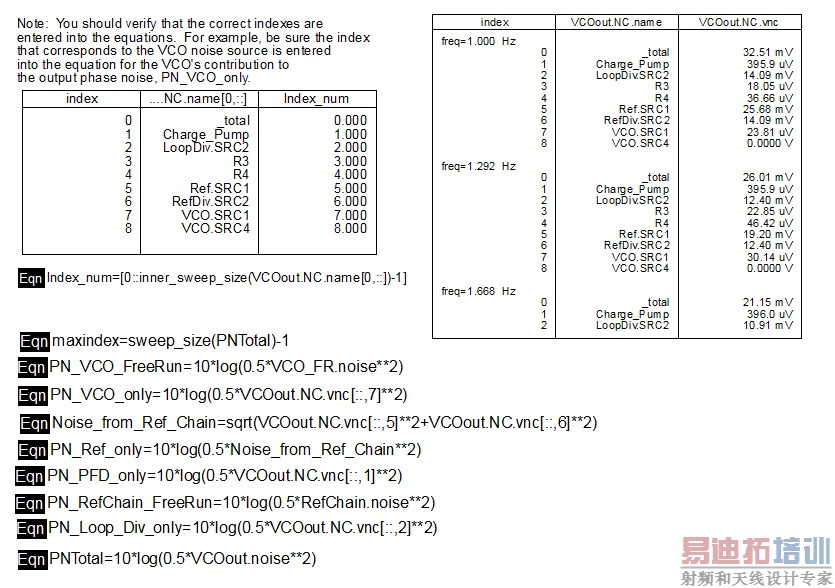

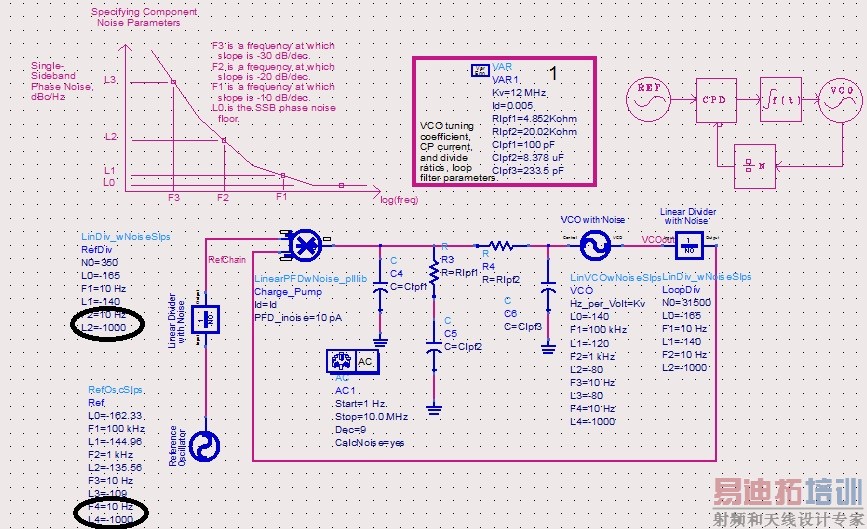

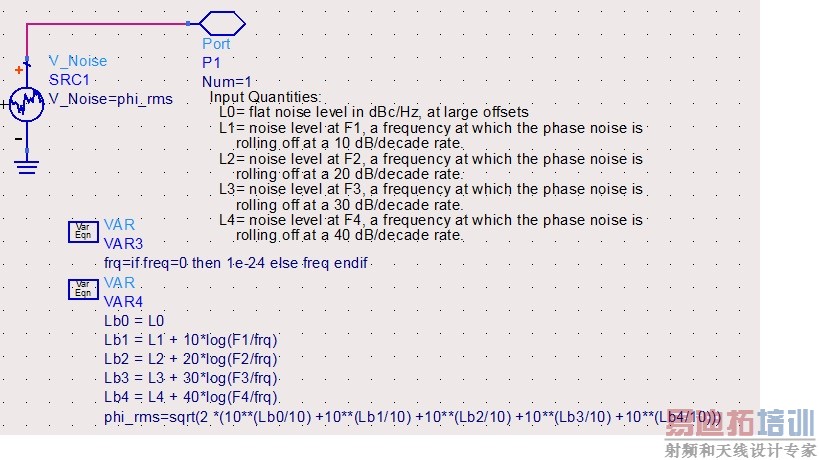

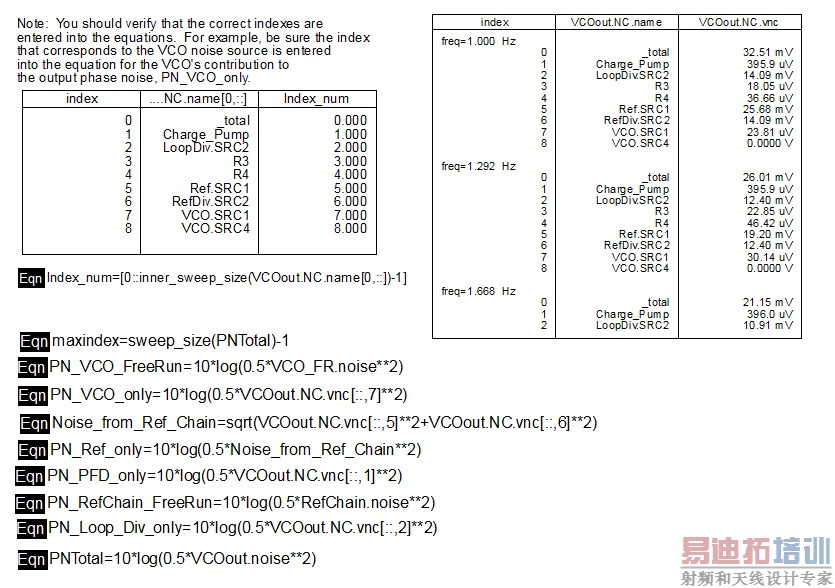

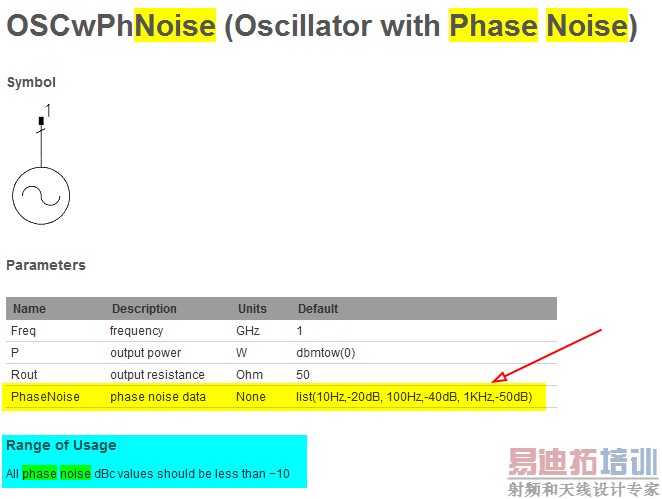

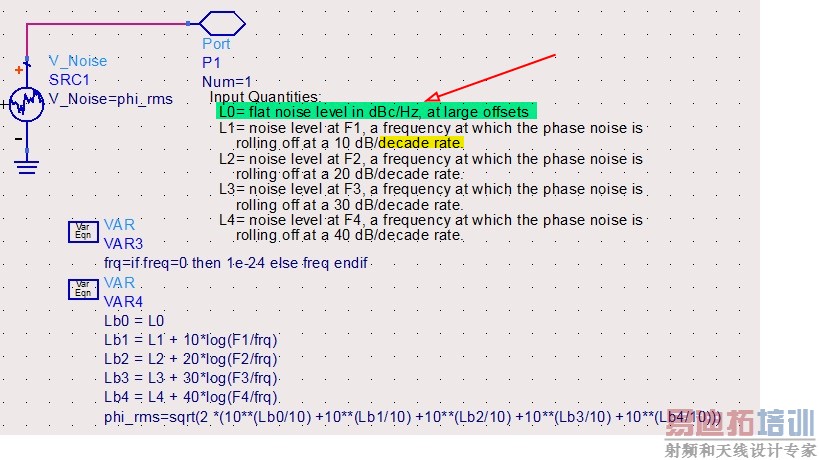

问题如下:图1的仿真模型中给定了F和L的定义,但不明白为什么L4和L3值相同?F4又为什么要设置为-1000?查了help无详细解释,相关仿真教程中也未做特别说明。还有图2和图3中的计算公式,看不太懂,那位大神清楚,能否说明一下?

在线等先谢谢大家啦!

图1频综系统的相噪仿真模型

图2参考信号源PushIntoHierarchy后的内部模型和计算公式

图3 仿真结果第二页给出的计算公式

问题如下:图1的仿真模型中给定了F和L的定义,但不明白为什么L4和L3值相同?F4又为什么要设置为-1000?查了help无详细解释,相关仿真教程中也未做特别说明。还有图2和图3中的计算公式,看不太懂,那位大神清楚,能否说明一下?

在线等先谢谢大家啦!

图1频综系统的相噪仿真模型

图2参考信号源PushIntoHierarchy后的内部模型和计算公式

图3 仿真结果第二页给出的计算公式

第一个问题描述错了,重新阐述:对于每一个器件,为什么最后一个L和倒数第二个L的值都要为10Hz,且最后一个L对应的F=-1000?

先声明: 我只负责破题、解题是出题者的责任。

Phase Noise 的表示法是:-xx(十进位制) dBc/Hz,那个c 意思是相对。其实你要知道的亊情都在你的贴图中已经说完了!

发现什么了? 相对频率越小、-dB値就越大! 再看一次你自己的贴图...

L=-1000 按你贴图中的说明调整一下,成为40dB/-1000 -> -40dBc/1000Hz -> 十进制一下=> -40dBc / KHZ (offset)

** 由此反推当offset = 100Hz时 -30dBc/100Hz 会比-40dBc / KHZ 大,也就不足为奇了。发现第一张图的重点了吗?

这就是我说的: 形不是重点、意才能区分高下。

申明:网友回复良莠不齐,仅供参考。如需专业帮助,请学习易迪拓培训专家讲授的ADS视频培训课程。

上一篇:求助ADS2011.05原理图设计显示不正确

下一篇:求ADS软件包

ADS培训课程推荐详情>>

国内最全面、最专业的Agilent ADS培训课程,可以帮助您从零开始,全面系统学习ADS设计应用【More..】

国内最全面、最专业的Agilent ADS培训课程,可以帮助您从零开始,全面系统学习ADS设计应用【More..】

- Agilent ADS教学培训课程套装

- 两周学会ADS2011、ADS2013视频教程

- ADS2012、ADS2013射频电路设计详解

- ADS高低阻抗线微带滤波器设计培训教程

- ADS混频器仿真分析实例视频培训课程

- ADS Momentum电磁仿真设计视频课程

- ADS射频电路与通信系统设计高级培训

- ADS Layout和电磁仿真设计培训视频

- ADS Workspace and Simulators Training Course

- ADS Circuit Simulation Training Course

- ADS Layout and EM Simulation Training Course

- Agilent ADS 内部原版培训教材合集