- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速PCB设计仿真讲座十三

2.2.5 使用SI Audit 进行核查

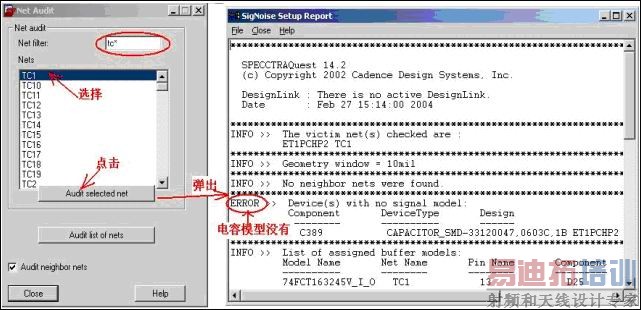

在Database Setup Advisor-SI Models窗口中点击 “Next” 按钮, 将进入Database Setup Advisor-SI Audit窗口,点击该窗口的中央的“SI Audit”按钮, Net Audit 窗口就会弹出,该窗口主要的功能就是检查要仿真的网络设置情况,相应网络的器件模型是否赋全,叠层设置的参数信息等等。假设需要对 TC总线有仿真要求,我们对TC*信号检查一下,在网络过滤器中输入TC*,按键盘Tab 键,选择TC1 网络并点击Audit selected Net按钮,弹出的窗口如下:

图 2-21 Net Audit 图解说明窗口

对于缺少模型的元件,需要返回上一步骤赋模型的窗口中进行添加,如果没有错误就可以关闭 Net Audit 窗口了,在Database Setup Advisor-SI Audit窗口中点击“Finish”按钮结束仿真设置向导。

2.3 设置 IO管脚的测试条件和逻辑门限值

在给器件赋好模型后,我们还有一个需要经常修改的地方,就是模型参数中的测试条件,这是因为同一器件的不同功能的 IO管脚可能使用的是同一个 IOCell模型,厂家在测试这些管脚的功能参数时可能使用了不同的测试条件,因此我们在对不同的管脚所在的网络进行仿真时,必须根据该管脚实际测试条件进行设置。

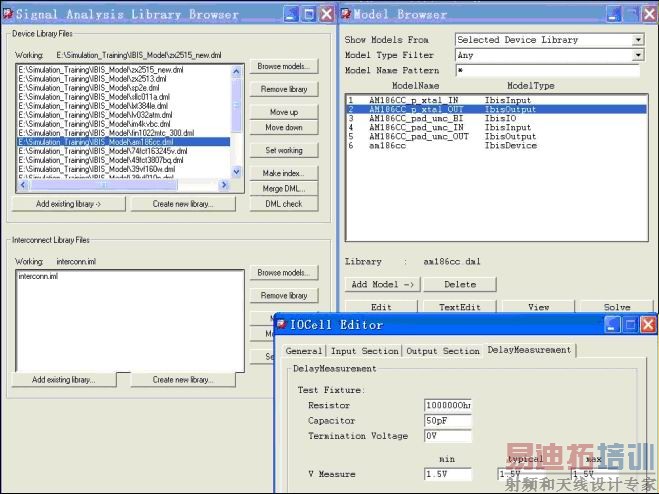

执行 Analyze ->SI/EMI Sim ->Library…启动 Signal Analysis Library Browser 界面,选中你所需设置的器件,再启动 Model Browser界面。选中所需管脚,点击 Editor,启动 IOCell Editor界面,如图 2-29 所示。其中有四个标签,我们会经常修改的是 Delaymeasurement标签,该标签的内容必须根据DATASHEET的数据进行填写。

因为现在公司有统一的 IBIS模型库,DATASHEET有这些参数的已加上了,但往往有些粗糙的DATASHEET没有给出这些参数,此时使用该器件的设计人员必须向厂家咨询获得该参数,否则仿真将无法进行。

图 2-22 修改 IO管脚的测试条件

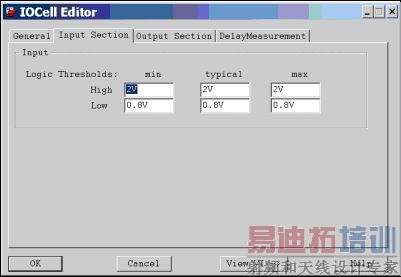

另外,除了 DelayMeasurement标签需要设置外,通常还需要设置输入缓冲器模型 Input Section标签中Logic Thresholds 的 High和 low值,如图 2-23 所示。

2.4 差分驱动器的设置

当仿真差分线时,可以将差分线一起提取拓朴,这就要将两个驱动器一起提取 IO模型,这需要在模型中作些修改:

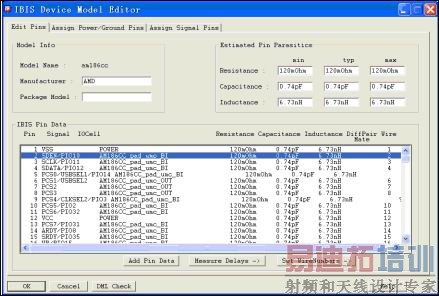

执行 Analyze ->SI/EMI Sim ->Model,启动 Signal Model Assignment界面,如图 2-24 所示。选中你所需设置的器件,再启动 IBIS Device Model Editor 界面。点击需要设置成差分对的一个管脚,将自动弹出IBIS Device Pin Data 界面,如图 2-25 所示。对于差分对,在 Diff Pair Date 下面,选择 Type类型,如反向还是不反向,然后在 Mate Pin中填入耦合管脚,如 3,图 2-26 所示,这样就将2 和3 两个管脚组成了一对,提取拓朴时会一起提出。

图 2-24 Signal Model Assignment 界面

图 2-25 IBIS Device Model Editor界面

图 2-26 IBIS Device Pin Data 界面

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:LTE多模多频段选择对终端产品的挑战一

下一篇:多层电路板设计EMI抑制技巧一