- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PCB高速信号阻抗简析

录入:edatop.com 点击:

高速信号一般为差分对,它们需要明确的、恒定的差分和单端阻抗。差分对应该是边缘耦合,意思就是差分对的两根线在同一层且线间的间隔是固定的。并不推荐层间耦合(意思是差分对的两个线分布在不同层上)。

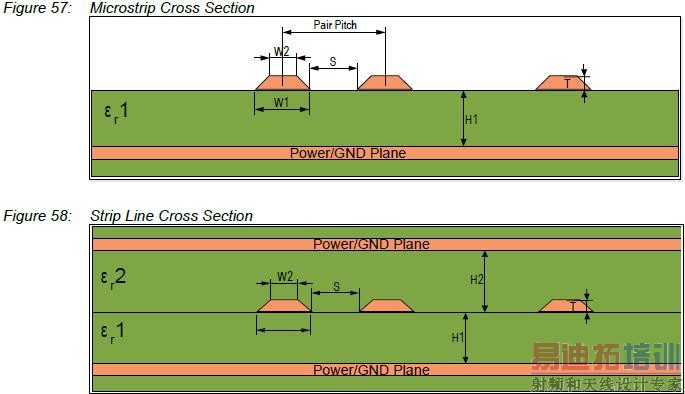

走线有两个基本的结构:一个是“Microstrip”,线的参考是单一的地平面或电源平面。多层板的上下外层就是“Microstrip”结构。

还有一种结构叫“Stripline”线被夹在两个参考平面之间,如果线与两个参考平面严格对称,我们称为对称或平衡;通常内层走线是不对称的。

参数:

符号 | 定义 |

Er1 | 走线层与参考层之间的固有介质常数。增加Er1, 阻抗降低. |

Er2 | 走线层与第二参考层之间的固有介质常数。Er2与Er1一样,增加Er2, 阻抗降低 |

H1 | 较低层的走线与最近的参考层之间的距离。增加H1, 阻抗也增加。假设H1小于H2 |

H2 | 较低层的走线与较远的参考层之间的距离。通常H2比H1大得多,如果这一条件成立,图中的较低平面是主参考层,增加H2可以增加走线阻抗。 |

PairPitch | 差分对之间的间隔,这个间隔是S和W1的和,增加S+W1,阻抗会增加。 |

S | 增加线的间距,阻抗增加。 |

T | 厚度增加, 阻抗降低 |

W1,W2 | 线宽增加,阻抗降低 |

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PCB抗电磁干扰设计

下一篇:PCB画板裸露焊盘的作用

射频和天线工程师培训课程详情>>