- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

阻抗偏离到60~65欧姆有什么危害(下)

录入:edatop.com 点击:

记得刚接触信号完整性分析的时候,读的最多的就是Eric Bogatin著的《Signal Integrity:Simplified》,中文译作《信号完整性分析》,书中将所有信号完整性噪声问题归结为四个方面,分别是:单一网络的信号完整性;两个或多个网络间的串扰;电源和地分配中的轨道塌陷;来自整个系统的电磁干扰和辐射。当然,信号完整性涉及到的问题应该不止这些,但是这四个方面为我们的信号完整性分析提供了很好的思路,一般如果信号质量出现了问题,我们一般都会从这四个方面寻找原因。

高速先生上篇文章中提到,导致阻抗偏高的一个主要原因就是不能使用比较薄的芯板,这样会导致信号离参考层的距离较远。这种情况除了会使信号的反射严重,对于串扰又有什么影响呢?还是来验证一下。

3、从串扰角度分析

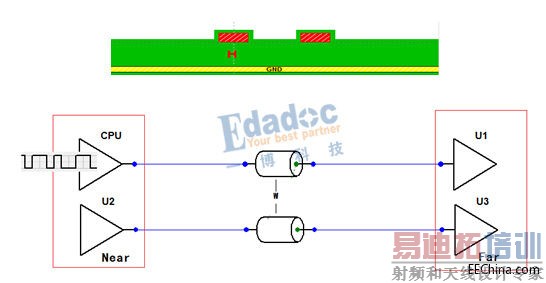

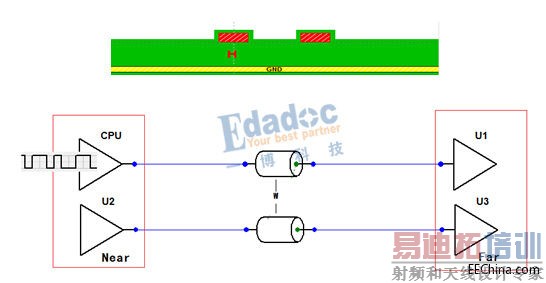

我们假设有两根线,两线线宽及线间距不变。只是改变信号线到参考层距离,使单根线阻抗分别达到40,50,60,65欧姆,看看信号的串扰波形有什么变化。仿真示意如下图1:

图1

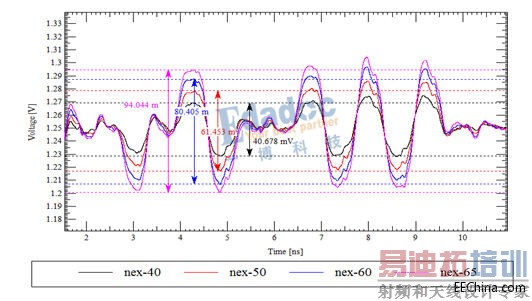

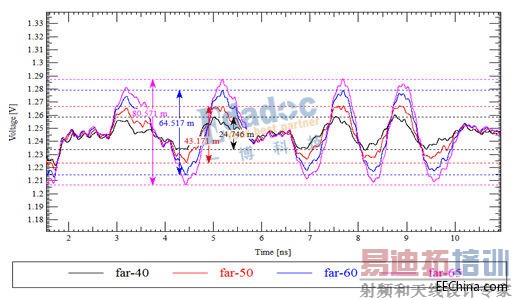

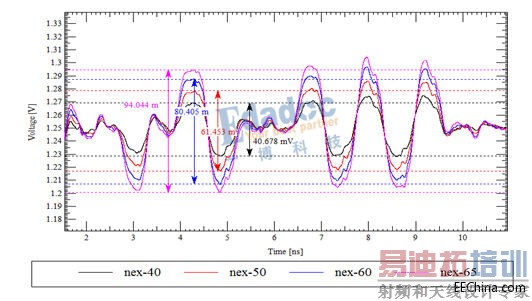

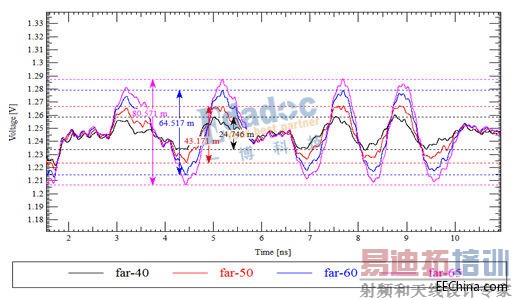

改变信号层到参考层距离,得到近端串扰(图2)与远端串扰(图3)波形如下:

图 2

图3

由上图可知,这种信号线到参考层之间距离增大导致的阻抗偏高,对串扰是不利的,阻抗越高,串扰越厉害。为什么会这样呢?我们还是回到串扰产生的原因,一般认为线间距变小会使串扰加剧。因为线间距变小之后攻击线和受害线之间的耦合作用更明显了,如图4所示。

图4

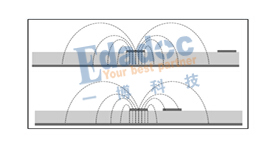

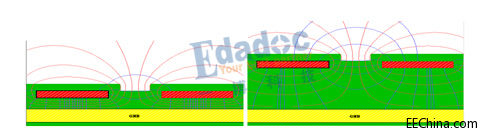

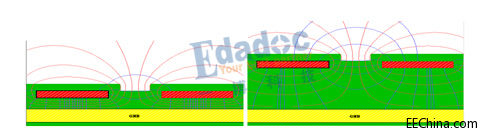

信号到参考层之间的距离也会影响信号间的电磁场分布,如下图5所示,如果信号到参考层之间的距离很近,信号电场主要分布在信号与地之间,当信号到地之间的距离变远之后,电场会更多的耦合到旁边的信号线,这样就会造成串扰加剧。

图5

总结:

文章终于结束了,不知道各位网友还记得文章的前两部分内容吗?我们来总结一下:当通道有端接电阻,上拉电阻或者芯片有ODT的情况下,线路阻抗从40~65欧姆不会导致太大的过冲,如果没有这些端接措施,线路阻抗越高,过冲越大。作者认为反射较厉害的原因是传输线阻抗与芯片的输出阻抗不匹配,如果是接口信号,如网口,USB等,或者是背板——子板这样的互连结构,阻抗失配也都会增加反射。同时,在本文设定的条件下,信号到参考层距离变远导致的阻抗升高,会对串扰产生不利影响,阻抗越高,串扰越大。

综上所述:不是任何情况下都可以采用高阻抗方案,除非您的信号通道有良好的端接措施且对串扰以及损耗等要求不是很严格,通常情况下,我们还是好好遵守芯片的阻抗控制规则吧。

这篇文章对解答您的疑问有帮助吗?群殴阻抗,阻抗群殴,我们的下一篇文章将带给您更多的精彩!

高速先生上篇文章中提到,导致阻抗偏高的一个主要原因就是不能使用比较薄的芯板,这样会导致信号离参考层的距离较远。这种情况除了会使信号的反射严重,对于串扰又有什么影响呢?还是来验证一下。

3、从串扰角度分析

我们假设有两根线,两线线宽及线间距不变。只是改变信号线到参考层距离,使单根线阻抗分别达到40,50,60,65欧姆,看看信号的串扰波形有什么变化。仿真示意如下图1:

图1

改变信号层到参考层距离,得到近端串扰(图2)与远端串扰(图3)波形如下:

图 2

图3

由上图可知,这种信号线到参考层之间距离增大导致的阻抗偏高,对串扰是不利的,阻抗越高,串扰越厉害。为什么会这样呢?我们还是回到串扰产生的原因,一般认为线间距变小会使串扰加剧。因为线间距变小之后攻击线和受害线之间的耦合作用更明显了,如图4所示。

图4

信号到参考层之间的距离也会影响信号间的电磁场分布,如下图5所示,如果信号到参考层之间的距离很近,信号电场主要分布在信号与地之间,当信号到地之间的距离变远之后,电场会更多的耦合到旁边的信号线,这样就会造成串扰加剧。

图5

总结:

文章终于结束了,不知道各位网友还记得文章的前两部分内容吗?我们来总结一下:当通道有端接电阻,上拉电阻或者芯片有ODT的情况下,线路阻抗从40~65欧姆不会导致太大的过冲,如果没有这些端接措施,线路阻抗越高,过冲越大。作者认为反射较厉害的原因是传输线阻抗与芯片的输出阻抗不匹配,如果是接口信号,如网口,USB等,或者是背板——子板这样的互连结构,阻抗失配也都会增加反射。同时,在本文设定的条件下,信号到参考层距离变远导致的阻抗升高,会对串扰产生不利影响,阻抗越高,串扰越大。

综上所述:不是任何情况下都可以采用高阻抗方案,除非您的信号通道有良好的端接措施且对串扰以及损耗等要求不是很严格,通常情况下,我们还是好好遵守芯片的阻抗控制规则吧。

这篇文章对解答您的疑问有帮助吗?群殴阻抗,阻抗群殴,我们的下一篇文章将带给您更多的精彩!

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>