- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于ATmega128单片机的压电式贾卡控制系统设计

0 引 言

贾卡经编机贾卡装置自1884年问世以来,已从机械式发展到电磁式和现在的压电式,即Piezo贾卡系统,彻底改变了贾卡装置需要通丝、移位针等繁杂部件的特点,使贾卡经编机提花部分的机构大大简化,速度有了很大提高。此外,与计算机辅助花型设计系统配合,加快了贾卡经编织物的设计,简化了上机工艺,缩短了产品更新周期。Piezo贾卡的成功开发促进了经编机设备的不断发展进步,目前机器速度已经大大提高,提花原理也得到了进一步的发展。

Piezo贾卡导纱针主要由三部分组成:压电陶瓷、导纱针握持端和可替换的贾卡导纱针。Piezo贾卡元件用于控制经编机上贾卡导纱针的左右偏移。它由两片压电陶瓷组成,中间由玻璃纤维层隔离(绝缘)。压电陶瓷具有“逆压电效应”,将其置于外电场将产生几何变形。通过控制贾卡元件两侧交替加上去的正负电压,使电陶瓷变形,进而使导纱针向左或向右偏移。由于压电陶瓷效果像电容一样,使得压电式导纱针能保持在它的偏移位置上。贾卡导纱针左右两面都有定位快,可以保证精确的隔离。

设计贾卡控制系统的主要目的就足要根据经编机的需求,把花型数据准确适时地执行到导纱针,实现经编机的提花。本文根据实际经编机设备的开发需求,选用AVR系列单片机ATmega128为主控芯片,设计了压电式贾卡控制系统,包括控制系统的软、硬件设计,压电陶瓷贾卡装置的驱动电路等。系统将计算机技术和传统的提花工艺结合,较好地解决了传统提花工艺中存在的问题,降低了成本,简化了操作过程,缩短了新产品的开发周期。该系统由于成本低,结构简单,特别适用于实际贾卡经编机设备控制部分的技术改进,具有较好的可靠性与实用性。本系统的设计原理和结构的可靠性与实用性已通过样机试运行得以证实。

1 硬件设计

1.1 系统总体结构

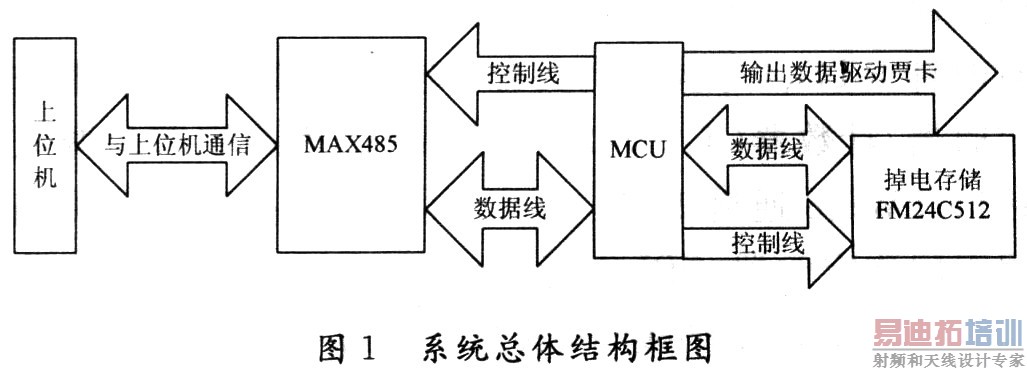

图1所示为系统总体结构框图。

图1中下位机在系统中所完成的主要工作包括:接收上位机的选针花型数据,并存储在下位机的存储器FM24C512中;接收上位机的同步和归零信号,并根据存储器中的选针花型数据驱动贾卡陶瓷导纱针,以实现提花控制。

1.2 单片机控制系统总体设计

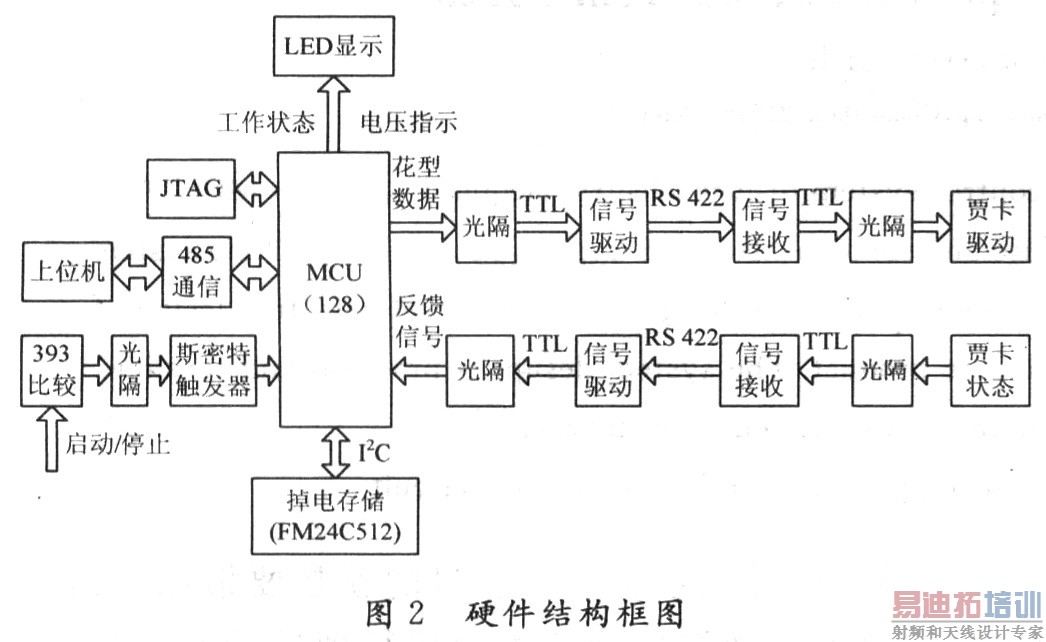

下位机系统硬件结构框图如图2所示。AT-mega128单片机作为系统控制核心,将花型准备系统设计出来的花型数据(花型数据库)通过RS 485连接单片机的串口通信,从上位机把花型数据传送到外部扩展的FM24C512存储器中,实现与上位机的高速多机通讯,并由ATmega128单片机按照花型数据,与机器设备其他部分协调控制(同步、归零等)贾卡经编机所需要的花型,通过贾卡驱动电路驱动贾卡陶瓷导纱针,以实现提花控制。

单片机采用MCU的联机仿真和测试的标准接口(JTAG),可实时在线仿真和调试,方便系统软件的维护和升级。系统工作的启动或停止信号经393比较电路、光电隔离电路和斯密特触发电路处理后安全可靠稳定地到达控制核心,两路信号接ATmega128两路外部中断接口,以保证信号的实时处理。

[p]

1.3 硬件各部分设计

1.3.1 MCU控制中心

本经编机贾卡控制系统采用美国ATMEL公司资源丰富的ATmega128产品作为主控芯片进行设计。ATmega128为基于AVR RISC结构的8位低功耗CMOS微处理器,具有快速、灵活、集成度高,加密性强和易实现等诸多优点。ATmega128具有128 KB的系统内可编程FLASH、4 KB的E2PROM、4 KB的SRAM、53个通用I/O口线、32个通用工作寄存器、实时时钟RTC、4个灵活的具有比较模式和PWM功能的定时器/计数器(T/C)、2个USART、面向字节的两线接口TWI、8通道10位ADC、具有片内振荡器的可编程看门狗定时器、SPI串行端口、与IEEE 1149.1规范兼容的JTAG测试接口,以及6种可以通过软件选择的省电模式。由于其先进的指令集以及单周期指令执行时间,ATmega128的数据吞吐率高1 MIPS/MHz,比普通的复杂指令集微处理器高10倍,从而可以缓减系统在功耗和处理速度之间的矛盾。

1.3.2 RS 485通信

在实际应用中采用一台主机控制多台从机。根据设备的基本要求,从机与主机间的通讯速度不需要太高,一般采用9 600 b/s或14 400 b/s即可。所以本系统通讯总线采用半双工RS 485总线即可达到要求,且造价低廉,稳定性好。用MAX485芯片在控制信号下可以完成与上位机的通讯,实现数据的传输,主要是接收上位机传来的选针花型数据以及发过来的控制命令。

1.3.3 掉电存储

图2中,掉电存储部分采用FM24C512。它带有2线工业标准串行接口的512 KB非易失性FRAM,且与工业标准24C512的E2PROM的引脚兼容,极易进行容量扩展。为满足系统需要,本设计采用了两片FM24C512,组成了1 MB的存储空间。该存储器以高达1 MHz的总线速度执行读操作和无须等待的写入操作,擦写次数超过100亿次,避免了一般E2PROM存储器需要很长的擦写延迟时间和轮询软件,擦写次数并少于100万次的弊端。其工作电压是5 V,读写频率在100 kHz时电流消耗为250μA,具有极低的功耗。可在-40~+85℃的工业温度范围内工作,同时提供45年的数据保留能力,信息保存可靠。利用AT-mega128的两线接口TWI(I2C)对FM24C512进行操作,简单方便,满足系统要求。正是由于以上原因,系统设计舍弃了单片机自身所具有的E2PROM而采用了FM24C512作为掉电存储器。

1.3.4 信号传输

系统的控制过程是一个闭环控制,信号传输过程如图2中所示,MCU通过花型数据来驱动提花机的贾卡动作,同时提花机将贾卡的当前状态反馈给MCU,MCU根据实时的贾卡状态修正或准备新的花型数据并驱动贾卡动作,从而形成回路控制。

控制系统一次性传输的数据量较大,每台贾卡经编机上一般有几千把导纱针同时动作,单片机控制导纱针的每一个动作都需要向外输出几千位的控制信号,使用并行输出,受单片机端口数限制必定行不通。使用串行转并行输出则可以很好地解决问题,所以系统采取的是单片机串行输出花型数据到贾卡的驱动电路,驱动电路将串行数据转化成并行数据执行动作的方式。虽然串行比并行传输的速度慢,但根据实际需要在规定的时间内传输完几千位的数据还是可以做到的。因此,信号传输过程对速度和抗干扰能力的要求较高,同时系统中贾卡驱动电路设计至关重要。

为防止电源等对信号的干扰,对输出的花型数据信号进行光电隔离,经隔离后的信号通过信号长线驱动器MC3487转换成RS 422信号,将TTL逻辑电平变为电位信号来实现信息传送。同理,MCU接收的反馈贾卡状态信号也需要经过长线驱动器MC3487和长线驱动接收器MC3486的处理后经过光隔进入单片机。这样的设计不仅可以增加系统的抗干扰能力,同时可以支持较高的传输速率和较长的传输距离。

1.3.5 光电隔离

为满足系统高速、低功耗、可靠的信号传输要求,光隔部分采用6N137光耦合器。它是一款用于单通道的高速光耦合器,其内部有一个850 nm波长A1GaAsLED和一个集成检测器组成,其检测器由一个光敏二极管、高增益线性运放及一个肖特基箝位的集电极开路的三极管组成。具有温度、电流和电压补偿功能,高的输入输出隔离,LSTTL/TTL兼容,高速(典型为10 MBd),5 mA的极小输入电流。

1.3.6 贾卡驱动

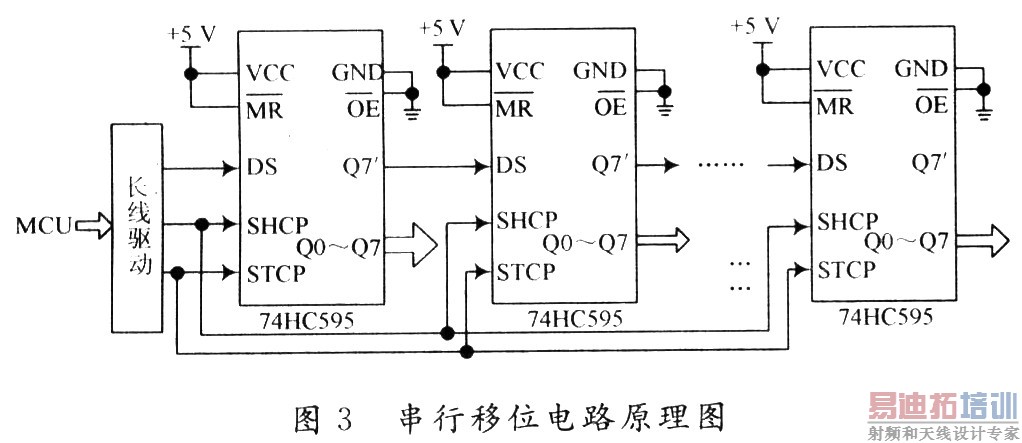

本设计采用硅结构的CMOS器件74HC595作为串行移位输出,其兼容低电压TTL电路,遵守JEDEC标准。8位串行输入、8位串行或并行输出,具有8位移位寄存器和一个存储器,三态输出功能。移位寄存器和存储器是分别的时钟。输出寄存器可以直接清除,具有1OO MHz的移位频率,并行输出,总线驱动。数据在SHCP上升沿进入移位寄存器后,在STCP上升沿输出到并行口进行驱动。串行移位输出电路原理如图3所示。

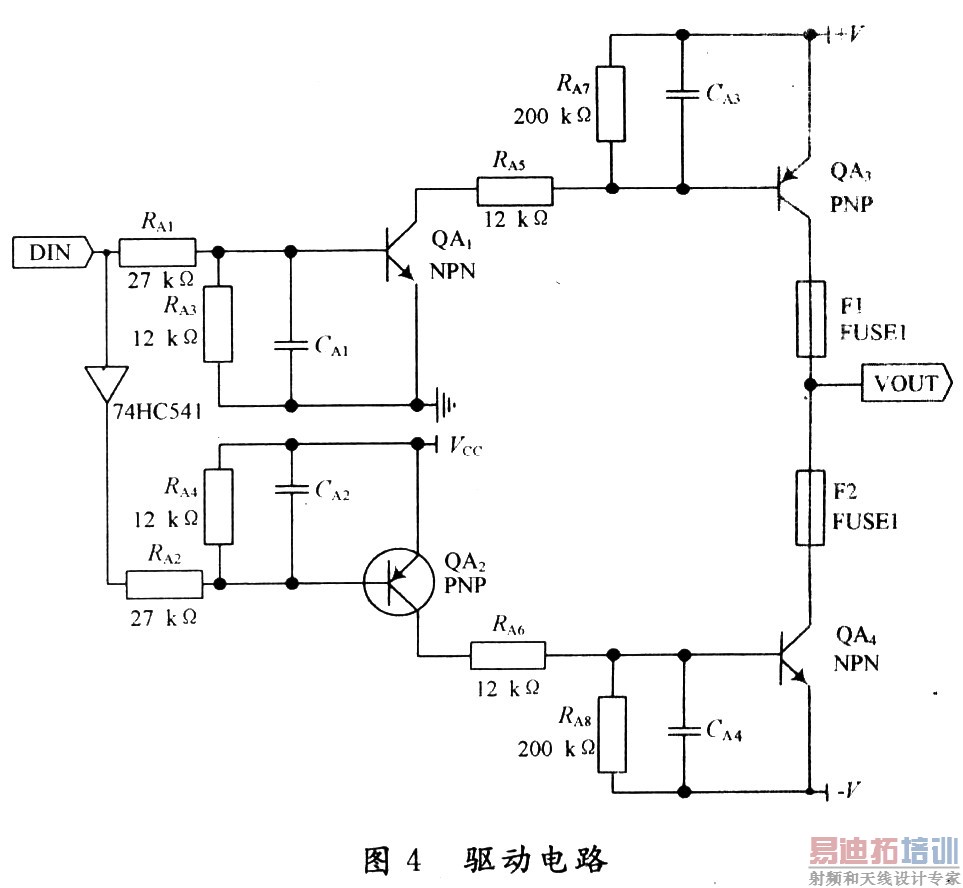

根据贾卡导纱针的工作原理,驱动电路要根据花型数据给压电陶瓷加正或负60 V直流电。驱动电路如图4所示,主要由74HC541为八缓冲器/驱动器、2个2N5551型三极管、2个2N5401等组成。

压电陶瓷驱动电路的工作原理为:由控制系统输出的脉冲信号DIN,一路输入到第一组由QA1和QA3组成的正电源开关电路,另外一路经过74HC541缓冲输入到第二组由QA2和QA4组成的负电源开关电路,这两组开关电路由DIN统一控制。当DIN为高时,第一组开关电路导通,第二组关断,正电压+V输出加到压电陶瓷端(VOUT);当DIN为低时,第二组开关电路导通,第一组关断,负电压-V输出加到电陶瓷端(VOUT)。这样通过系统输出的脉冲信号不断变化即能控制压电陶瓷导纱针的左右摆动,将电能转换成机械能,实现提花选针。

[p]

在脉冲开关电路中,为了尽量接近理想开关,晶体管则一定要工作于饱和或截止状态,而放大状态则只是在饱和、截止两个状态相互转换的瞬间经过一下。根据压电陶瓷片驱动电压60 V及驱动电流(几十毫安左右),本驱动电路选择2N5551和2N5401型三极管(Icm=600 mA,Bvceo>160 V),经验算,各三极管在此电路中能饱和。该驱动电路设计合理实用。

2 软件设计

根据控制系统的功能要求并结合上述硬件设计,再结合系统选取针花型数据的存储、花型驱动信号、主从机的数据通讯及控制等功能。然后由RS 485半双工总线的特性设计出命令表及协议。MCU在编程状态下,通过RS 485总线接收上位机发送的数据,并按顺序存储在掉电存储器中;在运行状态下,从机在同步及归零信号控制下,按顺序将数据从掉电存储器中读出,并将其解压后转换成一组贾卡导纱针。软件程序采用模块化的编程思想,采用汇编和C语言混合编写的方法。

2.1 RS 485通信程序

RS 485通信任务是从上位机把花型数据或者发过来的控制命令传送到外部扩展的FM24C512存储器中。系统采用半双工工作方式,接收上位机的花型数据,则单片机利用USART串口采用应答式实现与上位机的通信,程序流程如图5所示。

2.2 花型控制程序

本控制系统的控制信号传输采用串行转并行传输技术。其串行传输采用的是软件模拟串行同步传输。CPU从片外FM24C512读取花型控制信息,经单片机端口在时序(SHCP)配合下串行传送给74HC595进行移位缓存,数据依次由高位到低位传输。传送完花型控制信号后,单片机CPU处于等待状态。当现场向单片机发送使能信号时,则单片机对74HC595的STCP发送一个上升沿脉冲信号,从而缓冲的所有数据并行输出,从而贾卡导纱针实现一次动作。其程序框图如图6所示。

3 系统可靠性设计

贾卡经编机对系统可靠性要求很高,在系统工作时,不能出现死机及其他异常现象。因此系统在软硬件设计过程中对可靠性加以特殊的重视。下面介绍几种提高系统可靠性的主要措施。

(1)ATmega128自身具有看门狗功能,可在系统异常发生时自行重启。

(2)信号光电隔离,分组供电。采用稳定可靠的DC-DC模块24S05由24 V直流电源得到单片机需要的5 V电源,光耦及MC3486或3487需要的5 V电源另外供应,同时24 V电源为393提供电源。

(3)提高元器件及其印刷电路板的可靠性。关键元器件要严格筛选,电路板布线要严格按照PCB布线规则,充分考虑电磁兼容、抗干扰等要求。

(4)良好的接地系统,提高安全性,抑制干扰。

(5)程序采用汇编语言和C语言混合编写,以适应要求较严格的时序问题。

(6)采取充分的软件可靠性措施,例如采用串行数据的出错重传和延时调整、严格各端口的控制字、超时判断等。

4 结 语

本系统设计集成了花型数据的提取、存储、传输、校验及控制等一系列功能,实现了花型数据的数字化传输功能,提高了贾卡经编机提花控制系统的数字化水平,大大节约了花型控制的成本。此贾卡控制系统与计算机辅助花型设计系统配合可以加快贾卡经编织物的设计,简化上机工艺,缩短产品更新周期,可以很好地改进贾卡经编机设备的控制技术,系统的可靠性与实用性在样机试运行中已经得到证实。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...