- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高频率、高输入DC/DC转换器设计实例

DC/DC转换器的设计频率越来越快,目的是减小输出电容和电感的尺寸,以节省电路板空间。正因如此,现在市场上出现越来越多工作在高输入电压下的DC/DC转换器,其可提供线压瞬态保护,更低的占空比使更快频率下难以达到更低的电压。许多电源集成电路制造厂商(IC)正在积极推销高频DC/DC转换器,声称可以减少电路板空间占用。工作在1MHz或者2MHz下的DC/DC转换器似乎是一个好主意,但开关频率对电源系统产生的影响远不止体积和效率两方面。本文介绍了几个设计实例,说明在高频下开关存在的一些好处和挑战。

应用选择

为了说明使用高开关频率的权衡过程,我们设计了三个独立电源,其工作频率分别为100、300和750 kHz。所有这三种设计,输入电压均为48V,输出电压均为5V,而输出电流均为1A。这些要求常用于为一个5-V逻辑USB,或者为其它DC/DC转换器使用的中频通用5-V总线供电,例如:低压降稳压器等。若想建立一些设计限制,所选允许纹波电压需为50mV,其约为输出电压的1%;同时选择使用0.5 A的峰至峰电感电流。德州仪器TPS54160是一种集成MOSFET的2.5-MHz、60-V、1.5-A降压DC/DC转换器,用作所有设计的稳压器。TPS54160特有外部补偿和快速可编程频率,适用于一些高输入电压的工业应用。

电感和电容选择

根据下列四个简化公式,选择每种情况的电感和电容:

电感选择

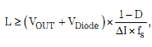

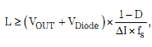

(1a)

可重写为:

(1b)

其中,D(占空比)=5 V/48 V=0.104,且△I = 0.5 A峰至峰。

电容选择

I= C x dv/dt (2a)

可重写为:

(2b)

其中,△I = 0.5 A峰至峰,且△V=50 mV。

就方程式2b而言,我们假设所选电容的等效串联电阻(ESR)忽略不计,陶瓷电容便是如此。我们选择陶瓷电容,用于所有三种设计,原因是其低电阻和小尺寸。方程式2b分子的乘数2表明DC偏压相关电容下降情况,原因是大多数陶瓷电容的数据表中都没有说明这一效应。

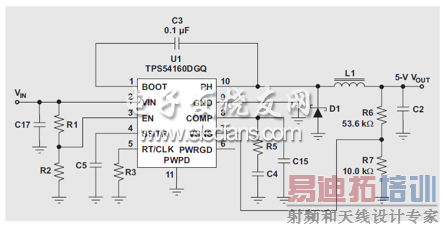

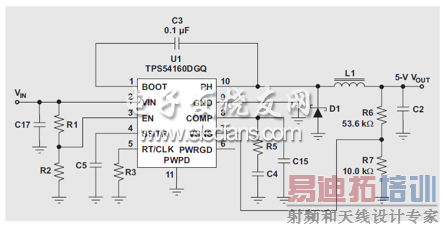

图 1 TPS54160 参考示意图

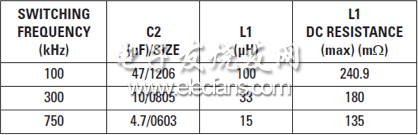

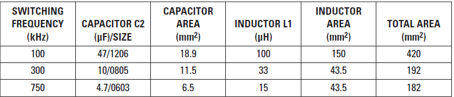

图1所示电路用于评估实验台上每种设计的性能。示意图中没有值的一些组件,为设计中修改了的组件。输出滤波器由L1和C2组成。所有三种设计的组件值都列举在表1中,这些值的选择是基于方程式1a到2b的结果。注意,每个电感的DC电阻随频率增加而减小。这是因为较少的匝数所需的铜长度更短。我们单独为每个开关频率设计了误差放大器补偿组件。选择补偿值的计算方法,超出了本文讨论的范围。

最小“导通”时间

最小可控“导通”时间限制是DC/DC转换器IC的一个特点,其为脉宽调制(PWM)电路的最窄可达脉宽。在降压转换器中,开关周期期间功率MOSFET导通的时间百分比被称作占空比,其等于输出电压与输入电压的比。使用TPS54160转换器时,占空比为0.104(4 V/48 V),而数据表中列出的最小“导通”时间为130 ns。可控脉宽限制产生一个最小可达占空比,而用最小“导通”时间乘以开关频率,我们可以轻松地计算出该占空比的大小。一旦知道了最小占空比,利用VIN乘以最小占空比,我们便可以计算出最低可达输出电压。最低输出电压同样也受转换器基准电压的限制,使用TPS54160时其为0.8V。

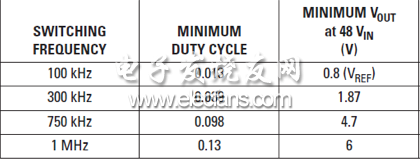

本例中,我们可以通过750-kHz开关频率来产生一个5-V输出电压(参见表2)。但是,如果该频率为1 MHz,则最低可能输出电压被限制为约6V;否则,DC/DC转换器会跳过脉冲。替代方法是降低输入电压或者频率。在选择某个开关频率以前,你最好是先查看DC/DC转换器数据表,了解保证最小可控“导通”时间。

DC/DC转换器的设计频率越来越快,目的是减小输出电容和电感的尺寸,以节省电路板空间。正因如此,现在市场上出现越来越多工作在高输入电压下的DC/DC转换器,其可提供线压瞬态保护,更低的占空比使更快频率下难以达到更低的电压。许多电源集成电路制造厂商(IC)正在积极推销高频DC/DC转换器,声称可以减少电路板空间占用。工作在1MHz或者2MHz下的DC/DC转换器似乎是一个好主意,但开关频率对电源系统产生的影响远不止体积和效率两方面。本文介绍了几个设计实例,说明在高频下开关存在的一些好处和挑战。

应用选择

为了说明使用高开关频率的权衡过程,我们设计了三个独立电源,其工作频率分别为100、300和750 kHz。所有这三种设计,输入电压均为48V,输出电压均为5V,而输出电流均为1A。这些要求常用于为一个5-V逻辑USB,或者为其它DC/DC转换器使用的中频通用5-V总线供电,例如:低压降稳压器等。若想建立一些设计限制,所选允许纹波电压需为50mV,其约为输出电压的1%;同时选择使用0.5 A的峰至峰电感电流。德州仪器TPS54160是一种集成MOSFET的2.5-MHz、60-V、1.5-A降压DC/DC转换器,用作所有设计的稳压器。TPS54160特有外部补偿和快速可编程频率,适用于一些高输入电压的工业应用。

电感和电容选择

根据下列四个简化公式,选择每种情况的电感和电容:

电感选择

(1a)

可重写为:

(1b)

其中,D(占空比)=5 V/48 V=0.104,且△I = 0.5 A峰至峰。

电容选择

I= C x dv/dt (2a)

可重写为:

(2b)

其中,△I = 0.5 A峰至峰,且△V=50 mV。

就方程式2b而言,我们假设所选电容的等效串联电阻(ESR)忽略不计,陶瓷电容便是如此。我们选择陶瓷电容,用于所有三种设计,原因是其低电阻和小尺寸。方程式2b分子的乘数2表明DC偏压相关电容下降情况,原因是大多数陶瓷电容的数据表中都没有说明这一效应。 [p] 图 1 TPS54160 参考示意图

图1所示电路用于评估实验台上每种设计的性能。示意图中没有值的一些组件,为设计中修改了的组件。输出滤波器由L1和C2组成。所有三种设计的组件值都列举在表1中,这些值的选择是基于方程式1a到2b的结果。注意,每个电感的DC电阻随频率增加而减小。这是因为较少的匝数所需的铜长度更短。我们单独为每个开关频率设计了误差放大器补偿组件。选择补偿值的计算方法,超出了本文讨论的范围。

最小“导通”时间

最小可控“导通”时间限制是DC/DC转换器IC的一个特点,其为脉宽调制(PWM)电路的最窄可达脉宽。在降压转换器中,开关周期期间功率MOSFET导通的时间百分比被称作占空比,其等于输出电压与输入电压的比。使用TPS54160转换器时,占空比为0.104(4 V/48 V),而数据表中列出的最小“导通”时间为130 ns。可控脉宽限制产生一个最小可达占空比,而用最小“导通”时间乘以开关频率,我们可以轻松地计算出该占空比的大小。一旦知道了最小占空比,利用VIN乘以最小占空比,我们便可以计算出最低可达输出电压。最低输出电压同样也受转换器基准电压的限制,使用TPS54160时其为0.8V。

本例中,我们可以通过750-kHz开关频率来产生一个5-V输出电压(参见表2)。但是,如果该频率为1 MHz,则最低可能输出电压被限制为约6V;否则,DC/DC转换器会跳过脉冲。替代方法是降低输入电压或者频率。在选择某个开关频率以前,你最好是先查看DC/DC转换器数据表,了解保证最小可控“导通”时间。

脉冲跳跃

DC/DC转换器无法足够快速地清除门驱动脉冲来维持理想占空比时,便会出现脉冲跳跃。电源会尝试调节输出电压,但由于距离更远的脉冲,纹波电压会增加。由于存在脉冲跳跃,输出纹波会呈现出分谐波成分,其可能出现噪声问题。限流电路也可能不再正常工作,因为IC可能不响应大电流峰值。一些情况下,如果控制器不正常工作,控制环路便可能会不稳定。

效率和功耗

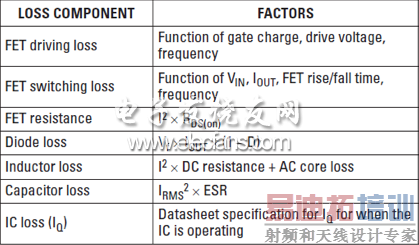

DC/DC转换器的效率,是进行电源设计时需要考虑的最重要属性之一。低效率会转换成高功耗,必须要在印刷电路板(PCB)上使用单独的散热器或者更多的铜,才能处理这些功耗。功耗也对电源上游器件提出了更高的要求。如表3所示,功耗共有几个组成部分。

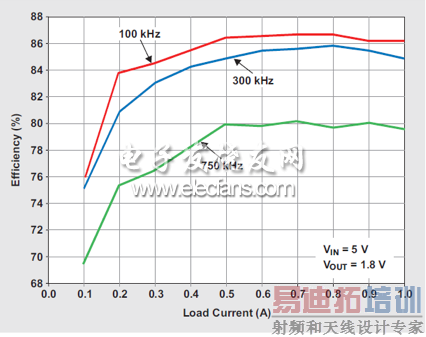

三个例子的重要损耗组成部分,来自于FET驱动损耗、FET开关损耗和电感损耗。FET电阻和IC损耗是一致的,因为所有三个设计中都使用了相同的IC。由于所有例子中都选择了低ESR的陶瓷电容,因此电容损耗可以忽略不计。为了表明高频开关的影响,我们对每个例子的效率都进行了测量,并将其显示在图2中。该图清楚地表明,效率随开关频率增加而下降。若想提高所有频率下的效率,需要寻找到一种全负载状态下低漏到源“导通”电阻、低门电荷或者低静态电流规范的DC/DC转换器;或者寻找到一些具有更低等效电阻的电容和电感。

表 1 三个举例电源设计的电容和电感选择

表 2 130-ns最小“导通”时间的最小输出电压

表 3 功耗组成部分

图 2 三个举例频率下 TPS54160 的效率

组件尺寸

表4列出了三种设计要求的总电路板面积,以及电容和电感的焊盘面积。电容或者电感的建议焊盘面积,稍稍大于单个组件本身,且三种设计举例均使用了该面积。每个组件占用的面积相加(其包括IC、滤波器以及所有其它小型电阻器和电容的焊盘尺寸),然后将得到的结果乘以2倍(考虑到组件的间距),便得到总面积。100-kHz和750-kHz设计之间存在近250 mm2的总面积节省,从而使滤波器体积缩小50%,而板空间占用减少55%。但是,存在收益递减规律,因为电容和电感值无法减少至零!换句话说,不断推高频率并不能够一直减小总尺寸,因为你无法总是能够在市场上买到这些尺寸适合且批量生产的电感和电容。注意,33-µH和15-µH电感占用相同的面积。存在这种可能性,是因为33-µH电感的高度为3.5 mm,而15-µH电感仅高2.4 mm。我们想通过这两种电感来说明的观点是:电感与体积成正比例关系。

表 4 组件尺寸和总面积要求

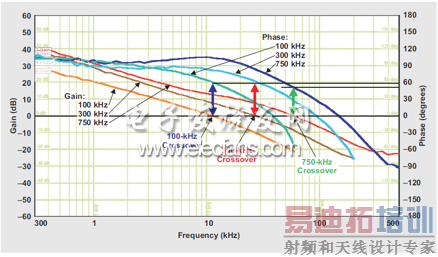

图 3 100kHz、300 kHz和750 kHz 的波特图

[p] 瞬态响应

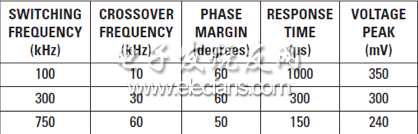

瞬态响应是电源性能级别的一个较好指标。我们利用每种电源的波特图来表明高开关频率的对比情况(参见图3)。如图所示,每个电源的相位裕度在45°和55°之间,其表明瞬态响应得到较好的抑制。交叉频率约为开关频率的1/8。使用快速开关DC/DC转换器时,设计人员应确保电源IC误差放大器具有足够的带宽来支持高交叉频率。TPS54160误差放大器的单位增益频宽一般为2.7 MHz。表5显示了实际瞬态响应时间以及电压峰值过冲的相关值。开关频率越高,过冲值便越是更低,原因是更宽的带宽。

表 5 瞬态响应

表 6 小占空比时抖动与“导通”时间之比

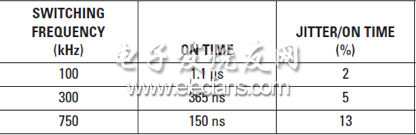

抖动考虑

高转换比和更高频率时,会存在噪声问题。当选择某个高开关频率时,设计人员应考虑抖动和DC/DC转换器的最小“导通”时间。当占空比较小时,抖动噪声便为开关脉冲的更大百分比。表6显示了48-V到5-V转换比时,抖动与“导通”时间之比。我们假设,在该相位节点上存在0.5-V二极管压降和20-ns抖动。

结论

设计高频开关转换器时,存在许多折中考虑。本文介绍的一些优点包括更小的尺寸、更快的瞬态响应,以及更小的电压过冲/欠冲。获得这些优点的代价是效率低和散热多。但是,在挑战性能极限的过程中同样也存在许多陷阱,例如:脉冲跳跃和噪声问题。在为高频应用选择一种宽输入电压DC/DC转换器以前,我们应该首先查看制造厂商提供的数据表,以了解一些重要的规范,例如:最小“导通”时间、误差放大器的增益带宽、FET电阻以及FET开关损耗。在这些规范下运行良好的IC价格昂贵,但却对得起它的价格;在设计人员担心如何处理某个棘手的设计问题时,其更加易于使用。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:医疗设备开关电源维修技术研究

下一篇:汽车环境中要求高性能电源转换的设计