- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于Virtex-5 FPGA的Gbps通信基站设计

引言

随着以TD-SCDMA为代表的3G移动通信全面进入商用部署,LTE标准基本完成,华为、爱立信成功实现LTE标准的现场演示[1],以LTE-A、IMT-Advanced为标准的下一代移动通信技术、标准与系统的研发也已经开始。

国际电信联盟(ITU)已将3G之后的未来移动通信技术正式定名为IMT-Advanced,在2007年世界无线电大会为之分配了新频段,并已经在2008年开始征集标准提案。中国也通过IMT-Advanced推进组开始为ITU技术提案征集的准备工作[2],提出国内技术提案应具有高频谱效率、低系统时延等特点,主要技术指标应达到:5-100MHz的可变系统带宽;在固定和低速移动情况下支持1Gbps的峰值速率,在高速移动情况下支持100Mbps;基站侧最多8根天线,终端侧最多4根天线;在移动性上最高支持500km/h的移动速度。

随着技术研究与提案工作的进行,基站系统的研发也已经开始。本文研究工作依托于国家“863”计划Gbps无线传输关键技术与试验系统研究开发项目,研制面向LTE-A、IMT-Advanced等未来移动通信标准,能够验证相关技术并达到标准技术指标的新型移动通信基站原型。

Gbps无线通信系统的算法链路设计

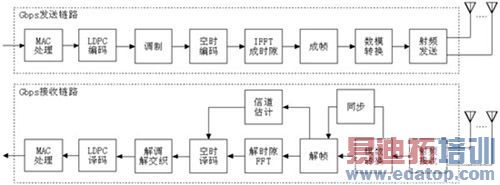

为满足未来移动通信标准的需要[3],在算法链路上Gbps系统采用时分双工(TDD)、多天线(MIMO)、空时编码、正交频分复用(OFDM)、高阶调制和LDPC编码等高性能物理层传输技术,以实现Gbps系统所需的高数据速率业务传输和高频谱效率。以频分、时分为主的多址方式实现,能够在多天线环境下对无线资源进行灵活调配,在兼顾实时话音传输的同时,最大程度上满足分组数据传输的需要。

具体而言,Gbps系统使用3.4GHz频段,实际带宽100MHz,移动台采用2发4收的天线,基站采用4发8收的天线,OFDM子载波数为2048子载波,有效为1664子载波。图1是Gbps无线传输系统的算法链路示意图。

图1Gbps无线传输系统算法链路

Gbps基站系统的设计实现考虑

移动通信基站往往在一个站址上同时有GSM、TD-SCDMA等多种标准的基站,越来越多地呈现多标准共存的局面,基站研发应当着眼于降低建设、运营维护和升级成本。对此,Gbps无线通信基站应当采用可重配置方式,在支持Gbps无线传输的同时能够兼容未来的LTE-A、IMT-Advanced标准,实现平滑演进。

从实现技术上看,实现信号处理算法并支持可重配置需要可编程的处理器件,现代基站系统广泛采用的可编程处理器以DSP和FPGA为主。尽管高端多核DSP的工作时钟频率已经提升到1.2GHz,在TD-SCDMA基站中得到广泛应用,但还是无法满足Gbps系统中同步、MIMO、LDPC等算法对信号处理复杂度和实时性的要求。因此,Gbps项目需要采用大容量的高性能FPGA来作为复杂算法的承载平台。

从基站系统的互连与数据传输机制上看,互连连接所有的无线接口、网络接口和计算资源,传输代表计算任务的数据,是使基站系统成为整体、协调运行的关键要素。由于MIMO算法需要多天线输入数据到多基带处理芯片的传输,应当采用以交换式互连网络和分组数据传输机制,更好满足未来基站系统中MIMO、并行处理、动态可重配置、计算资源动态调度等的需要。

综合以上设计实现考虑,经过综合调研考察,Gbps项目决定采用Xilinx公司Virtex-5系列FPGA构架硬件系统平台[4],承载复杂的信号处理算法,采用串行RapidIO[5]技术作为板间高性能互连,采用千兆以太网(GE)连接业务服务器及LMT计算机。

Virtex-5FPGA介绍

Virtex-5系列FPGA是Xilinx率先发布和量产的65nm平台FPGA,目前包括LX、LXT、SXT、FXT及TXT等面向不同应用的多个子系列。

Virtex-5系列FPGA最高工作时钟可以达到550MHz,总逻辑单元数多达330,000个。提供了高达11.6Mbit的灵活嵌入式BlockRAM,能有效地存储和缓冲各种运算数据。多达640个

增强型嵌入式DSP48Eslice块,可以满足高性能DSP算法加速的需要,实现352GMACs的性能。Virtex-5FXT系列FPGA提供多达两个标准的PowerPC 440处理器模块,每个处理器在550 MHz时钟频率下可提供1,100 DMIPS 的性能。利用PowerPC 440嵌入式处理器模块,可快速方便地实现Gbps基站中复杂的控制和通信协议处理。

Virtex-5系列FPGA集成100Mbps–6.5Gbps的高性能收发器,配合FPGA内部编程实现的串行RapidIO逻辑层模块可以实现芯片间和板间高性能的数据交换互连。集成符合IEEE802.3标准的10/100/1000Mbps以太网MAC硬核,连接外部GEPHY或直接使用FPGA本身的GTP/GTX,就可以实现高性能的千兆以太网接口。

算法对资源的需求及FPGA型号的确定

分析Gbps算法链路中各算法的不同实现特点并对运算量以及使用的主要资源进行估计,可以确定所需要使用的FPGA。表1是资源需求估计与FPGA选择的结果,表2是目标FPGA内部资源情况的总结。

表1Gbps无线通信基站系统算法链路对FPGA