- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于DDS技术和单片机设计的射频信号干扰器

文中介绍的干扰器能够产生3种干扰信号:随机干扰、点频干扰和扫频干扰,其中点频干扰和扫频干扰是基于单片机对DDS芯片AD9852的控制产生,整个系统的控制灵活、高效。测试结果表明,系统能够准确产生所需要的干扰信号,满足抗干扰性能测试的需要。虽然本设计产生的干扰信号位于406 MHz频段,但这样的电路结构也可用于其它频段(需修改VCO、PLL等电路),例如手机通信频段,因此本电路结构对其它频段的应用同样具有借鉴意义。

随着电子设备的使用越来越普遍,电子设备之间的干扰问题也越来越突出,特别是通信设备的干扰问题,这使得电路工程师在电子产品的设计过程中不得不考虑设备的抗干扰问题,并且有必要对通信设备的抗干扰能力进行测试。文中介绍的射频信号干扰器可用于测试通信设备的抗干扰能力,能够产生如下3种干扰:

1)随机干扰。在目标频率范围内产生频率随机的干扰信号,湮没目标频率,也会降低信噪比,形成对正常通信的压制。

2)点频干扰。在已知目标频率的情况下,瞄准目标频率输出干扰信号,产生对目标通信的压制效果。

3)扫频干扰。在目标频率范围内进行频率扫描,当干扰信号频率与通信频率的碰撞概率达到一定数值时,就会影响通信的信噪比,导致误码率增加,产生有效干扰。

射频信号干扰器的设计基于DDS技术和锁相环(PLL)技术,通过单片机进行控制,能够产生分辨率极高的干扰频率,控制方便、灵活。

1硬件电路设计

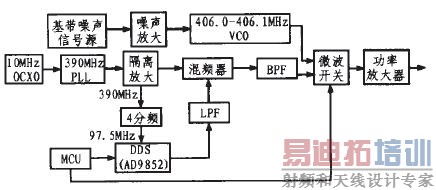

射频信号干扰器原理框图如图1所示,当微波开关接通406.0~406.1 MHZVCO时,输出随机干扰噪声;当微波开关接通BPF时,输出点频干扰或扫频干扰噪声。

图1硬件系统原理框图

1.1随机干扰

基带噪声信号源的随机电压噪声施加到VCO的电压控制端,产生噪声调频信号。406.0~406.1 MHZVCO输出信号的频率表示为:

ωvco=ωo+Kvco(Vo+Anu(t)) (1)

式中:ωo为控制电压为零时VCO输出频率,Kvco为VCO电压控制增益,Vo为直流控制电压,An为噪声放大电路增益,u(t)为基带噪声信号。

当微波开关选通随机噪声输出时,输出信号为

Vo(t)=KSKAUvcoCOS(ωo+Kvco(Vo+Anu(t)) (2)

式中:KS为微波开关增益,KA为放大器增益,Uvco为VCO输出信号幅度。干扰机的输出为调频噪声,噪声幅度为KSKAUvco,噪声的中心频率为ωo+Kvco(Vo,噪声频谱的范围取决于Anu(t)的幅度。

1.2点频干扰与扫频干扰

点频干扰与扫频干扰通过单片机控制DDS专用芯片AD9852实现,AD9852具有功耗低,相位累加器位数高,可产生高频率的正弦波等优点。

DDS输出频率:

f0=KF×fc/2N (3)

其中,KF为频率控制字,fc为外部参考时钟的频率,Ⅳ为DDS相位累加器位数。AD9852的频率控制字为48bit,即N=48。

输出频率分辨率由下列公式决定:

Δf=fc/2N (4)

根据Nyquist定理,DDS外部参考时钟频率至少是输出频率的2倍(f0/2),但工程应用中,一般将参考频率设为最高输出频率的5倍以上。本设计中参考频率为97.5MHz,将的值代入式(4),得DDS输出信号的频率分辨率为3.5 × 10-7Hz。

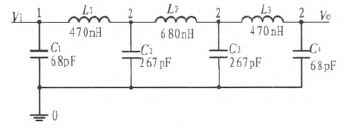

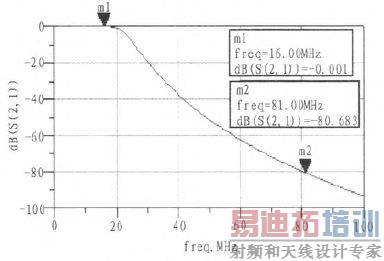

AD9852内置12bit DAC,其输出模拟信号频谱中除f0外还带有fc、fc±f0等频率分量(fc一f0的频率最低),需设计一个LPF将其滤除,此处采用了图2所示的七阶Butterworth低通滤波器,对该滤波器使用ADS仿真的结果如图3所示,81 MHz处的衰减达到- 80.683 dB。

图2七阶Butterwoth低通滤波器

图3滤波器仿真结果

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:太赫兹波超材料近场调控研究新进展

下一篇:测试环路滤波器及射频电路设计