求助:如何来验证自己设计的AFC(自动频率控制)

录入:edatop.com 阅读:

RT~

求助:如何用FPGA来验证AFC(自动频率控制)

由于AFC里面的fvco很快,所以我采用的办法是先进行一个分频得到一组四相时钟再进行记数的,但是即使这样counter的时钟还是有500M左右,不知道fpga能否跑这么高的频率,而且由于AFC的结构问题,为了得到一个反馈的fvco,用fpga怎么实现啊?因为涉及到锁相环的问题~

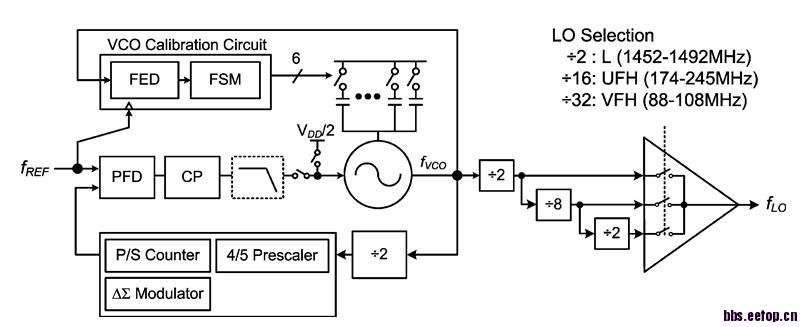

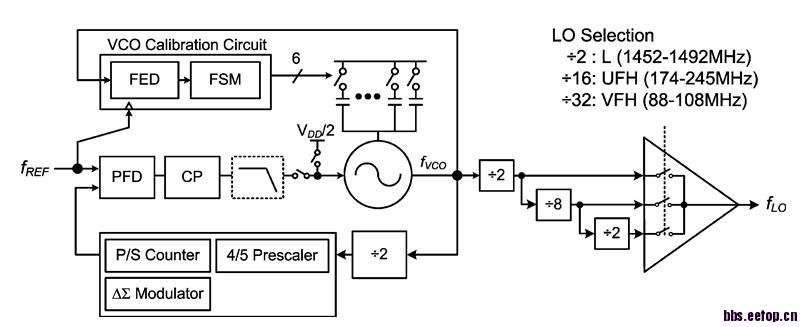

AFC的结构如图所示~

新手求帮助

求助:如何用FPGA来验证AFC(自动频率控制)

由于AFC里面的fvco很快,所以我采用的办法是先进行一个分频得到一组四相时钟再进行记数的,但是即使这样counter的时钟还是有500M左右,不知道fpga能否跑这么高的频率,而且由于AFC的结构问题,为了得到一个反馈的fvco,用fpga怎么实现啊?因为涉及到锁相环的问题~

AFC的结构如图所示~

新手求帮助

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:HSPICE 的优化的到电感模型

下一篇:问前辈们有关共模电压的问题