一个简单的verilog初值问题。

录入:edatop.com 阅读:

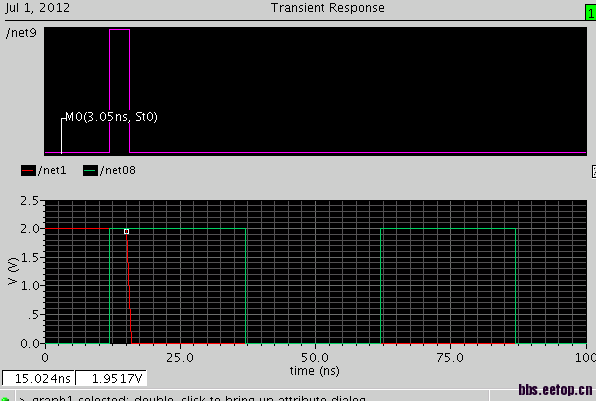

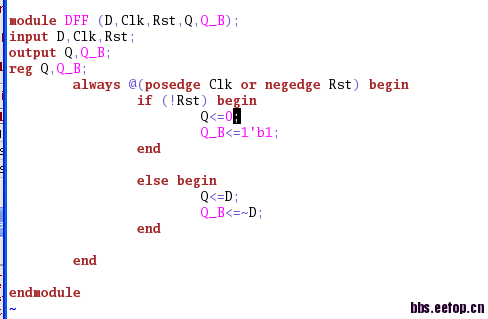

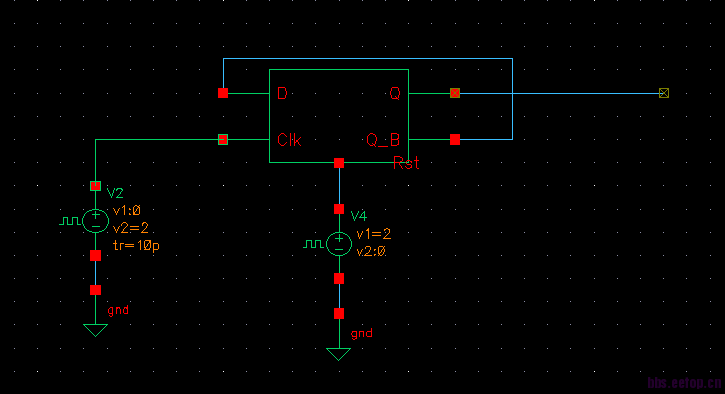

小弟想问个简单的verilog的初值问题·。上面是个DFF的verilog代码。后面两幅图是仿真结果,图中的粉红色的仿真结果为Q的输出,可以看出初值为0。但是我想问的是,此时reset为高电平,而且posedge CLk也不满足,为何会有初值,为何(RST!)会执行,会复位?很困惑,照理说应该是不定态吧......

小弟想问个简单的verilog的初值问题·。上面是个DFF的verilog代码。后面两幅图是仿真结果,图中的粉红色的仿真结果为Q的输出,可以看出初值为0。但是我想问的是,此时reset为高电平,而且posedge CLk也不满足,为何会有初值,为何(RST!)会执行,会复位?很困惑,照理说应该是不定态吧......

psoedge CLK不满足,reset为高的时候出现的低点平Q输出,和posedge CLK满足,reset为高的时候出现的高电平Q输出,都是复位前的不定态。因为你的DFF代码中规定了RST低电平复位。为什么会产生不定态呢,很简单,你的代码没规定这个状态啊。这个代码只规定了沿触发的时候的行为。

嗯·,我想我问得不太清楚吧,看仿真结果,有初态,为0啊(粉红色的),绿色的线为时钟,红色的为RST,初态应该是不定态啊,对不对?但仿真显示为0态。always语句块不满足的情况下,为何会有初态(0)?

这个要看仿真器怎么处理这个未定义的状态了吧. 你的代码反正没定义这个, 出什么都是你不关心的. 如果要定义就应该能明确看到输出. 或者你给一个不一样的初始值在节点上,看看有没有变化.

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:此 Class AB 運放增益為何

下一篇:电压模的DC-DC有什么优点?