请教一个困扰很久的PLL相位噪声叠加问题

录入:edatop.com 阅读:

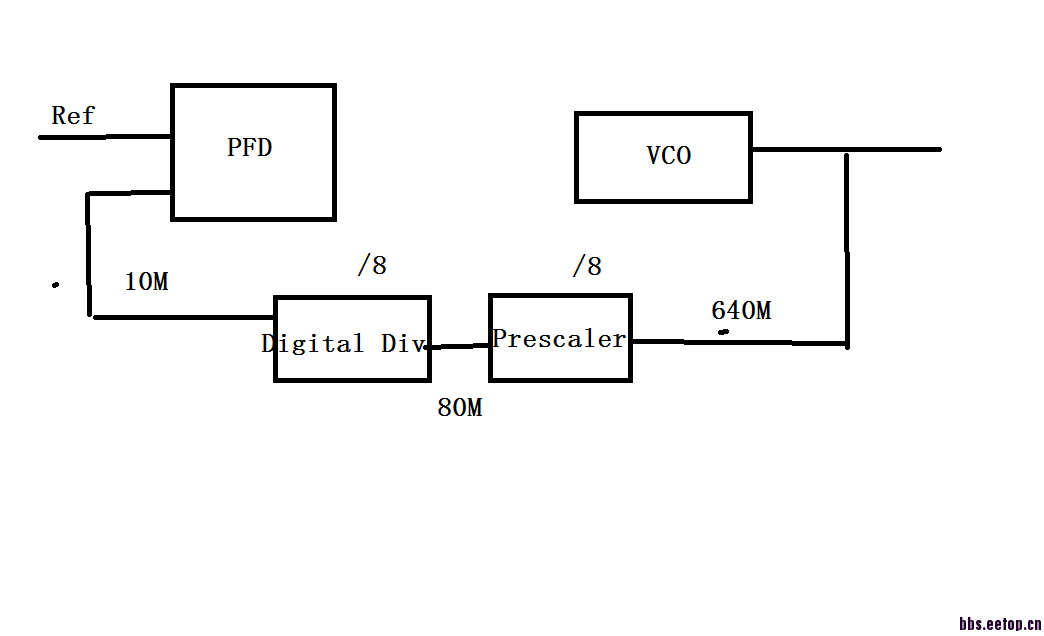

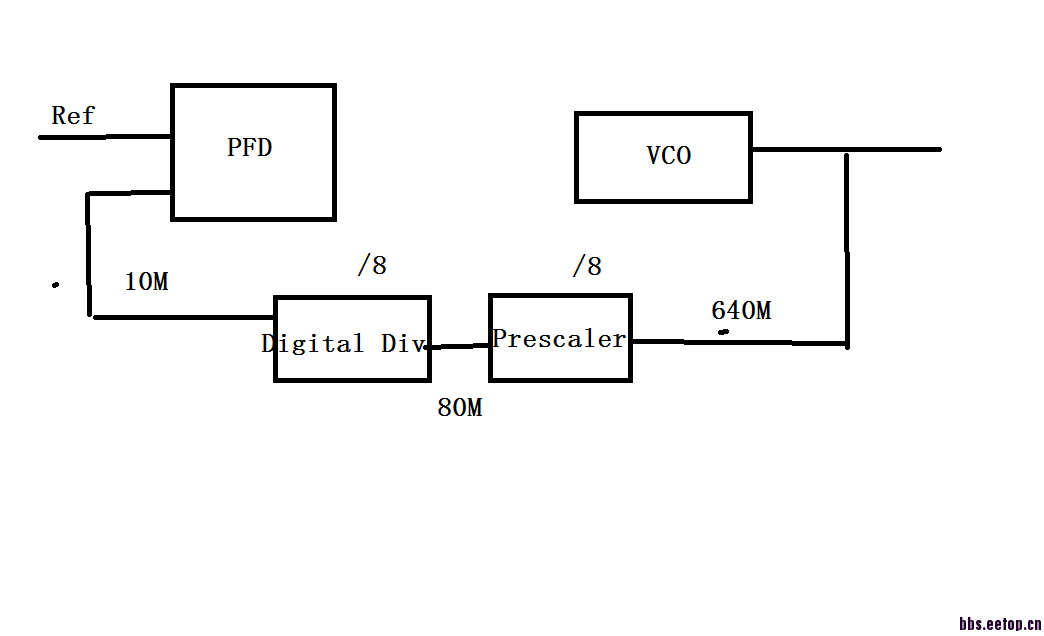

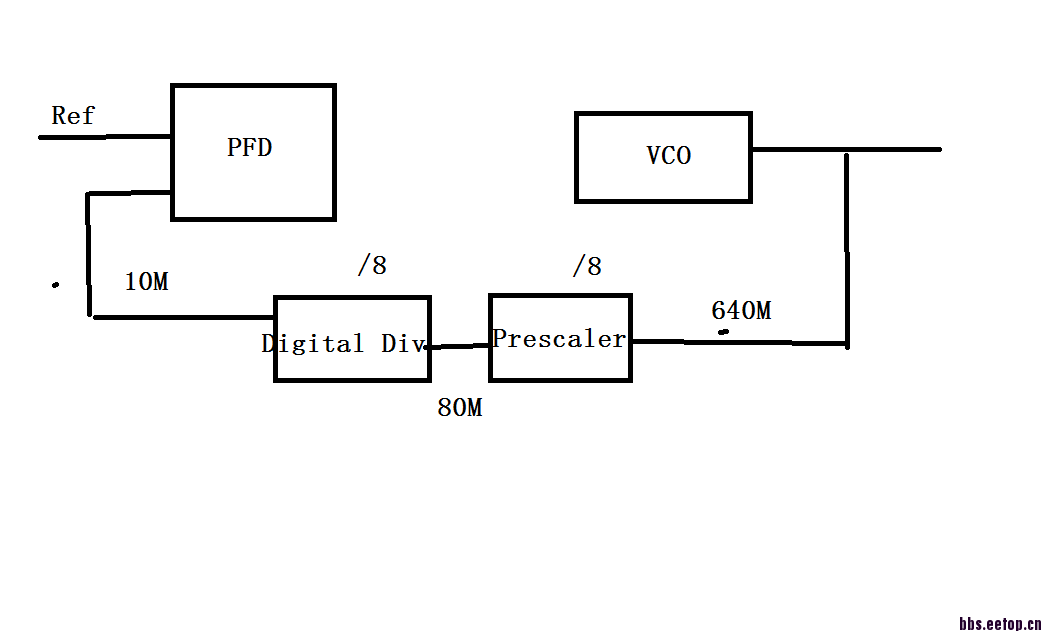

是这样的,在PLL VCO输出到PFD的分频器路径上,采用的是模拟预分频加数字分频串联结构,如图一,VCO输出640M信号,由模拟预分频器进行八分频,输出80MHz信号,再由数字分频器进行八分频,输出10MHz信号,其实是小数分频结构,为了解释问题,分频比是随便定的,只是为了方便说明。

在进行相噪噪声的仿真过程中,出现这么个问题,假设模拟部分输出的相位噪声是PNa,数字部分输出的相位噪声是PNd,那么可以对两个模块分别进行仿真,然后通过叠加,可以得到在10MHz输出处,总的相位噪声应该是【PNa-20*log10(8)】+PNb,相位噪声通过分频器降低20倍的log(N),我之前一直是这么理解的。

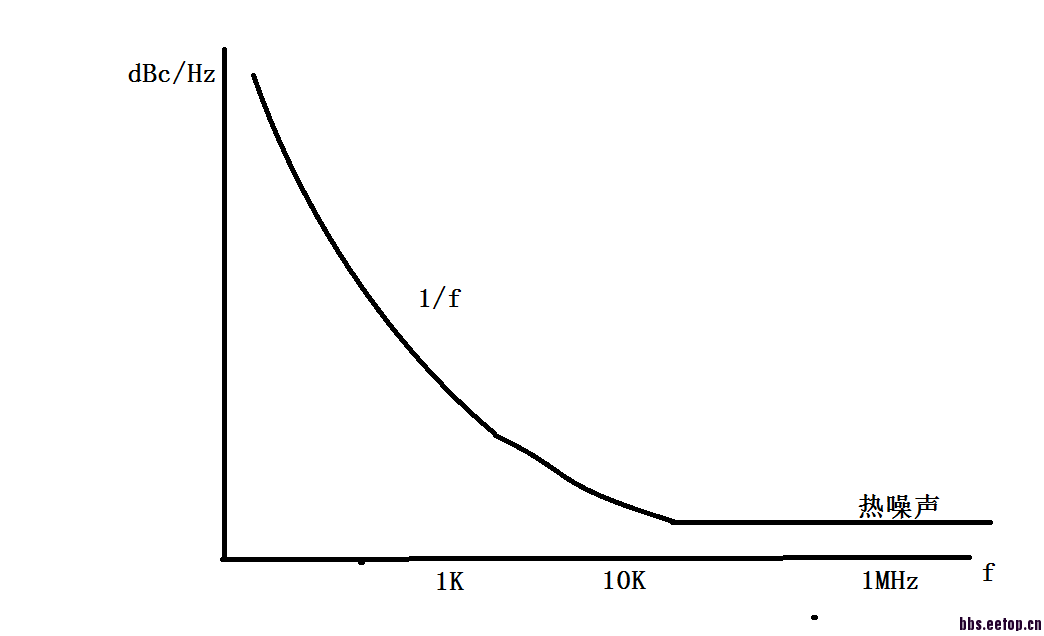

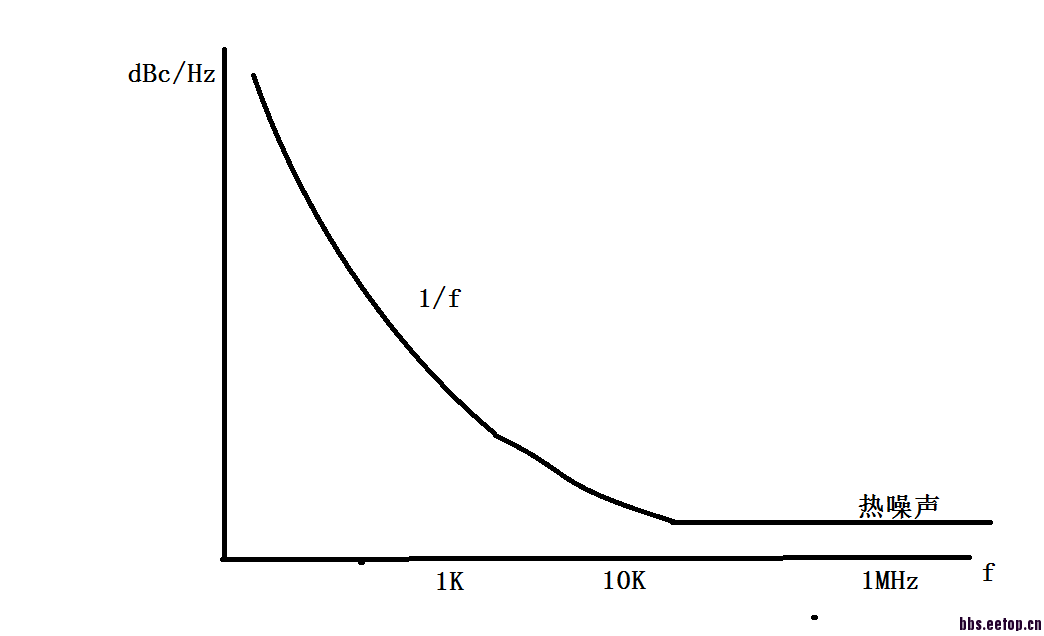

但是现在出现了问题,我通过叠加后,计算出来的结果,和对两部分电路整体仿真出来的结果出现了偏差,在高频处,1MHz频偏处,吻合的很好,但是在低频处,例如1KHz处,缺出现了错误。大家应该都知道,分频器的相位噪声曲线一般是如图二的形式,低频处闪烁噪声占主导,高频处热噪声占主导。现在发现,模拟预分频的热噪声通过20倍的log(N)衰减到了数字输出,N=8,然后通过与数字分频器噪声叠加,正好就是数模分频器总的输出相位噪声。但是奇怪的是,整体仿真结果表明低频处的闪烁噪声却全部由数字部分决定,模拟部分的闪烁噪声消失了,也就是说单仿第二级分频器和整体仿真得到的相噪几乎一样(这块模拟部分的闪烁噪声是很大的,所以不会出现由于过小被数字闪烁噪声湮没的问题)。

我以上的结论都是spectre下通过pss和pnoise仿真的现象,我现在有个问题,为什么第一级分频器输出的热噪声可以通过第二级分频器,闪烁噪声却没有了,

是因为闪烁噪声完全不能通过分频器吗?被分频器抑制了

还是说这两个模块的闪烁噪声是不相关的,不能进行叠加,只能又第二级的数字部分决定。

希望理论知识扎实的朋友能给我一个解释,谢谢!

在进行相噪噪声的仿真过程中,出现这么个问题,假设模拟部分输出的相位噪声是PNa,数字部分输出的相位噪声是PNd,那么可以对两个模块分别进行仿真,然后通过叠加,可以得到在10MHz输出处,总的相位噪声应该是【PNa-20*log10(8)】+PNb,相位噪声通过分频器降低20倍的log(N),我之前一直是这么理解的。

但是现在出现了问题,我通过叠加后,计算出来的结果,和对两部分电路整体仿真出来的结果出现了偏差,在高频处,1MHz频偏处,吻合的很好,但是在低频处,例如1KHz处,缺出现了错误。大家应该都知道,分频器的相位噪声曲线一般是如图二的形式,低频处闪烁噪声占主导,高频处热噪声占主导。现在发现,模拟预分频的热噪声通过20倍的log(N)衰减到了数字输出,N=8,然后通过与数字分频器噪声叠加,正好就是数模分频器总的输出相位噪声。但是奇怪的是,整体仿真结果表明低频处的闪烁噪声却全部由数字部分决定,模拟部分的闪烁噪声消失了,也就是说单仿第二级分频器和整体仿真得到的相噪几乎一样(这块模拟部分的闪烁噪声是很大的,所以不会出现由于过小被数字闪烁噪声湮没的问题)。

我以上的结论都是spectre下通过pss和pnoise仿真的现象,我现在有个问题,为什么第一级分频器输出的热噪声可以通过第二级分频器,闪烁噪声却没有了,

是因为闪烁噪声完全不能通过分频器吗?被分频器抑制了

还是说这两个模块的闪烁噪声是不相关的,不能进行叠加,只能又第二级的数字部分决定。

希望理论知识扎实的朋友能给我一个解释,谢谢!

每日一顶 每人研究过吗

每日一顶 每人研究过吗

有人能救救我吗?能给个解释吗?

没人只能流片验证了!

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:LDO瞬态响应太快的疑问

下一篇:IC5414 无法启动