vco降噪问题

没人回答吗?急啊~

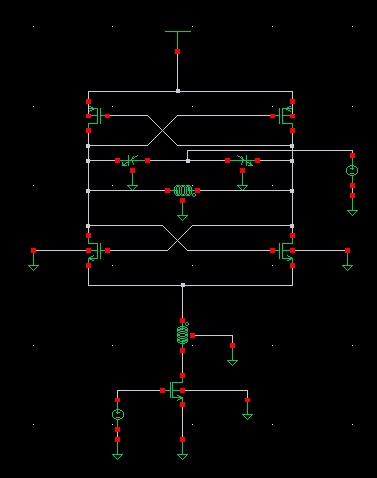

有图吗》?

1.先搞清楚电感的自谐振频率在哪里,那么高频的vco,LC 又要在2f0, 电感的模型支持吗?

2.一般这么高频的vco 都采用单nmos 或者单pmos 耦合的

3.最好把完整的电流镜带上,这样仿真出来的pn才更真实一些

偏压的好坏对相位噪声的影响很大的

1、自谐振频率是24.4G,但是加电感谐振在2w0后,频率w0会变大一点,电感选的是TSMC 0.18的库,谐振在2W0的话就是48.8G,电感可以啊 2、我看的论文是一般是采用单nmos 耦合的,就想换个结构做做~

3、完整的电流镜也用过,因为有2个管子,每次调太麻烦了。感觉pn变化不大~

还有,我应该怎么降低噪声啊~二次谐波降噪不行吗?还是互补结构不行?或者用其他的降噪技术?

什么偏压,不好意思,能说清楚一点吗?

不要沉啊

1.我说的是电感的自谐振频率 不是vco的震荡频率 不知道你看过库里面的电感的应用频率没有

2.把完整的bias带上 才能真实的反应电路的性能

3.都几十GHz了 管子当然是越少越好 结构越简单越好

4.相位噪声 就和Q值有关 二次谐波抑制 就是为了提高电路的Q值 ,选个Q值高的电感 ,足够大的摆幅 也都是为了提高电路Q值

5.注意24GHz 制约整个电路Q值的变成了变容管 而不是电感了

6. .18库的管子 到24GHz model 会准吗? 这个真的难说

7. 没有十全十美的电路 ,工程师的工作就是meet spec ,那么高频的应用下 1M下 这样的PN 肯定是够用了

8. 怎么样画好版图 才是你要下功夫的

真的非常非常感谢~

那个电感的自谐振频率怎么看啊~还有,我用24G扫描电感,计算L是正值,是不是没达到谐振频率啊?

不要沉啊

那个电感的自谐振频率怎么看啊~还有,我用24G扫描电感,计算L是正值,是不是没达到谐振频率啊?

这个啥么LC滤波paper里有很多,以前自己仿过,效果不大,感觉就是个骗人的玩意,用来发paper的。流片测试才知道phase noise和输出功率相关性较大。而且加个电感 layout 也不好画呀。不知道其他人怎么看的?

但是我师姐用单MOS管结构,二次谐波降噪能降7~8dB,难道是结构问题?

仿真电感的电抗值 横轴是频率 从正到负的拐点 就是电感自身的自谐振频率 也就说高于这个频率电感就成电容了

你的spec是多少频偏处多少相噪 功耗要多少 频率范围是多少

固定频率值,扫描尺寸,得到电感值是正的,这样可以吗?

1M频偏-106dBc/Hz,功耗5.4mV,频率范围23.1~25.7 GHz。

是因为电感模型不准所以不能二次谐波降噪吗?但是有人做过,结构不一样,也能降噪呢,用的也是0.18um的电感。

固定频率在48.8GHz吗? LC谐振在2w0的目的是 为了形成高阻 组织2w0 能量泄露到底, 如果滤波没有效果,原因只能是1.没有形成高阻 2。形成的高阻不在2w0。 你好好想想吧~

我改变了电感的感值,相噪有变化但是变化不大,差不多,应该不是形成的高阻不在2w0吧?难道是没形成高阻,感觉不太可能啊。我发现我的尾电流源vds<vdsat,不在饱和区,这有影响么?我用一个MOS管做尾电流源,发现栅极越大,相噪越好,但是栅极变大就不在饱和区了,为什么?

看来你模拟集成电路也没学好 好好看书吧 有师兄师姐带吗

做电路要有感觉 但是要 证明什么是什么 不是跟人家说感觉怎么怎么样就行的 要仿真结果的····· 你证明给我看LC形成的高阻的在哪个频率把

我用TRAN仿了,在共模点几乎是2倍的基频,这能不能证明啊?请教一下,我是不是尾电流没设计好啊?

当然不能 ····· 共模点本来就是有二倍频波形的 和你加不加电感 没关系

额,我不知道怎么证明,您能告诉我这个VCO设计哪里可能出问题了吗?

不加尾电流源 也能振的 相噪还更好呢 ! 好好看一篇别人的硕士论文吧,感觉你做vco 不是在设计 而是在凑。

仿真共模点的阻抗 如果阻抗在2w0有一个明显的尖峰 说明是设计对了,一般 这个电感的Q值的要求和tank里的要求正好相反,小一些比较好,这样阻抗可以在比较宽的频率范围内 都可以高阻

我试试看,真的非常感谢~

话说大侠您做的VCO结果最后是啥呢,目前我也需要做个高频的VCO,(方便告诉我您的电路参数吗?方便的话 请发我邮箱420462303@qq.com)如果需要好的相位噪声一般什么结构会好点,拜谢中

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。