DNL和INL很差,高手帮我看看ADC问题出在哪里?

录入:edatop.com 阅读:

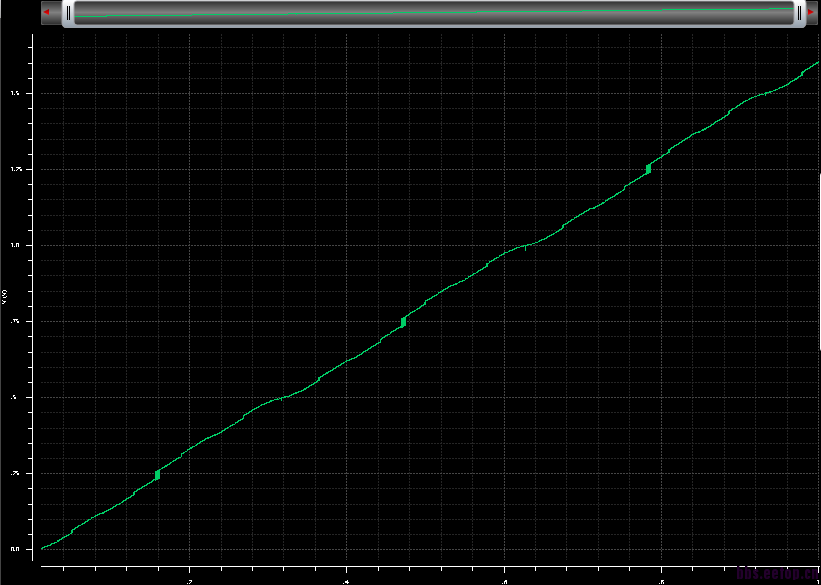

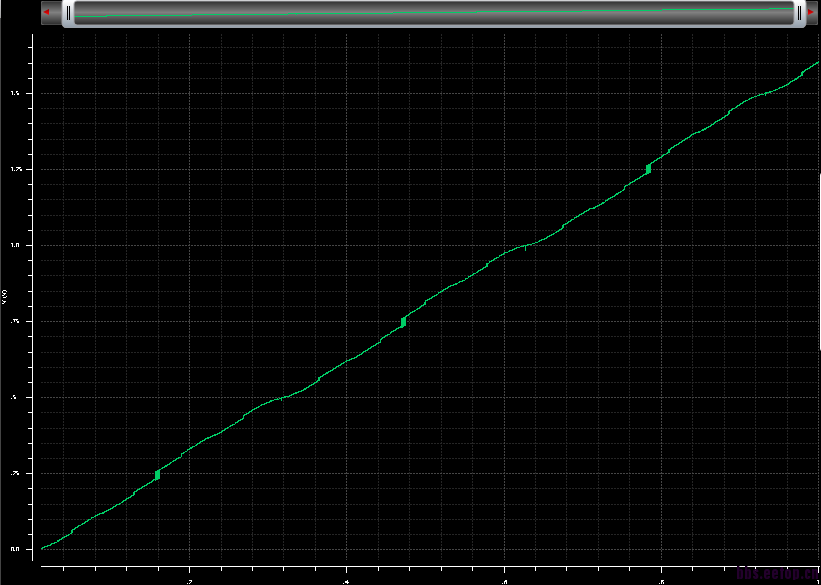

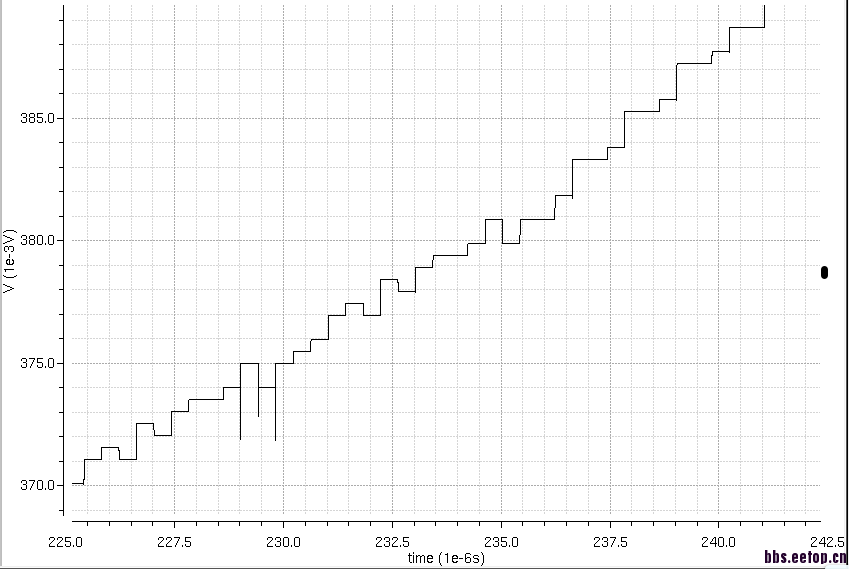

最近对12bit 流水线ADC做仿真,给三角波线性渐变电压,输出结果(理想DAC转换之后的)如下图1,图2细节图。

可以看出DNL和INL很差,有的地方还有小幅振荡(貌似是比较器在阈值附近的振荡引起)

请问大牛们,我设计的这个ADC哪里存在问题?

可以看出DNL和INL很差,有的地方还有小幅振荡(貌似是比较器在阈值附近的振荡引起)

请问大牛们,我设计的这个ADC哪里存在问题?

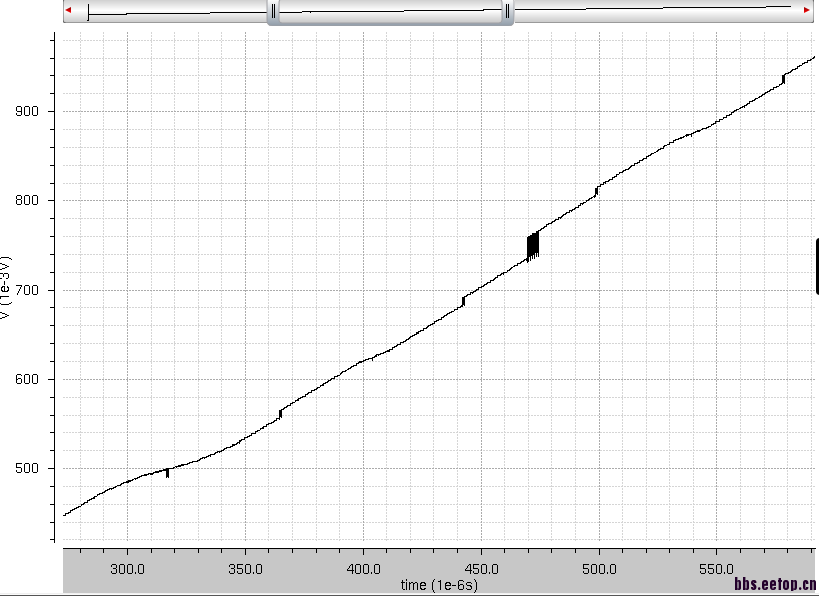

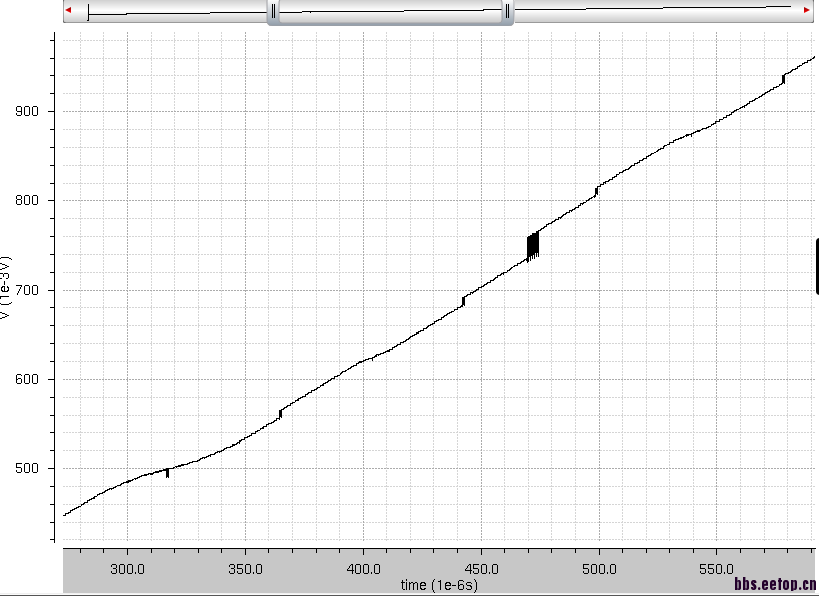

再补一张细节图

做ADC的牛们难道都不会啊?没人帮你解决啊。呵呵。没做过不懂,猜测问题应该是很多地方的小问题积累引起的。

function都没有做对,还看什么INL/DNL

先要debug function

还没看monte carlo就这样了...建议从最基本电路的开始做

谢谢,是我的比较器出了问题,在阈值附近会来回振荡,请问你们仿真时有这种问题吗?

pipeline ADC 加了冗余位后比较器有判断误差也没有关系的啊

目测你的量化曲线有跳变也有弯曲,是不是放大器增益太低?输出饱和了?还是加了电容误差但是没有校准?

你好,能帮忙推荐一个离散比较器的结构吗?

我的目标是做个12bit 5M 100mW左右的ADC

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:各位大神,rail to rail 运放的线性度THD最大能做到多少?

下一篇:模拟设计的存储器电路仿真激励怎么弄啊