cadence数模混合仿真问题求助

录入:edatop.com 阅读:

rt,在cadence数模混合仿真时出现问题,clk上升沿不触发,反而在高电平时触发,所以时序一直不对~

这是在纯数字的部分的问题,但数字部分电路用modelsim中仿真没问题,放到cadence中混合仿真就不对了~

求教下如何解决中问题~

主要就是时钟沿触发问题!

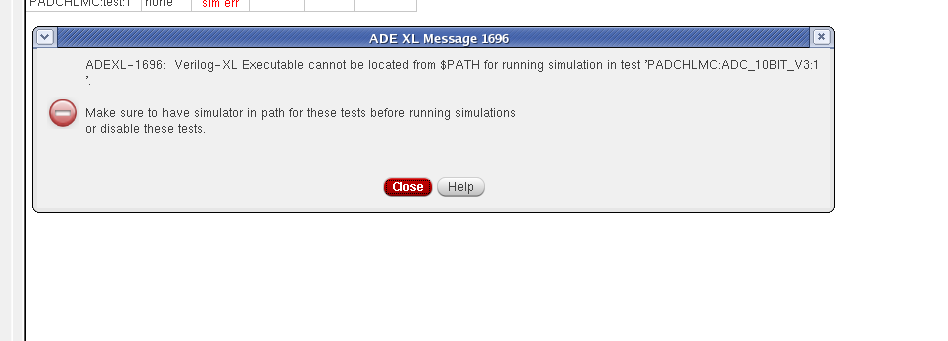

Error found by spectre during AHDL read-in.

ERROR (VACOMP-1008): Cannot compile ahdlcmi module library. Check the log file input.ahdlSimDB/890_work61_PADCHLMC_DA12_veriloga_veriloga.va.d2a_ideal.ahdlcmi/Linux2.6.9-89.ELlargesmp+gcc/../ahdlcmi.out for details. If the compiler ran out of memory, use 'setenv CDS_CMI_COMPLEVEL 0', and try again. If the reason for the failure was a syntax error, contact your Cadence Customer Support representative with the netlist, log files, behavioral model files, and any other information that can help identify the problem.

这是在纯数字的部分的问题,但数字部分电路用modelsim中仿真没问题,放到cadence中混合仿真就不对了~

求教下如何解决中问题~

主要就是时钟沿触发问题!

求大神帮助~

求帮助~

你用的是ams混合仿真吗?如果是的话,修改connectrule,用verilogspectre应该是可以跑成功的

帮顶一下

可能是精度的设置没设置好

用spectreverilog仿真的话感觉会好些,但是比较慢

也是这个问题呢

去cadence官网上看看

我的是615 为什么在模拟仿真中加入 verilogA symbol 就跑不了了呢?

具体报的什么错误?要把它发上来看看才知道

谢谢你 mmsim不能做混合仿真 需要配置其他的软件是吗?

Error found by spectre during AHDL read-in.

ERROR (VACOMP-1008): Cannot compile ahdlcmi module library. Check the log file input.ahdlSimDB/890_work61_PADCHLMC_DA12_veriloga_veriloga.va.d2a_ideal.ahdlcmi/Linux2.6.9-89.ELlargesmp+gcc/../ahdlcmi.out for details. If the compiler ran out of memory, use 'setenv CDS_CMI_COMPLEVEL 0', and try again. If the reason for the failure was a syntax error, contact your Cadence Customer Support representative with the netlist, log files, behavioral model files, and any other information that can help identify the problem.

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。