流水线ADC比较器的时钟问题

录入:edatop.com 阅读:

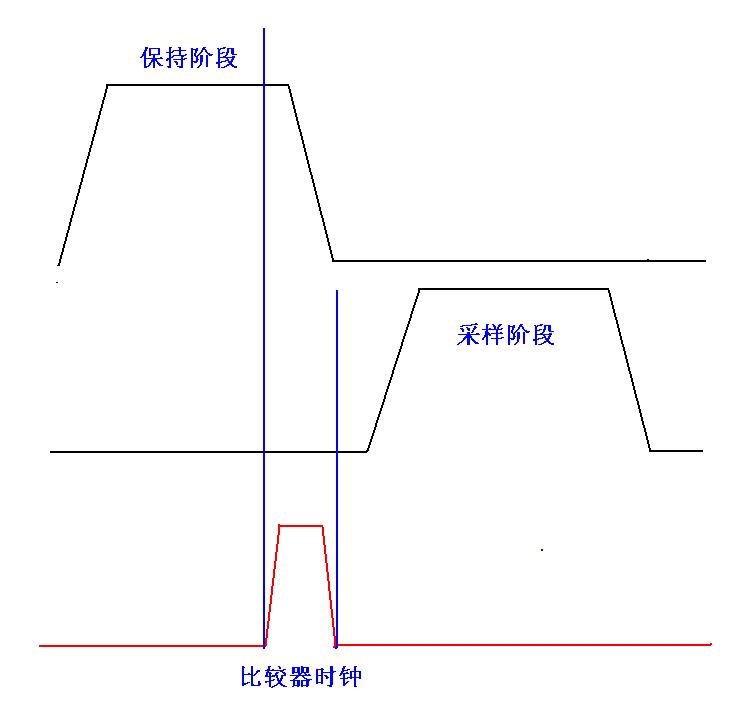

新手设计流水线ADC,在设计比较器的时钟时遇到一个问题。在MDAC的信号保持阶段,实际信号的建立需要一定的时间,因此,在信号建立的末期(快结束时),将信号采集到比较器内进行比较,是最接近理想状态的。

因此对于比较器的控制时钟,它的上升沿(开始比较的时刻)应该在CLK2(保持)高电平的快结束时,同时它的下降沿应该在下个周期CLK1(保持阶段)的上升沿之前。

如下图所示

不知道这样设计时钟是否合理? 怎么设计这个比较器控制时钟的生成电路?

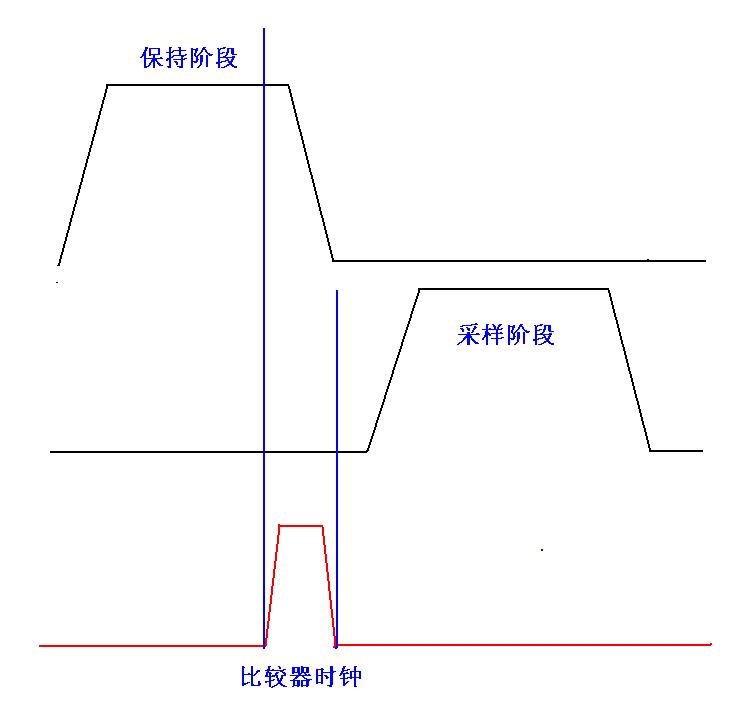

比较器电路和MDAC的CLK时钟的生成电路如下图:

因此对于比较器的控制时钟,它的上升沿(开始比较的时刻)应该在CLK2(保持)高电平的快结束时,同时它的下降沿应该在下个周期CLK1(保持阶段)的上升沿之前。

如下图所示

不知道这样设计时钟是否合理? 怎么设计这个比较器控制时钟的生成电路?

比较器电路和MDAC的CLK时钟的生成电路如下图:

比较器 的时钟可以再长一些哦

LZ理解的不太对哦

比较器Latch应该在MDAC进入Hold阶段之前或者Hold阶段的前期哦

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:mash和single loop结构的sigma-deta调制器的噪声整形特性

下一篇:请教各位大牛 全差分一级放大零极点! 附电路图-频率响应