CML高速输出缓冲电路问题

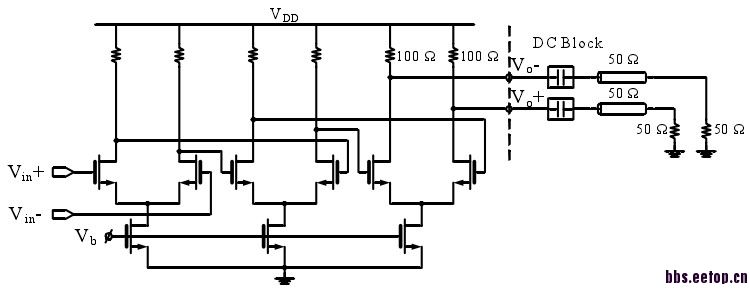

如图所示为论文中看到的缓冲电路

我自己的电路图中Vin+约为1.8v,Vin-约为1.3v,Vb为650mv,

因为最后一级负载电阻为100欧,为了保证摆幅,最后一级尾电流源管栅宽达到400u。

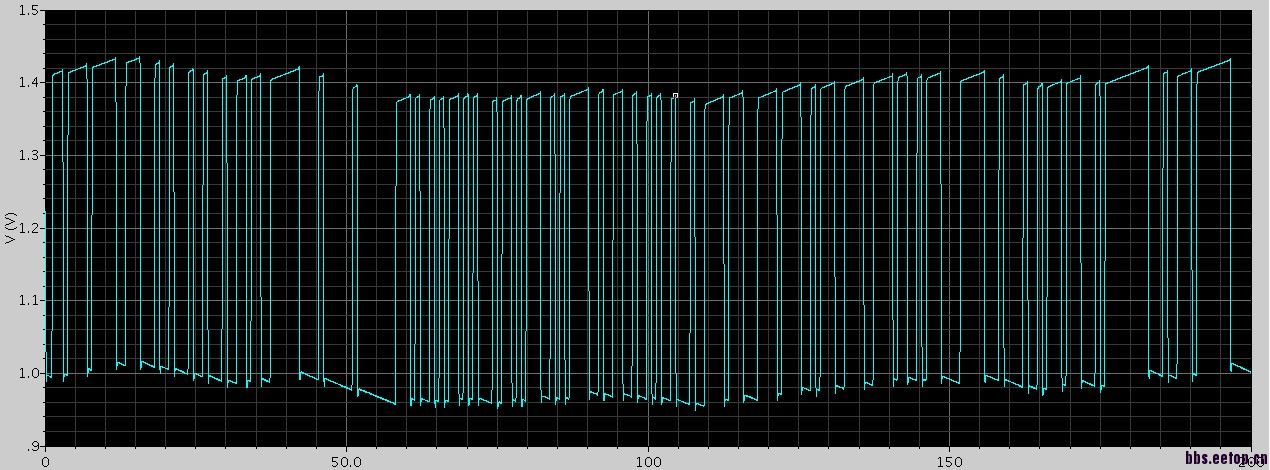

放在整体环路中仿真后,发现输出Vo+和Vo-都是斜的,如下图

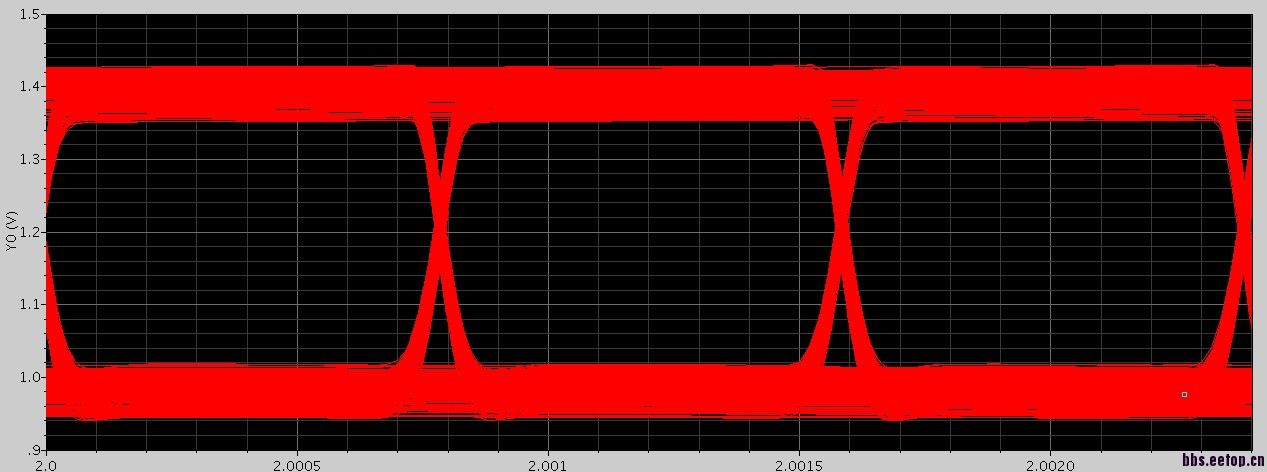

最后观察眼图的情况是

请各位大侠指点指点,谢谢!

看看 .

你的耦合Cap多大?

这是充电引起

请问你眼图是怎么仿真的?

我仿真用的800p,输出缓冲外接大电容小电阻,其他同学说是大概几百p的样子,试了感觉差不多。

用calculator里的eyediagram看的。

800pF是指DC—Block电容吗?如果是,换个80nF看看有什么不同,--看仿真适当初始化后或者跑较长时间使电容充电稳定后的情况。

是的,我按你说的试试吧,谢谢!

单端高频负载 100 并 100 等于50

单端低频负载 100

所以电流Step来时,输出电压先按50欧姆step,后面给足够时间,会增大到100欧姆负载的幅度

从传输函数看,先是零点引起的阶越,然后是极点的缓慢充放电

所以电容越大,你所说的信号斜的程度越低

你的时钟是多少的?图上看不清!

根据不同的时钟选择不同范围的Cap

一般几pF到几nF的范围

是不是带宽不够?电容负载这么大,这个不是有RC决定的么

谢谢麦蒂指导!

我的时钟是1.25Ghz,图中的眼图是用这个时钟的鉴相器里恢复出来的数据。

电阻值是确定的,电容值听说大概这个范围,然后自己瞎调了仿真的。

Cap要变小!

100p~200pF范围应该够了

这个结论怎么来的? 电容越小不是越斜吗..

还是我分析错了..

被忽悠了。

电容值80nF的话效果确实好多了,几乎完全平直了。

这是看的论文里面的,说负载阻抗过低会使得驱动十分困难,作为折中将负载电阻设为100欧,虽然会有一定发射,但驱动会变得容易一些。

你的时装1.25G,电容需要80nF?

也太大了点

电容太大 耦合作用就降低了。要是电容值适合带宽

恩,80n确实太大了,不过几百p的时候确实不太理想

我自己的仿真效果是200pF at 1.25G 应该没有什么斜坡了,很平滑。你的在800pF还有在这么明显的 不知道什么原因,奇怪

你的差分 幅度也不是很大 0.5V左右 ,照理应该很平滑的

请问你这个理论分析的出处?

自己分析的..

请问版版这个有问题吗?

“先是零点引起的阶越,然后是极点的缓慢充放电”

你用零极点能分析出这个来?你依据是什么啊?

计算电容前面out点的阻抗传输函数

(1+sRC)/(1+2*sRC)

你可以用matlab看一下它的阶越响应(电流阶越)

开始直接跳到0.5*Vstep是因为零点,后面逐渐上升到1*Vstep是因为极点(上升的时间常数是2RC)

高论?!

看起来电容耦合好像还很难理解。现在了解为何有些标准会给出耦合电容选择范围,就怕某些想象严重损害系统性能。DP 要求70n~200nF.

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。