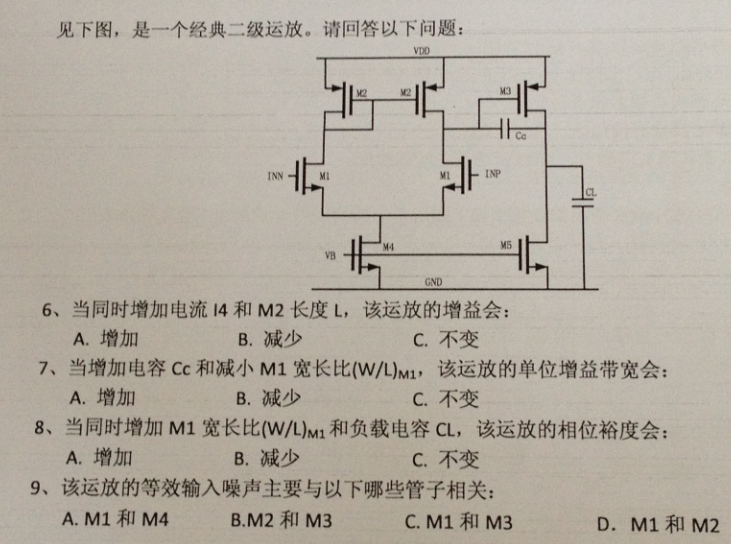

试问公司笔试一道运放题

知道的人 麻烦解答下 非常感谢!

BBBD

可否简单说明下 谢谢

第一题还要看ro1 ro2的比值和电路参数的变化幅度啊。

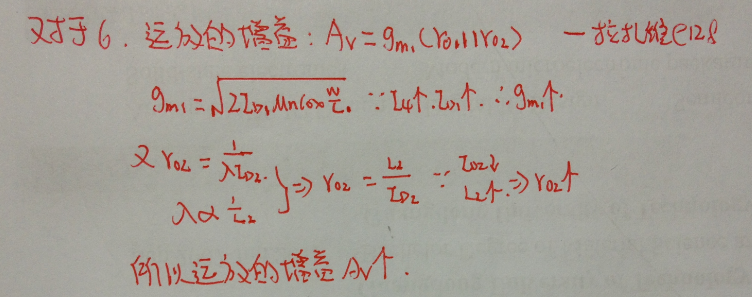

第一题 我觉得选A 增大论述如下

典型情况下Av会变小

你忽略了ro1,增大电流,ro1减小,两个电阻并联,阻抗小于其中的任何一个值,所以增大电流,第一级的输出阻抗减小。

能否详细说明下 谢谢

是的 你说的没错 我搞错了 ro2也不一定是变大了的那应该怎样分析

如果ro2>>ro1,阻抗取决于ro1,增大电流,增益下降,如果ro1>>ro2,阻抗取决于ro2,ro2~VeL/Id,我觉着不好说了

第一题出的有点问题。出题人不严谨。

这些问题的答案可以是多选,估计出题的人也没想那么多。

第8题为啥选B,我看着像选A.......在下菜鸟

第八题,W/L增加,第一输出极点减小,CL增大,第二输出极点减小。要看两者减小的幅度。如果CL减小很多,那么单极点系统就变成双极点系统(带宽内),相位就差。但是,其实主极点也在相应减小。难说!?

第八题, Increase (W1/L1) --> gm increase, And GBW=gm/Cc increase too. When CL is bigger, 2nd pole is lower. Therefore, phase margin is getting lower.

第一题:如果假设此放大器更关注噪声,为了Noise,输入管尺寸都是做的比镜子大的,假设L相同,Id也必然相同,则小尺寸PMOS必然比大尺寸NMOS的ro要大的多,因此提高镜子的L对第一级输出阻抗的提升意义不大,因为主要由输入管NMOS决定。然而Id的上升在优化了noise的同时必然损失了gain,这是不难理解的。所以B是最合理的答案。

可能直观上大家更愿意通过沟道调制理解。但是很不幸的是,在short channel及以后,长度和输出AC阻抗之间的关系急剧减弱,还不如通过commen sense,也就是系统噪声的角度来看这个问题:

如果不理解为何本级noise和本级gain trade off, 可以思考一下Friis方程。Ftot=F1 + F2-1/A1 + F3-1/A1A2 +... 如果随随便便本级的noise和gain都能同时增加,而且---!还只线性的烧功耗,带宽还变大! 那就不需要那么多模拟工程师整天作死了。

Have fun 说的不一定对

Justin

楼上搞射频的吧?

just。

更准确点说,被射频搞。

做射频经常用最小尺寸,但是做模拟一般都是3Lmin,这个时候再增加L应该意义不如从1Lmin到3Lmin那么显著了。想想也是,IC Design哪是这么简答几道题就可以考察的,此题纯属娱乐。

做High Speed 也不定用最小尺寸。纯analog的一般L还是很大的,看情况需求,基本上都用IO device。

第八题,不要考虑GM了吧,带宽也是变的,就从1/RC上考虑,M1W/L增加,第一级的ro是减小的,AvCc不变,主极点增大,CL增大,次级点减小,两极点靠近,PM变小

哪个公司?

请问 增加(W/L)M1 ro1如何增加了? ro1只与流过M1的电流和M1的L有关呀。

无语了!这家公司难道都在做判断题?设计一个运放就是尝试调调管子啊?哎,反向思维害死人啊

就第九题还可以,

其他都是垃圾题

第一题,A,Id增加,会增加gm,

L增加,则增加Ro

Gain正比于gm.Ro

第二题,B

BW正比于gm/Cc

第三题,B

次极点频率变低,带宽增加,PM减小

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。