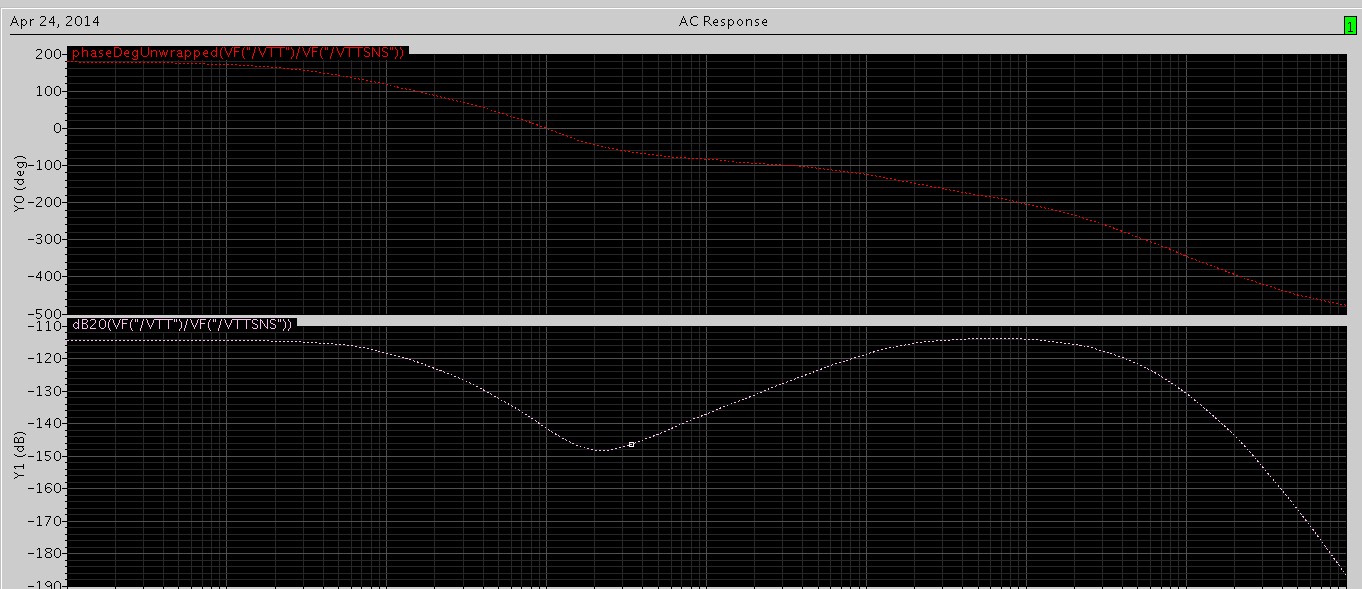

LDO负载电流为3A时,交流仿真为什么是这样?如何改进

录入:edatop.com 阅读:

增益怎么变成这样,怎么从负的开始,如何分析,电路改怎么改进

增益怎么变成这样,怎么从负的开始,如何分析,电路改怎么改进

Hi Apenper:

If the output cap has a ESR, the LDO is 2 pole and 1 zero system.

At the heavy load, one pole is higher than the zero and other is

closed to low frequency the result is like your picture.

If your compensation is based on an external element (Cout + ESR),

I suggest the zero is in the LDO.

mpig

是负载电流过大,LDO已经进入by-pass状态了么

谢谢 正如上面所说负载电流过大 问题已经解决

请问什么是bypass状态呢,是指管子进入线性区么?

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:HFSS求助,各位给个解答吧,谢谢。

下一篇:ADC流片测试发现有部分偶次谐波较大