芯片没有 vdd ground 是如何设计 ?

录入:edatop.com 阅读:

芯片没有 vdd ground 是如何设计 ?

有看过一些卖的 chip ,

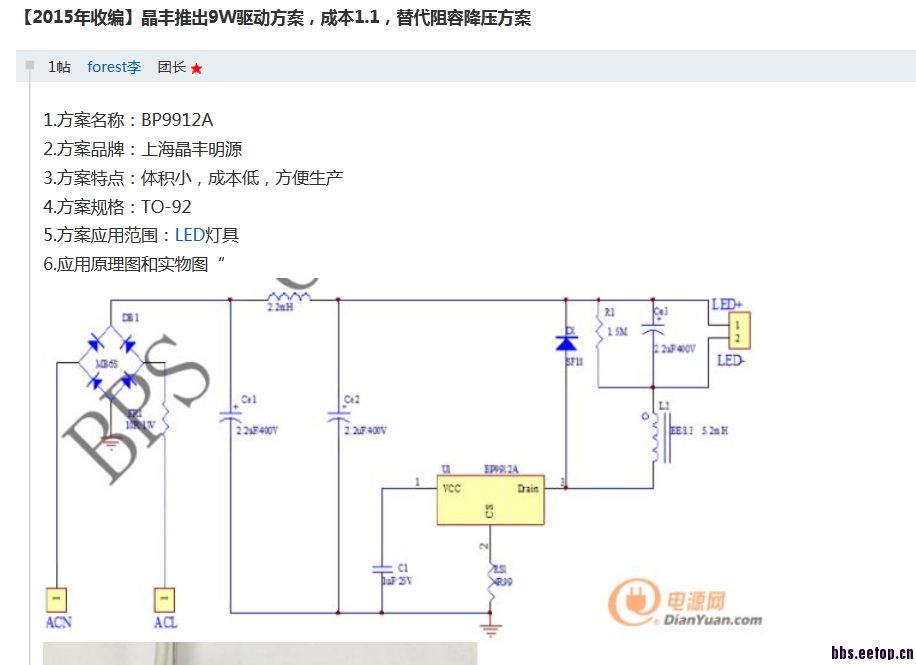

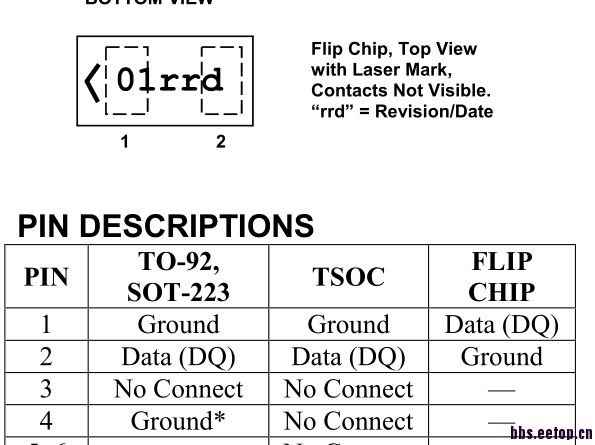

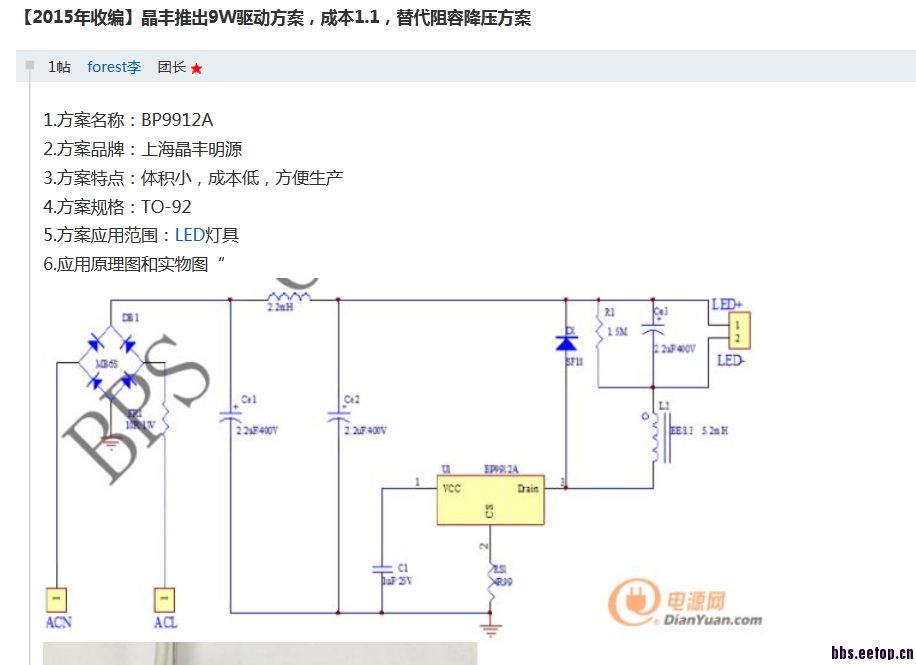

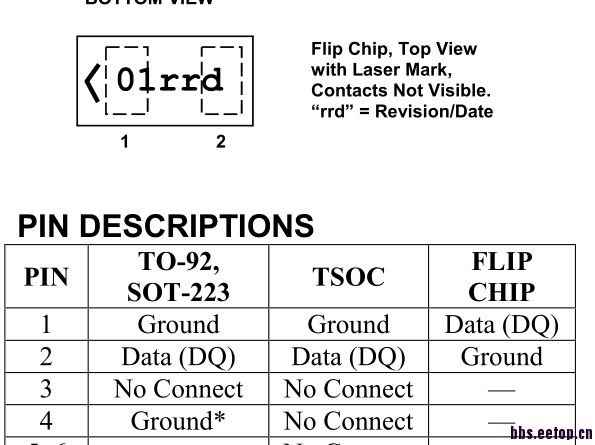

datasheet 如这边 .

http://bbs.eetop.cn/viewthread.php?tid=486310&pid=8570916&page=1&extra=page%3D1#pid8570916

但是不是没有 vdd

就是 没有 ground

这要如何设计 ?

这方式可以吗? 不过就我知道一般 UHV EDMOS 好像都很大一块做成

racetank (finger) type ..

有看过一些卖的 chip ,

datasheet 如这边 .

http://bbs.eetop.cn/viewthread.php?tid=486310&pid=8570916&page=1&extra=page%3D1#pid8570916

但是不是没有 vdd

就是 没有 ground

这要如何设计 ?

只有有个基准参考点就成就成!其实是有GND和VDD

drain 里面有花样

不知道是如何設計? 那 current sense 不能對地 .

电流信号的嘛

不懂?

有 paper ?

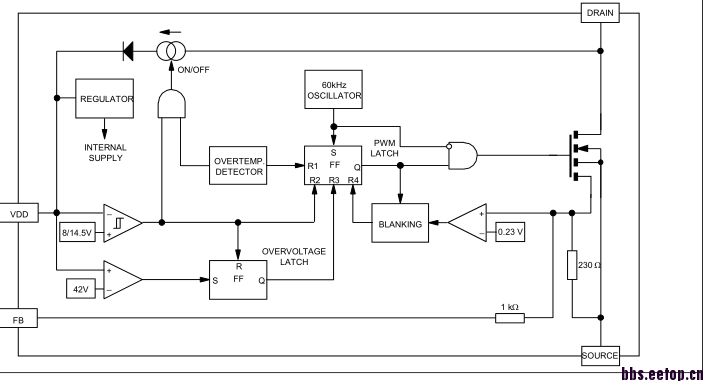

给你看个图吧

其实不是没有地,是内部地和外部地的区别。接在电阻上面的CS应该是内部地,当电流CS输出的电流变大,会把内部地电位相对VCC抬升,相对的Drain的内部控制电压也变化了。

地只是相对的参考,我把这个符号画在哪里都没有关系,我甚至可以画在电源上,那么原来的0电位就变成了-vdd

所以内部 current sense 点其实是 vcc? 外接大电容

如可以省去GROUND , 一般CHIP 为何不如此 设计 ? 应该有其他不好地方吧

因为是浮地,噪声比较大,不适合传输小信号。优点是在长距离(数百米)传输时抗衰减,双线式的连接也可以节约成本(数百米的线,少一根芯少不少钱呢),双绞线的EMC特性比较好,所以一般用于传输数字信号。

第一个图里的CS应该是芯片内部的GND

YES

数百米的线 ?

现在不是讨论 芯片内

我说的是应用时的情况。

viper12

Source = chip internal Gnd

这方式可以吗? 不过就我知道一般 UHV EDMOS 好像都很大一块做成

racetank (finger) type ..

基本上就是这个意思。

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。