多晶硅电阻的第三端(衬底),该接VDD还是GND啊?

录入:edatop.com 阅读:

制造不同的N型或者P型多晶硅电阻对衬底有要求吗?

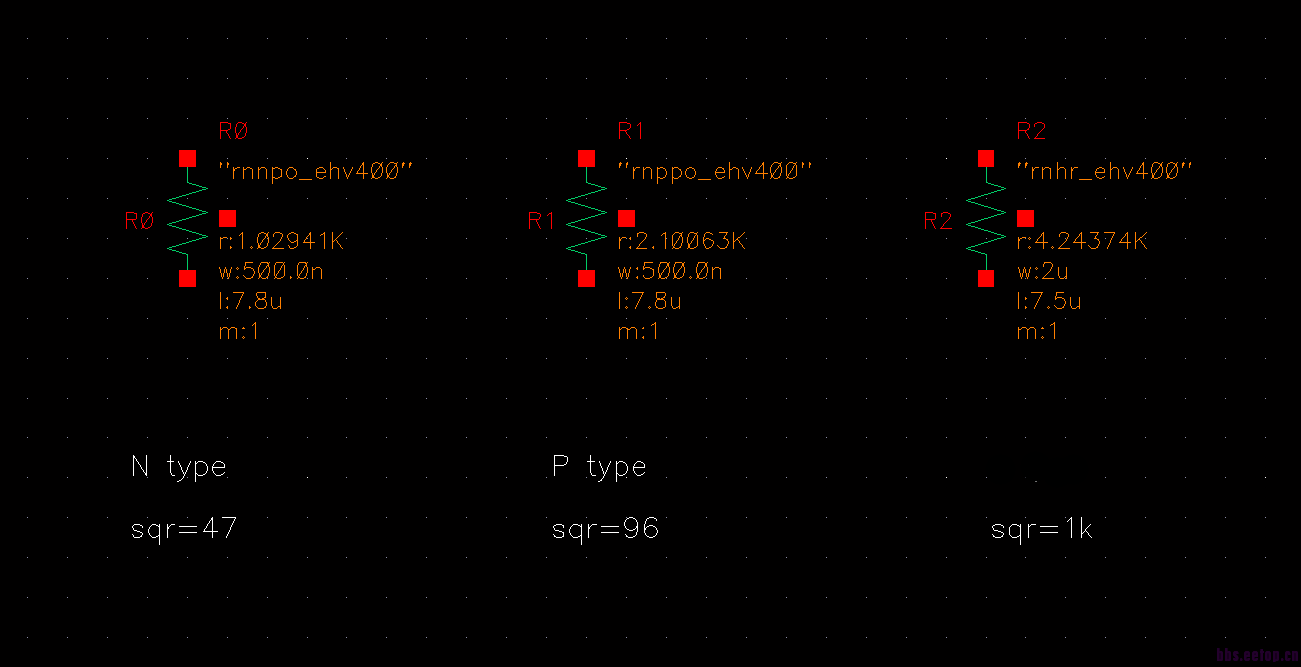

下面分别是n型poly电阻,p型poly电阻,HR电阻,请问衬底的原理是什么啊,谢谢!

看版图电阻外圈是p+ imp还是n+ imp?

poly电阻要考虑衬底?。

你是做多大速率的电路,要把电阻网络和衬底之间的耦合电容要考虑进去?

普通的标准CMOS 0.5um工艺

一般默认接独立干净的高电位

没有特殊要求就不用考虑了。仿真起来影响也不大。

要噪声隔离的话,包nwell接gnd,

没有特殊要求的话,直接放substrate上接gnd

你说的是版图上的。小编还在搭电路。

那就是寄生的cap了对谁的问题了,

问题解决了,谢谢大家

一般,信号参考VDD就结VDD,信号对地就接地。如果要求不高,就随便接。

你的解释正确

我的天,这就解决了?没有人仿真过?就tsmcN28工艺而言,n掺和p掺的电阻接不同电位阻值的影响在40%左右。

我最近在做带隙基准,电路仿真时候,电阻的点三端悬空,可以得出很理想的温度系数,当有链接时候,相差太多!需要修改吗?版图第三端需要链接吗?心好累啊

你用的什么电阻?

P+diff,我想了一下,画版图时候点三端就是衬底,电路图可以悬空

我想问一下多晶硅是可以作为电阻的,吗、那么不同掺杂对其阻值会有影响吗?N掺杂和P掺杂对阻值的影响的原理是什么?是由于其内部的载流子不同吗?

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。