- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

Silicon Labs推出简化相干光线卡,降低系统成本和复杂度

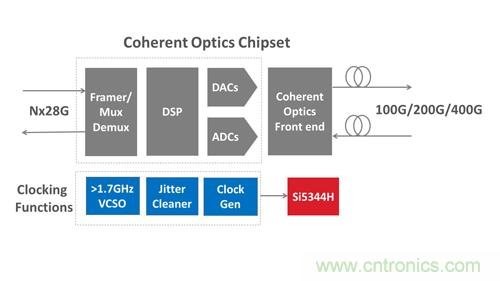

Silicon Labs新型Si534xH相干光时钟可以为数据转换器提供低抖动参考定时,可替代依赖于昂贵、大封装尺寸的压控SAW振荡器(VCSO)的分立定时解决方案。与仅支持单一固定频率的VCSO不同,新型Si534xH时钟提供很宽的频率范围,支持频率高达2.7GHz,且无需改变物料清单(BOM)元器件。

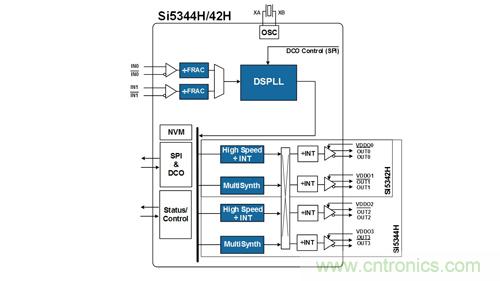

Si5344H和Si5342H时钟提供最佳的频率灵活性和无与伦比的50fs RMS抖动性能。这些时钟芯片简化了器件采购过程,可采用交货时间短至两周的单个时钟IC解决方案,来替代多个需定制的、较长交货时间的VCSO。凭借抖动衰减PLL、高频率输出驱动器、分数频率合成和数字控制振荡器(DCO)技术,Si534xH系列产品为相干光收发器应用提供所需的全部时钟功能,与竞争对手解决方案相比降低了40%的占用面积及40%的功耗。

通信市场中最大增长驱动因素之一是业内城域网络和数据中心互联(DCI)领域从10G到100G的转变。相干光学技术可用于100G和400G应用,因为它使得服务提供商能够通过现有的光纤发送更多的数据,减少为带宽扩展而进行网络升级的成本和复杂性。当前用于相干光的定时解决方案在成本和尺寸方面还未达到最优化,需要VCSO、时钟发生器和分立器件的多样化组合。

Silicon Labs的Si534xH时钟是专门用于满足100G/400G相干光应用对于定时的要求。除了支持光收发数据转换器中定时所需的超高频合成,Si534xH时钟还整合了Silicon Labs经过市场验证的DSPLL®抖动衰减技术和MultiSynth低抖动分数频率合成技术,从而提供了巧妙的、易于使用的单芯片解决方案。所有100G/400G发射器或接收器时钟都可以由单个芯片生成,通过消除大量分立器件,将BOM成本降至最低并降低了复杂度。

Silicon Labs定时产品高级营销总监James Wilson表示:“为了满足日益增加的带宽需求,运营商需要100G/400G相干设计,从而获得比传统方案更高的线卡端口密度和更低的位成本。Silicon Labs的Si534xH时钟产品与传统基于VCSO的解决方案相比,具有显著减小的占用面积和更低的功耗等优势,它能够为相干光应用提供所需的高频率时钟合成、抖动衰减和严格的相位噪声。”

Silicon Labs的ClockBuilderProTM支持相干时钟开发,它是一款能够简化时钟树设计、设备配置和评估细节性能的易用型软件工具。该工具能够独立生成芯片配置文件或者直接控制评估板上的Si534xH芯片。ClockBuilder Pro也能够用于创建Silicon Labs抖动衰减器和时钟发生器的工厂定制版本,从而满足每个客户独特的计时要求。

Si534xH相干光时钟产品特性:

用于发射器和接收器时钟的超高性能抖动衰减PLL;

用于最大2.7GHz数据转换器时钟的高速驱动器,且具有超低相位噪声;

典型50fs RMS(1MHz至40MHz)抖动性能;

MultiSynth分数频率合成,可生成最大712.5MHz的任意频率;

集成环路滤波器和用户可编程PLL带宽,实现灵活的抖动衰减;

高速、数字可调的DCO模式:0.001ppb分辨率,1MHz SPI更新速率;

适合模组化的尺寸和功耗;

简单易用的ClockBuilder Pro软件;

价格及供货:

Si5344H和Si5342H相干光时钟样片现已供货,采用7mm×7mm 44QFN封装,计划于5月量产。当采购量在一万片时的单价为27美元起。标准和定制的芯片可在短期内交货(样片需两周时间,量产订单需四周时间),这简化了原型设计和量产阶段的采购。为了简化芯片评估和系统级定时设计,Silicon Labs还提供Si5344H-EVB和Si5342H-EVB评估板,价格均为199美元。